一种全双工射频自干扰的消除方法

1.本发明属于全双工通信技术领域,尤其设计一种分数时延技术辅助射频干扰的消除方法。

背景技术:

2.同频同时全双工通信可以扩大两倍频谱效率,节约频谱资源,提高用户传输速率,然而这一过程中,单用户的接收天线在接收对方发射的信号同时,也会接收到来自自身发射天线的同频率信号,产生自干扰,降低了接收信号的信干噪比,进而影响通信速率。目前,现有技术主要在功放后级引出一路参考信号,搭建多抽头干扰消除链路的方式来实现全双工干扰消除。然而,由于多抽头链路的每个抽头的时延固定,并且抽头的数量增加会严重加剧控制算法的复杂度,将导致消干扰效果不明显或者不能有效适应周围通信环境的改变。固定抽头将无法对齐每径干扰的基带信号部分,抽头数量限制将遏制其干扰消除效果。综上所述,现有同频同时全双工射频干扰消除技术存在未能解决多径环境下的多径信号基带对齐的问题,以及抽头数量限制带来的不理想消除效果的缺陷。

技术实现要素:

3.为了解决干扰信号对齐问题和抽头数量增加带来的硬件复杂度的问题,本发明提供了一种基于分数时延技术的全双工射频自干扰的消除方法,能够实现基带信号高精度对齐,同时又能很好的解决抽头增加带来的额外硬件复杂度。

4.本发明的技术解决方案是:

5.一种全双工射频自干扰的消除方法,其步骤如下:

6.1)在数字域实现分数时延滤波器,此滤波器由多个n阶fir滤波器构成,其中滤波器系数是h(n),假设滤波器的输入信号为x(l),那么通过滤波器输出信号为

[0007][0008]

其中,d为分数时延值;

[0009]

2)将上述分数时延滤波器的抽头系数值定义为

[0010][0011]

其中,表示第n个可变抽头系数,从而获得输出信号为

[0012][0013]

2)在上述分数时延滤波器后级增加一个q阶fir数字滤波器,此滤波器的系数为a(q),其傅里叶变换为h

csi

(f);a(q)=fft(h

csi

(f)),将分数时延滤波器的信号变频到射频域,在射频域完成消除射频自干扰。

[0014]

进一步,在射频域设置一个衰减器和合路器,衰减器用于调整信号幅值,合路器用于将信号与射频端接收自干扰信号混合。

[0015]

进一步,分数时延滤波器的系数h(n)采用拉格朗日、sinc函数,即h

id

(f)=e-2πdf

。

[0016]

进一步,在合路器之前增加一个低噪声放大器。

[0017]

本发明通过数字域实现了一个分数时延滤波器,用于对齐自干扰信号,利用分数时延的高精度分数时延和灵活可调节的优点,可以在全双工射频消干扰领域构造出每径的自干扰信号,本发明能以很低的硬件成本实现复杂多径环境的干扰消除。增加一个fir数字滤波器用于模拟自干扰信道,便于重构自干扰信号,最终在射频域实现全双工自干扰抵消。

[0018]

本发明提出的方法与现有技术相比的优点在于:

[0019]

1)提出了分数时延滤波器与全双工射频消干扰结合起来,可以起到对齐自干扰信号在空中传播的时延,并且有较高的精度和更灵活的时延变换。

[0020]

2)在数字域实现干扰信号的重构,相比于传统多抽头方案更加有利于节省硬件资源,可以便捷地提高fir滤波器的阶数来降低重构信号的失真。同时提出头失真问题解决办法,有效抑制头失真。

[0021]

3)最终干扰信号抵消是在射频域完成,这有利于将干扰信号在adc采样前抑制到一个较低水平,以避免adc比特位饱和。

附图说明

[0022]

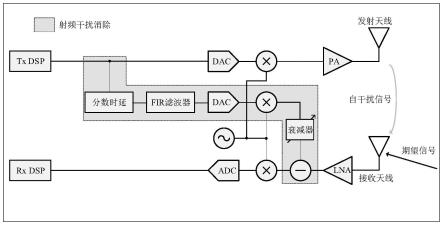

图1为本发明的结构框图;

[0023]

图2为分数时延滤波器的头失真改善示意图。

具体实施方式

[0024]

下面结合附图,通过实施例进一步描述本发明,但不以任何方式限制本发明的范围。

[0025]

本发明分数时延技术的全双工射频自干扰消除方法,如图1所示。其步骤如下:

[0026]

1)在数字域实现farrow结构滤波器,此滤波器由多个n阶子fir滤波器构成,这里以n=11为例,假设滤波器的输入信号为x(l),那么通过滤波器输出信号为

[0027][0028]

其中,d为分数时延值,这里d=5.4为例,分数时延滤波器的系数h(n)可通过各种设计,比如拉格朗日、sinc函数等,来逼近理想时延全通滤波器频域响应,即h

id

(f)=e-2πdf

。这里的h

id

(f)是系数h(f)的频率响应逼近的理想曲线。

[0029]

2)考虑fir滤波器的头失真问题,这是fir滤波器的普遍问题。当输入序列索引小于滤波器的阶数时,由于输入信号未能把滤波器所有抽头利用填满而使得输出信号产生失真。为了解决这个问题,改写滤波器的抽头系数值为这里从而获得输出信号为

[0030]

[0031]

具体来说,对于整个信号做滤波器,采用可变抽头形式如下

[0032][0033]

这里表示第n个可变抽头系数。

[0034]

以lagrange分数时延滤波器为例,lagrange方法是分数时延滤波器的一种方法,在数字域实现此滤波器,其滤波器系数为

[0035][0036]

根据lagrange分数时延滤波器的系数值,利用本发明提出的改进头失真的方法,设置分数时延滤波器的抽头系数值为

[0037][0038]

在matlab仿真软件中对本发明的分数时延滤波器进行仿真分析。由于设计中的数字部分误差包含分数时延滤波器的失真和dac的比特位失真,因而仿真部分引入这两部分失真。

[0039]

在matlab仿真分析时,使用dac的量化精度12位,即最小精度设计lagrange分数时延滤波器时,取n=11,即11阶滤波器。如图2所示,表示输入理想信号,x(l)为此信号的采样,y

sinc

(l)和y

aim

(l)分别表示输出具有头失真的信号和头失真改善信号,可以观察出本发明在头部信号拥有较大的失真改善作用。

[0040]

3)在分数时延滤波器后级设计一个q阶fir数字滤波器,此滤波器的系数为a(q),其傅里叶变换为h

csi

(f),这个fir滤波器的系数由信道估计参数决定。

[0041]

a(q)=fft(h

csi

(f))

[0042]

由此fir滤波器滤波的基带信号上变频到射频域,在射频域选用射频衰减器和射频合路器,利用衰减器调整信号幅值,可以控制信号强度,利用合路器与接收自干扰信号叠加,将信号通过合路器与射频端接收自干扰信号混合,完成射频消干扰的整体目的。

[0043]

本发明在合路器之前可以增加一个低噪声放大器,以便于将干扰信号提升一个水平,这样有利于后级干扰消除获得更好的效果。值得注意的是,这里的低噪声放大器放大自干扰的同时也会放大远端的期望信号,不会降低信干比。

[0044]

需要注意的是,公布实施例的目的在于帮助进一步理解本发明,但是本领域的技术人员可以理解:在不脱离本发明及所附权利要求的精神和范围内,各种替换和修改都是可能的。因此,本发明不应局限于实施例所公开的内容,本发明要求保护的范围以权利要求书界定的范围为准。本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1