一种编码变换系统、编码方法及存储介质、电子设备与流程

1.本发明涉及图像处理技术领域,尤其涉及一种编码变换系统、编码方法及存储介质、电子设备。

背景技术:

2.在2020年7月,国际视频编码标准(versatile video coding,vvc)由itu-tvceg和iso/iec mpeg联合组成的jvet(joint video exploration team)委员会完成制定。vvc在编码效率上相比前一代视频编码标准,即高效视频编码(high efficiency video coding,hevc)提高了大约一倍,与此同时其计算复杂度也大幅度提高。变换是vvc的一个重要过程,其将残差数据从像素域转化为频率域从而能够去除变换域上的冗余信息,在编码过程中使用频率高、计算复杂度大。在已有的方案中,在hevc的研究成果中,使用multiple constant multiplication(多重常用乘法,mcm)实现的变换结构会相比于使用通用乘法器实现的变换结构具有更小的硬件实现面积和功耗。但是随着vvc中对于变换类型和变换尺寸的增加,基于mcm结构实现的变换将会增加大量的移位与加法单元(saus),从而大幅度增大硬件实现面积。并且,基于mcm方法设计的saus在进行小块计算时只会用到相应的小块saus,而用于大块计算的saus会处于闲置状态,并不能高效地利用资源进行计算。另外,现有的方案大多基于dct-ii变换类型具有的蝶形运算特性进行实现,虽然可以降低运算的次数,但是在流水设计中会要求一维变换内部达到64个并行度,这样的设计虽然在基于mcm方法实现的结构中减少了一定的面积,但本质上还是会造成很大程度上的资源空闲。

技术实现要素:

3.为解决上述技术问题,本发明实施例期望提供一种编码变换系统、一种编码方法、一种存储介质、一种电子设备,以至少解决由于现有技术中存在的问题。

4.在第一方面,本发明实施例提供一种编码变换系统,包括:

5.计算模块,用于利用确定的变换系数与待处理数据进行相乘运算得到第一运算结果;其中,所述变换系数通过各变换核对待处理数据进行码位估计确定;所述计算模块包括若干个乘法单元,各所述乘法单元包括若干个通用乘法器;

6.累加器,用于对所述第一运算结果进行求和运算,以获取编码结果。

7.进一步地,本发明实施例提供一种编码方法,包括:

8.获取待处理数据,对所述待处理数据进行码位估计以确定对应的变换矩阵;

9.根据所述变换矩阵对应的变换类型和变换尺寸获取对应的变换系数;

10.利用计算模块对所述变换系数、所述待处理数据进行相乘运获取第一结果;其中,所述计算模块包括若干个乘法单元,各所述乘法单元包括若干个通用乘法器;

11.利用累加器对第一结果进行求和运算,以获取编码结果。

12.进一步地,本发明实施例提供一种存储介质,其上存储有计算机程序,所述程序被处理器执行时实现如上述实施例所述的编码方法。

13.进一步地,本发明实施例提供一种存储介质,电子设备,包括:处理器;以及存储器,用于存储所述处理器的可执行指令;其中,所述处理器配置为经由执行所述可执行指令来执行如上述实施例所述的编码方法。

14.本发明实施例提供了一种编码变换系统、编码方法,基于统一的通用乘法器实现vvc二维变换,通过在计算模块中设计若干个乘法单元,并在各乘法单元布局相同数量的乘法器,能够实现支持vvc中的dct-ii、dct-vii、dct-viii变换类型以及所有大小的变换尺寸;且不同的变换类型和变换尺寸都可以共用一个由通用乘法器构成的计算模块来实现,大大提高了资源的利用率。

附图说明

15.此处所说明的附图用来提供对本发明的进一步理解,构成本技术的一部分,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中:

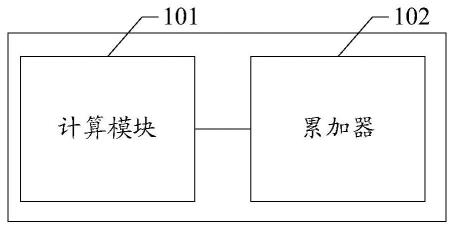

16.图1为本发明实施例提供的一种编码变换系统的组成示意图;

17.图2为本发明实施例提供的一种编码变换系统的组成示意图;

18.图3为本发明实施例提供的dct-ii4与dct-ii8变换矩阵的示意图;

19.图4为本发明实施例提供的dct-vii4与dct-viii4变换矩阵的转换关系的示意图;

20.图5为本发明实施例提供的通用乘法单元结构的示意图;

21.图6为本发明实施例提供的累加器结构的示意图;

22.图7为本发明实施例提供的一种编码方法的示意图;

23.图8为本发明实施例提供的一种程序产品的示意图;

24.图9为本发明实施例提供的一种电子设备的示意图。

具体实施方式

25.为了使本技术领域的人员更好地理解本发明方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分的实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

26.本发明实施例提供一种编码变换系统。参考图1所示,编码变换系统可以包括:计算模块101和累加器102。其中,计算模块101可以利用确定的变换系数与待处理数据进行相乘运算得到第一运算结果;其中,所述变换系数通过各变换核对待处理数据进行码位估计确定;所述计算模块包括若干个乘法单元,各所述乘法单元包括若干个通用乘法器。累加器102可以用于对所述第一运算结果进行求和运算,以获取编码结果。

27.在本技术实施例中,计算模块可以包括32个乘法单元;各所述乘法单元包括16个通用乘法器。

28.在本技术实施例中,所述系统还包括:内部寄存器105,用于存储不同类型的变换矩阵。

29.在本技术实施例中,dct-ii中的各尺寸的变换矩阵偶数行偶对称,奇数行奇对称;dct-vii和dct-viii中各尺寸的变换矩阵偶数行反序,奇数行反序且反号。

30.举例来说,在本发明提出的变换结构里,不同类型的变换矩阵存储在内部寄存器中。可以根据输入的变换类型与变换尺寸选择出相应的变换系数。对于变换核来说,dct-ii变换核中大小为4和8的两个变换矩阵如图3所示,其中,偶数行偶对称,奇数行奇对称;首行是第0行;并且,4

×

4的变换矩阵是由8

×

8矩阵的偶数行的前一半元素组成的。这两个特点也同样存在于其他尺寸的变换矩阵中。dct-vii变换核和dct-viii变换核没有与dct-ii变换核相同的蝶形特性。

31.dct-vii变换核和dct-viii变换核的变换矩阵具有非常明显的相似性,两者的变换矩阵在数值上具有偶数行反序,奇数行反序且反号的特点;首行是第0行。图4展示了大小为4的两个变换矩阵之间的关系,这样的特性同样存在于其他大小的变换矩阵中。

32.因此,dct-ii变换核的所有系数矩阵可由64

×

64的系数矩阵推演,dct-viii变换核的系数矩阵可由同尺寸dct-vii变换核系数矩阵推演,仅需存储dct-ii变换核中64

×

64的块系数与dct-vii变换核中全尺寸的块系数即可满足vvc中所有类型的变换。

33.在本技术实施例中,在计算模块中,选择出的变换核的矩阵系数将通过32组乘法单元与16个输入的变换核数据相乘,各乘法单元每组有16个通用乘法器。

34.乘法单元的数目取决于最大的变换核进入时所需的乘法单元个数,而vvc在dct-ii中大小为64的变换块拥有高频置零的特性,不需要计算出后32个变换系数与输入数据相乘的结果,这可以减少一半的乘法结构数目,仅需要32个通用乘法单元与少量控制逻辑即可实现一维变换。

35.单个通用乘法单元如图5所示,16个输入数据与16个变换系数分别相乘,根据不同的变换尺寸选择输出。当变换尺寸为64、32、16时,单个变换单元的输出为16个乘积项之和,当变换尺寸为8时,单个变换单元的输出为两组8个乘积项之和,当变换尺寸为4时,单个变换单元的输出为四组4个乘积项之和。

36.在本技术实施例中,参考图6所示的累加器;变换尺寸为16、8、4的块在一个时钟后即可输出完整的乘积和结果,而变换尺寸为64、32的块需分别经过四个、两个时钟的累加才能输出完整的乘积和结果。

37.在本技术实施例中,参考图2所示,所述系统还包括:并转串模块103,用于对变换尺寸后的编码结果延迟输出。

38.在本技术实施例中,参考图2所示,所述系统还包括:系数缩放模块104,用于使所述变换系数保持在预设标准。

39.具体的,为了保持系统并行度为16,在累加器后加入了并转串模块,所有变换尺寸的结果都将延迟4个时钟后流水输出,再经系数缩放模块使变换系数保持在16位以内。

40.在本技术实施例中,还提供了一种编码方法。如图7所示,本技术实施例提供的编码方法包括:

41.步骤s11,获取待处理数据,对所述待处理数据进行码位估计以确定对应的变换矩阵;

42.步骤s12,;根据所述变换矩阵对应的变换类型和变换尺寸获取对应的变换系数

43.步骤s13,利用计算模块对所述变换系数、所述待处理数据进行相乘运获取第一结果;其中,所述计算模块包括若干个乘法单元,各所述乘法单元包括若干个通用乘法器;

44.步骤s14,利用累加器对第一结果进行求和运算,以获取编码结果。

45.在本技术实施例中,所述方法还包括:基于所述变换类型和变换尺寸向内部寄存器中提取所述变换矩阵对应的所述变换系数。

46.具体来说,上述的编码方法可以应用于上述的编码变换系统。其中,上述的待处理数据可以是视频中的连续的帧图像。对于各图像,可以首先利用各变换核进行码位估计,利用各类型变换核对应的各尺寸的变换矩阵对图像进行搜索,从而根据计算结果确定当前帧图像对应的最优类型的变换核,以及对应的变换矩阵的尺寸。其中,上述的码位估计采用现有技术即可实现,本发明对该过程不再赘述。

47.在确定变换类型、变换尺寸后,可以向预设的内部寄存器中提取对应的变换矩阵,及对应的变换系数。举例来说,可以预先计算各类型、各尺寸的变换矩阵的变换系数,并保存在内部寄存器中,以便于编码器快速获取变换系数。

48.在获取变换系数后,便可以在计算模块中利用变换系数与待处理数据进行运算。得到第一运算结果,并输入至累加器中。具体而言,对于单个通用乘法,16个输入数据与16个变换系数分别相乘,根据不同的变换尺寸选择输出。当变换尺寸为64、32、16时,单个变换单元的输出为16个乘积项之和,当变换尺寸为8时,单个变换单元的输出为两组8个乘积项之和,当变换尺寸为4时,单个变换单元的输出为四组4个乘积项之和。

49.累加器对计算模块输入的第一结果进行求和运算,从而得到编码结果。具体的,变换尺寸为16、8、4的块在一个时钟后即可输出完整的乘积和结果,而变换尺寸为64、32的块需分别经过四个、两个时钟的累加才能输出完整的乘积和结果。

50.之后,还可以将编码结果输入并转串模块中,为了保持系统并行度为16,对所有变换尺寸的结果都将延迟4个时钟后流水输出,再经系数缩放模块使变换系数保持在16位以内。

51.本发明的系统并行度可以实现为16,相比于传统方案需要在一维变换模块的前级加入串转并模块从而将16并行度拼凑到64个并行度以实现蝶形快速算法,本发明无需对输入数据进行拼拍处理,其内部计算模块采用16

×

32个通用乘法器,根据不同的变换类型和尺寸需要选择送入通用乘法器的变换矩阵与输入数据进行相乘,并将结果送入到累加器中进行求和。本发明的结构利用verilog hdl进行实现,并在asic 28nm工艺下使用design compiler进行综合。从实验结果来看,本发明提出的基于统一的通用乘法器实现的vvc二维变换结构可以在面积上比传统方案小30.9%左右。并且,本发明提出的结构在通用性和实现难度上都优于传统方案,这样的结构在实现多种视频编码标准上也更具备优势。

52.应当注意,尽管在上文详细描述中提及了用于动作执行的设备的若干模块或者单元,但是这种划分并非强制性的。实际上,根据本公开的实施方式,上文描述的两个或更多模块或者单元的特征和功能可以在一个模块或者单元中具体化。反之,上文描述的一个模块或者单元的特征和功能可以进一步划分为由多个模块或者单元来具体化。

53.进一步地,本发明实施例提供一种计算机可读存储介质,图8为本发明实施例提供的一种计算机可读存储介质的示意图。具体的,其上存储有能够实现本说明书上述方法的程序产品。在一些可能的实施方式中,本发明的各个方面还可以实现为一种程序产品的形式,其包括程序代码,当所述程序产品在终端设备上运行时,所述程序代码用于使所述终端设备执行本说明书上述“示例性方法”部分中描述的根据本发明各种示例性实施方式的步骤。

54.根据本发明的实施方式的用于实现上述方法的程序产品,其可以采用便携式紧凑盘只读存储器(cd-rom)并包括程序代码,并可以在终端设备,例如个人电脑上运行。然而,本发明的程序产品不限于此,在本文件中,可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。

55.所述程序产品可以采用一个或多个可读介质的任意组合。可读介质可以是可读信号介质或者可读存储介质。可读存储介质例如可以为但不限于电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。可读存储介质的更具体的例(非穷举的列表)包括:具有一个或多个导线的电连接、便携式盘、硬盘、随机存取存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(eprom或闪存)、光纤、便携式紧凑盘只读存储器(cd-rom)、光存储器件、磁存储器件、或者上述的任意合适的组合。

56.计算机可读信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了可读程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或上述的任意合适的组合。可读信号介质还可以是可读存储介质以外的任何可读介质,该可读介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。

57.可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于无线、有线、光缆、rf等等,或者上述的任意合适的组合。

58.可以以一种或多种程序设计语言的任意组合来编写用于执行本发明操作的程序代码,所述程序设计语言包括面向对象的程序设计语言—诸如java、c++等,还包括常规的过程式程序设计语言—诸如“c”语言或类似的程序设计语言。程序代码可以完全地在用户计算设备上执行、部分地在用户设备上执行、作为一个独立的软件包执行、部分在用户计算设备上部分在远程计算设备上执行、或者完全在远程计算设备或服务器上执行。在涉及远程计算设备的情形中,远程计算设备可以通过任意种类的网络,包括局域网(lan)或广域网(wan),连接到用户计算设备,或者,可以连接到外部计算设备(例如利用因特网服务提供商来通过因特网连接)。

59.进一步地,本发明实施例提供一种电子设备。图9为本发明实施例提供的一种电子设备的示意图。该电子设备可以用于实现上述的tdm系统可靠性评估。如图9所示,电子设备800以通用计算设备的形式表现。电子设备800的组件可以包括但不限于:上述至少一个处理单元810、上述至少一个存储单元820、连接不同系统组件(包括存储单元820和处理单元810)的总线830、显示单元840。

60.其中,所述存储单元存储有程序代码,所述程序代码可以被所述处理单元810执行,使得所述处理单元810执行本说明书上述"示例性方法"部分中描述的根据本发明各种示例性实施方式的步骤。例如,所述处理单元810可以执行如图7中所示的步骤。

61.存储单元820可以包括易失性存储单元,例如随机存取存储单元(ram)8201和/或高速缓存存储单元8202,还可以进一步包括只读存储单元(rom)8203。

62.存储单元820还可以包括具有一组(至少一个)程序模块8205的程序/实用工具8204,这样的程序模块8205包括但不限于:操作系统、一个或者多个应用程序、其它程序模块以及程序数据,这些示例中的每一个或某种组合中可能包括网络环境的实现。

63.总线830可以包括数据总线、地址总线和控制总线。

64.电子设备800也可以与一个或多个外部设备900(例如键盘、指向设备、蓝牙设备等)通信,这种通信可以通过输入/输出(i/o)接口850进行。电子设备800还包括显示单元840,其连接到输入/输出(i/o)接口850,用于进行显示。并且,电子设备800还可以通过网络适配器860与一个或者多个网络(例如局域网(lan),广域网(wan)和/或公共网络,例如因特网)通信。如图所示,网络适配器860通过总线830与电子设备800的其它模块通信。应当明白,尽管图中未示出,可以结合电子设备800使用其它硬件和/或软件模块,包括但不限于:微代码、设备驱动器、冗余处理单元、外部磁盘驱动阵列、raid系统、磁带驱动器以及数据备份存储系统等。

65.以上所述,仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1