数据通信处理方法及系统与流程

1.本发明涉及一种通信技术领域,特别是涉及一种数据通信处理方法及系统。

背景技术:

2.随着移动通信5g时代的到来,由于对瞬时带宽、调制技术要求的提高,对算法实现难度构成巨大的挑战。同时,对处理资源要求也成倍增加,由此,以数字预失真为核心的下行通道处理算法成为基站核心能力和技术的体现。其中,射频拉远单元rru(remote radio unit)在下行数字通道中集成有越来越复杂的算法,以抑制模拟电路非线性引起的失真、iq不平衡和本振直流分量等,从而进行移动通信。

3.目前,现有大型设备商通常将射频拉远单元rru嵌入至专用集成电路asic(application specific integrated circuit)或可编程器件fpga(field programmable gate array)中,以实现各种算法在硬件电路中的定制化需求。但是,由于在射频拉远单元rru中的下行通道算法通过硬件逻辑单元固化地嵌入至asic或fpga,当需要更新下行通道算法时,需要重新进行硬件的烧制,大大增加了设备成本,无法满足多样化数据通信处理需求。

技术实现要素:

4.有鉴于此,本发明提供一种数据通信处理方法及系统,主要目的在于解决现有数据通信效率低的问题。

5.依据本发明一个方面,提供了一种数据通信处理方法,包括:

6.通过处理器向调整单元发送校正参数,所述校正参数为基于放大单元放大后的第一通信数据以及基于所述调整单元校正后的第二通信数据进行运算处理得到的;

7.通过所述调整单元获取待传输的目标通信数据后,在所述调整单元中基于校正参数对所述目标通信数据进行校正,并将校正后的所述目标通信数据发送至放大单元;

8.通过所述放大单元对所述目标通信数据进行放大,并传输放大后的所述目标通信数据。

9.进一步地,所述方法还包括:

10.信号捕获单元获取基于所述放大单元放大后的第一通信数据以及基于所述调整单元校正后的第二通信数据,并在所述处理器中对所述第一通信数据、所述第二通信数据进行指令集结构调整处理;

11.所述处理器对进行所述指令集结构调整处理的所述第一通信数据、所述第二通信数据进行校正参数计算,得到校正参数;

12.所述通过处理器向调整单元发送校正参数包括:

13.所述处理器通过向量机机制将所述校正参数发送至所述调整单元。

14.进一步地,所述第一通信数据、所述第二通信数据分别存储于直接存储访问单元、以及随机存取存储器中,所述方法还包括:

15.所述直接存储访问单元通过所述随机存储器将携带有第一通信数据、所述第二通信数据的通信指令传输至所述处理器中,以进行指令集结构调整处理。

16.进一步地,所述在所述处理器中对所述第一通信数据、所述第二通信数据进行指令集结构调整处理包括:

17.所述处理器按照所述通信指令的指令形式确定与所述第一通信数据、所述第二通信数据对应的指令内容,并对所述指令内容对应的定点数据进行扩位和/或饱和处理,得到调整处理后携带有所述第一通信数据、所述第二通信数据的指令集;

18.其中,若所述定点数据为复数,则所述处理器对所述定点数据进行复数运算,得到调整处理后的携带有所述第一通信数据、所述第二通信数据的指令集。

19.进一步地,所述处理器对所述定点数据进行复数运算,得到调整处理后的携带有所述第一通信数据、所述第二通信数据的指令集包括:

20.确定所述定点数据中的复数信号以及复数抽头,并按照复数均衡求和函数对所述复数信号以及所述复数抽头进行运算,得到调整处理后的携带有所述第一通信数据、所述第二通信数据的指令集。

21.依据本发明另一个方面,提供了一种数据通信处理系统,包括:

22.调整单元、放大单元、处理器,所述调整单元分别与所述放大单元、所述处理器进行数据连接;

23.所述处理器,用于信号捕获单元获取基于所述放大单元放大后的第一通信数据以及基于所述调整单元校正后的第二通信数据,并根据所述第一通信数据、所述第二通信数据进行运算处理得到校正参数,发送至所述调整单元;

24.所述调整单元,用于基于所述校正参数对待传输的目标通信数据进行校正,并将校正后的所述目标通信数据发送至所述放大单元;

25.所述放大单元,用于对所述目标通信数据进行通信,并传输放大后的所述目标通信数据。

26.进一步地,所述处理器,具体用于信号捕获单元获取基于所述放大单元放大后的第一通信数据以及基于所述调整单元校正后的第二通信数据,并在所述处理器中对所述第一通信数据、所述第二通信数据进行指令集结构调整处理;对所述第一通信数据、所述第二通信数据进行校正参数计算,得到校正参数;通过向量机机制将所述校正参数发送至所述调整单元。

27.进一步地,所述系统还包括:直接存储访问单元、随机存取存储器,所述直接存储访问单元包括第一直接存储访问单元、第二直接存储访问单元,所述第一直接存储访问单元与所述调整单元进行数据连接,所述第二直接存储访问单元与放大单元进行数据连接;

28.所述第一直接存储访问单元,用于缓存所述调整单元向所述放大单元发送的调整后的所述第一通信数据,并将携带所述第一通信数据的通信指令传输至所述处理器中;

29.所述第二直接存储访问单元,用于缓存所述放大单元放大后的所述第二通信数据,并将携带所述第二通信数据的通信指令传输至所述处理器中。

30.进一步地,所述随机存取存储器的一端分别与所述第一直接存储访问单元、所述第二直接存储访问单元进行数据连接,所述随机存取存储器的另一端与所述处理器进行数据连接;

31.所述随机存取存储器,用于缓存所述第一通信数据以及所述第二通信数据。

32.进一步地,所述系统还包括:运行存储器,所述运行存储器与所述处理器进行数据连接;

33.所述运行存储器,用于向所述处理器提供运行数据空间;

34.所述系统还包括:信号捕获单元,

35.所述信号捕获单元分别与所述第一直接存储访问单元、所述第二直接存储访问单元的一端进行数据连接,用于将从所述放大单元捕获的第一通信数据、以及从所述调整单元捕获的第二通信数据传输至所述第一直接存储访问单元、所述第二直接存储访问单元。

36.借由上述技术方案,本发明实施例提供的技术方案至少具有下列优点:

37.本发明提供了一种数据通信处理方法及系统,与现有技术相比,本发明实施例通过处理器向调整单元发送校正参数,所述校正参数为基于放大单元放大后的第一通信数据以及基于所述调整单元校正后的第二通信数据进行运算处理得到的;通过所述调整单元获取待传输的目标通信数据后,在所述调整单元中基于校正参数对所述目标通信数据进行校正,并将校正后的所述目标通信数据发送至放大单元;通过所述放大单元对所述目标通信数据进行放大,并传输放大后的所述目标通信数据,降低了通信设备的设备开发成本,满足算法优化及多种场景的算法切换的灵活性需求,降低了逻辑硬件资源消耗,从而满足多样化数据通信处理需求。

38.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

附图说明

39.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。而且在整个附图中,用相同的参考符号表示相同的部件。在附图中:

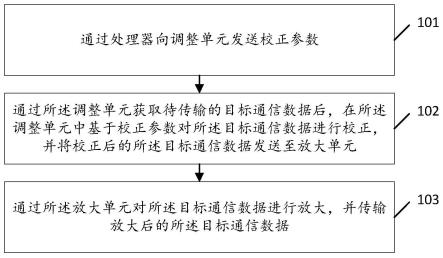

40.图1示出了本发明实施例提供的一种数据通信处理方法流程图;

41.图2示出了本发明实施例提供的一种系统结构示意图;

42.图3示出了本发明实施例提供的另一种数据通信处理方法流程图;

43.图4示出了本发明实施例提供的一种数据通信处理系统的结构示意图。

具体实施方式

44.下面将参照附图更详细地描述本公开的示例性实施例。虽然附图中显示了本公开的示例性实施例,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施例所限制。相反,提供这些实施例是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

45.针对大型设备商通常将射频拉远单元rru嵌入至专用集成电路asic(application specific integrated circuit)或可编程器件fpga(field programmable gate array)中,以实现各种算法在硬件电路中的定制化需求。但是,由于在射频拉远单元rru中的下行通道算法通过硬件逻辑单元固化地嵌入至asic或fpga,当需要更新下行通道算法时,需要

重新进行硬件的烧制,大大增加了设备成本,无法满足多样化数据通信处理需求。本发明实施例提供了一种数据通信处理方法,如图1所示,该方法包括:

46.101、通过处理器向调整单元发送校正参数。

47.本发明实施例中,执行数据通信处理方法的系统至少包括调整单元、放大单元、处理器,其中,调整单元分别与放大单元、所述处理器进行数据连接,如图2所示的系统结构示意图,处理器gp-cpu向调整单元发送校正参数。其中,基于所述校正参数为基于放大单元放大后的第一通信数据以及基于所述调整单元校正后的第二通信数据进行运算处理得到的,即在处理器中基于预先配置的运算算法对第一通信数据、第二通信数据进行运算,得到需要对前向数据进行校正的校正参数,通过处理器发送至调整单元,以便调整单元进行比较调整。

48.需要说明的是,本发明实施例中的处理器可以为任意型号的通用处理器,如gp-cpu等,优选为矢量处理器,矢量处理器可对浮点进行运算,可简化算法设计,提升研发效率。调整单元可以为具有比较功能的调整运算设备,如任意型号的单片机、运算电路等,本发明实施例不做具体限定。

49.102、通过所述调整单元获取待传输的目标通信数据后,在所述调整单元中基于校正参数对所述目标通信数据进行校正,并将校正后的所述目标通信数据发送至放大单元。

50.本发明实施例中,当调整单元接收到处理器发送的校正参数后,可以存储在查找表lut中,以便对目标通信数据进行比较。调整单元实时接收传输来的目标通信数据,并在获取到待传输的目标通信数据后,调取存储在lut表中的校正参数,并进行校正,将校正后的目标通信数据发送至放大单元。具体的,依据数据传输的功率值大小对应的系数进行查表lut赋值,而查找表lut可以根据处理器gp-cpu的计算定期进行更新。同时,由于作为前向数据的目标通信数据和表lut中的校正参数的更新都是实时的,在保证校正后信号性能的同时,为保持数据正确和校正稳定,lut表更新和校正配置为串行操作,保证了校正操作的稳定性。

51.需要说的是,本发明实施例中的基于校正参数进行校正,包括但不限于数字预失真(dpd),iq不平衡校正、本振直流消除等,具体的,可以基于作为调整前前向数据的目标通信数据与校正参数进行比较,当比较的结果大于预先设定的校正差异时,基于此校正参数对目标通信数据进行校正,即校正为等于此校正参数,或者校正为与此校正参数之间的差异小于校正差异,得到校正后的目标通信数据,本发明实施例不做具体限定。

52.103、通过所述放大单元对所述目标通信数据进行放大,并传输放大后的所述目标通信数据。

53.本发明实施例中,将调整后的目标通信数据从调整单元传输至放大单元,以便经过信号放大后通过天馈向外传输。其中,放大单元可以为任意型号的模拟放大器,以便将调整后的目标通信数据进行放大后向外传输。

54.需要说明的是,在前述传统基于专用大规模集成电路asic的架构下,将算法反馈计算部分由硬件逻辑转变为矢量通用处理器实现,即处理器通过运算得到校正参数,发送至调整单元对前向数据进行校正,从而在不增加asic的逻辑资源数据基础上实现更丰富的应用场景,如不同天线数、不同制式、不同载波带宽的多种组合。

55.在另一个本发明实施例中,为了进一步限定及说明,如图3所示,步骤还包括:

56.201、信号捕获单元获取基于所述放大单元放大后的第一通信数据以及基于所述调整单元校正后的第二通信数据,并在所述处理器中对所述第一通信数据、所述第二通信数据进行指令集结构调整处理;

57.202、所述处理器对进行所述指令集结构调整处理的所述第一通信数据、所述第二通信数据进行校正参数计算,得到校正参数;

58.对应的,所述通过处理器向调整单元发送校正参数包括:

59.203、所述处理器通过向量机机制将所述校正参数发送至所述调整单元。

60.本发明实施例中,为了满足实时性要求高,避免使用逻辑硬件编程烧写的方式固化在asic中,从而满足灵活的多应用场景需求,如图2所示,系统中还包括信号捕获单元,当调整单元将目标通信数据进行校正后,传输至放大单元过程中,信号捕获单元捕获放大后的第一通信数据,即为非线性失真信号反馈得到的,同时捕获调整后的作为前向数据的第二通信数据,从而传输给gp-cpu。其中,在存在对射频信号采样的通信数据具有处理器中的运算需求时,目标通信数据是一种伪随机序列,需要对前向的目标通信数据和反馈的目标通信数据进行对齐才能进行后续处理,故前向/反馈信号捕获单元可以配置同步机制,即可将两路数据流(第一通信数据流、第二通信数据流)进行同步捕获。还可以配置延时捕获,针对链路延时场景中,同时收到捕获触发后,信号捕获单元可分别配置额外的捕获时延,以分别捕获第一通信数据、第二通信数据,本发明实施例不做具体限定。

61.另外,由于通信数据在传输过程中是基于指令中携带的,因此,处理器在接收到第一通信数据、第二通信数据后,对其进行指令集结构调整处理,以便于进行运算得到校正参数。其中,处理器在基于第一通信数据、第二通信数据进行校正参数计算时,具体可以基于机器学习算法、线性函数算法等根据不同的通信场景进行配置,例如,根据按照指定场景下的通信训练样本完成训练的深度学习算法对第一通信数据、第二通信数据进行运算,得到校正参数,本发明实施例不做具体限定。

62.需要说明的是,通过处理器向调整单元发送校正参数时,为了高效且准确的进行传输,处理器采用向量机机制将带有校正参数的指令发送至调整单元。其中,处理器中将所有抽头预先加载到向量寄存器中,对需要进行传输的校正参数的指令进行计算编排,如y[i;i+m-1]=x[i]*[a[m-1],a[m-2],...a[0]],其中,x为输入负数信号,a为复数抽头,i=1...m,抽头为数字信号处理中每个系数的引入点,本发明实施例中可以基于不同通信场景进行配置抽头,不做具体限定。当完成计算编排的指令后,作为处理器中流水线式向调整单元传输。

[0063]

在另一个本发明实施例中,为了进一步限定及说明,步骤第一通信数据、所述第二通信数据分别存储于直接存储访问单元、以及随机存取存储器中,所述方法还包括:

[0064]

所述直接存储访问单元通过所述随机存储器将携带有第一通信数据、所述第二通信数据的通信指令传输至所述处理器中,以进行指令集结构调整处理。

[0065]

如图2所示,为了满足系统的稳定性、有效性,减化硬件改进的操作复杂性,系统还包括直接存储访问单元dma、随机存储器ram。其中,直接存储访问单元dma包括第一直接存储访问单元、第二直接存储访问单元,第一直接存储访问单元与所述调整单元进行数据连接,第二直接存储访问单元与放大单元进行数据连接。此时,第一直接存储访问单元缓存调整单元向放大单元发送的调整后的第一通信数据,并将携带第一通信数据的通信指令传输

至处理器中,同时,第二直接存储访问单元缓存所述放大单元放大后的第二通信数据,并将携带第二通信数据的通信指令传输至处理器中,以进行指令集结构调整处理。

[0066]

在另一个本发明实施例中,为了进一步限定及说明,步骤在所述处理器中对所述第一通信数据、所述第二通信数据进行指令集结构调整处理包括:

[0067]

所述处理器按照所述通信指令的指令形式确定与所述第一通信数据、所述第二通信数据对应的指令内容,并对所述指令内容对应的定点数据进行扩位和/或饱和处理,得到调整处理后携带有所述第一通信数据、所述第二通信数据的指令集;

[0068]

其中,若所述定点数据为复数,则所述处理器对所述定点数据进行复数运算,得到调整处理后的携带有所述第一通信数据、所述第二通信数据的指令集。

[0069]

为了满足基于指令进行不同通信场景中数据通信传输的需求,处理器在对第一通信数据、第二通信数据进行指令集结构调整处理时,具体的,处理器首先按照通信指令的指令形式确定第一通信数据、第二通信数据所对应的指令内容,如q15格式通信指令编码形式的指令内容,1位符号位sign+15位小数位fraction,一个采样点sample使用32bit,包含两个q15的i/q部分,本发明实施例不做具体限定。为了提高处理器中的运算速度,可以采用定点运算方式(single instruction multiple data,simd)进行对指令进行处理,即针对单指令流多数据流,一次运算指令可以执行多个数据流,本发明实施例不做具体限定。另外,本发明实施例中的定点数据可以为基于不同通信场景进行配置的,也可以为预先进行选取好的,不做具体限定。在一个具体的实施场景中,对指令数据进行扩位处理可以包括扩位乘法、扩位乘累加处理,具体的,将定位数据的格式进行相乘:q15格式

×

q15格式=q30,res(32bit)=q30<<1,完成扩位乘法后的指令内容。将指令数据的格式进行乘累加:res(32bit)=q30+(q15

×

q15),完成乘累加处理后的指令内容。在一个具体的实施场景中,对定点数据进行饱和处理,可以对定点数运算结果直接做进位处理,本发明实施例不做具有限定。本发明实施例中,对定点数据分别进行扩位乘法、乘累加处理时,将计算方法分别配置为y[n]=sum(x[n-i]*a[m-1-i]+x[n-i+1]*a[m-i]),i=1,3...m-1、y[n+1]=sum(x[n-i+1]*a[m-1-i]+x[n-i+2]*a[m-i]),i=1,3>>m-1。

[0070]

需要说明的是,单指令多数据运算时,即可以实现同一条指令操作多个8/16/32位数据,包括不限于上述的扩位和/或饱和处理,从而实现对指令集的结构优化目的。

[0071]

在一个具体实施场景中,指令集可以包括:pkbb32、smaldrs、smalxda、pbkt32等,其中,针对pkbb32指令,将t0,t2两个寄存器中通信数据的低32位组成一个64bit的,包含两个采样结果,即t0=x[n-i],x[n-i+1],以进行实部以及虚部的计算。针对smaldrs指令,进行复数乘累加,将t0,t1两个寄存器中两组通信数据分别做乘累加,即完成y[n]=sum(x[n-i]*a[m-1-i]+x[n-i+1]*a[m-i]),i=1,3...m-1中的实部运算,并将运算结果累加到64bit寄存器中。针对smalxda指令,进行复数交叉减累加,完成式y[n]=sum(x[n-i]*a[m-1-i]+x[n-i+1]*a[m-i]),i=1,3...m-1中的虚部运算。针对pbkt32指令,将t0,t2中的高32bit通信数据组合成64bit,即可实现t0=x[n-i+1],x[n-i+2],本发明实施例不做具体限定。

[0072]

在另一个本发明实施例中,为了进一步限定及说明,步骤处理器对所述定点数据进行复数运算,得到调整处理后的携带有所述第一通信数据、所述第二通信数据的指令集包括:

[0073]

确定所述定点数据中的复数信号以及复数抽头,并按照复数均衡求和函数对所述

复数信号以及所述复数抽头进行运算,得到调整处理后的携带有所述第一通信数据、所述第二通信数据的指令集。

[0074]

本发明实施例中,为了满足复数定点数据的运算处理场景,在对复数定点数据进行运算时,首先确定定点数据中的用作输入的复数信号x,以及预先配置或选取的复数抽头a,然后按照复数均衡求和函数对复数信号以及复数抽头进行运算,其中,复数均衡求和函数可以基于复数运算公式(a+ib)*(c+id),在单指令内实现r1=a*c-b*d,r2=a*d+b*c,即得到结果r1+i*r2进行构造,得到复数均衡求和函数为:y[n]=sum(x[n-i]*a[m-1-i]),i=1...m。

[0075]

本发明提供了一种数据通信处理方法,与现有技术相比,本发明实施例通过处理器向调整单元发送校正参数,所述校正参数为基于放大单元放大后的第一通信数据以及基于所述调整单元校正后的第二通信数据进行运算处理得到的;通过所述调整单元获取待传输的目标通信数据后,在所述调整单元中基于校正参数对所述目标通信数据进行校正,并将校正后的所述目标通信数据发送至放大单元;通过所述放大单元对所述目标通信数据进行放大,并传输放大后的所述目标通信数据,降低了通信设备的设备开发成本,满足算法优化及多种场景的算法切换的灵活性需求,降低了逻辑硬件资源消耗,从而满足多样化数据通信处理需求。

[0076]

进一步的,作为对上述图1所示方法的实现,本发明实施例提供了一种数据通信处理系统,如图4所示,该系统包括:调整单元31、放大单元32、处理器33,所述调整单元31分别与所述放大单元32、所述处理器33进行数据连接;

[0077]

所述处理器33,用于信号捕获单元获取基于所述放大单元32放大后的第一通信数据以及基于所述调整单元31校正后的第二通信数据,并根据所述第一通信数据、所述第二通信数据进行运算处理得到校正参数,发送至所述调整单元31;

[0078]

所述调整单元31,用于基于所述校正参数对待传输的目标通信数据进行校正,并将校正后的所述目标通信数据发送至所述放大单元32;

[0079]

所述放大单元32,用于对所述目标通信数据进行通信,并传输放大后的所述目标通信数据。

[0080]

进一步地,所述处理器,具体用于信号捕获单元获取基于所述放大单元放大后的第一通信数据以及基于所述调整单元校正后的第二通信数据,并在所述处理器中对所述第一通信数据、所述第二通信数据进行指令集结构调整处理;对所述第一通信数据、所述第二通信数据进行校正参数计算,得到校正参数;通过向量机机制将所述校正参数发送至所述调整单元。

[0081]

进一步地,所述系统还包括:直接存储访问单元、随机存取存储器,所述直接存储访问单元包括第一直接存储访问单元、第二直接存储访问单元,所述第一直接存储访问单元与所述调整单元进行数据连接,所述第二直接存储访问单元与放大单元进行数据连接;

[0082]

所述第一直接存储访问单元,用于缓存所述调整单元向所述放大单元发送的调整后的所述第一通信数据,并将携带所述第一通信数据的通信指令传输至所述处理器中;

[0083]

所述第二直接存储访问单元,用于缓存所述放大单元放大后的所述第二通信数据,并将携带所述第二通信数据的通信指令传输至所述处理器中。

[0084]

进一步地,所述随机存取存储器的一端分别与所述第一直接存储访问单元、所述

第二直接存储访问单元进行数据连接,所述随机存取存储器的另一端与所述处理器进行数据连接;

[0085]

所述随机存取存储器,用于缓存所述第一通信数据以及所述第二通信数据。

[0086]

进一步地,所述系统还包括:运行存储器,所述运行存储器与所述处理器进行数据连接;

[0087]

所述运行存储器,用于向所述处理器提供运行数据空间;

[0088]

所述系统还包括:信号捕获单元,

[0089]

所述信号捕获单元分别与所述第一直接存储访问单元、所述第二直接存储访问单元的一端进行数据连接,用于将从所述放大单元捕获的第一通信数据、以及从所述调整单元捕获的第二通信数据传输至所述第一直接存储访问单元、所述第二直接存储访问单元。

[0090]

本发明提供了一种数据通信处理系统,与现有技术相比,本发明实施例通过处理器向调整单元发送校正参数,所述校正参数为基于放大单元放大后的第一通信数据以及基于所述调整单元校正后的第二通信数据进行运算处理得到的;通过所述调整单元获取待传输的目标通信数据后,在所述调整单元中基于校正参数对所述目标通信数据进行校正,并将校正后的所述目标通信数据发送至放大单元;通过所述放大单元对所述目标通信数据进行放大,并传输放大后的所述目标通信数据,降低了通信设备的设备开发成本,满足算法优化及多种场景的算法切换的灵活性需求,降低了逻辑硬件资源消耗,从而满足多样化数据通信处理需求。

[0091]

显然,本领域的技术人员应该明白,上述的本发明的各模块或各步骤可以用通用的计算装置来实现,它们可以集中在单个的计算装置上,或者分布在多个计算装置所组成的网络上,可选地,它们可以用计算装置可执行的程序代码来实现,从而,可以将它们存储在存储装置中由计算装置来执行,并且在某些情况下,可以以不同于此处的顺序执行所示出或描述的步骤,或者将它们分别制作成各个集成电路模块,或者将它们中的多个模块或步骤制作成单个集成电路模块来实现。这样,本发明不限制于任何特定的硬件和软件结合。

[0092]

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包括在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1