面向CMOS图像传感器的实时压缩存储内核

本发明属于cmos图像传感器数据处理系统领域和可编程逻辑器件领域,具体涉及到risc-v六级流水线处理器设计,ddr3接口控制设计以及jpeg-ls协处理器设计。

背景技术:

1、cmos(complementary metal-oxide-semiconductor)图像传感器是使用cmos工艺,将像素阵列单元、放大电路、模数转换器、时序控制逻辑、信号处理单元和外部接口单元这些功能模块全部集成在一片芯片上,从而实现图像采集的功能。

2、随着cmos图像传感器的像素分辨率不断提高,动态范围不断扩大,导致需要实时传输以及预处理的图像数据量越来越大,而且多通道设计给图像采集和传输系统带来更大的带宽压力。

3、最直接的解决办法是提高存储器容量,双倍速率同步动态随机存储器——ddrsdram是一种最为成熟的高速率、高带宽、大容量的存储器。但是大容量存储器十分昂贵,容量提升有限。

4、因此,除了片外缓存,还可以在近图像传感器端进行实时的图像压缩处理,这有效地降低数据量,减轻了传输接口的带宽压力。

5、图像压缩的理论基础是其数据本身包含了大量冗余信息,理论上来说主要有编码冗余、像素间冗余、心里视觉冗余这三种冗余信息,而且像素分辨率越高的图像,图像数据的局部相关性越大,即冗余信息越多。

6、jpeg-ls压缩标准是基于hp实验室开发的算法—loco-i,是iso和itu—t认可的新一代图像压缩标准,可以选择性的实现无损压缩和近无损压缩。

7、但是jpeg-ls算法码率不可控,对误差十分敏感,在与ddr3进行数据交互的时候,如果出现像素误差,一直累计到最后可能导致整张图像无法还原。

8、risc-v是美国加州大学伯克利分校研发的完全开源的一种精简指令集体系结构。

9、基于模块化设计的risc-v体系结构可以根据需要设计出灵活控制其他模块且能效比较高的cpu,这样的cpu是为整个系统量身定制的,可以解决ddr3和jpeg-ls压缩模块之间的数据交互,以及复杂的码率控制问题。

10、目前对于图像传感器存储的研究主要集中在ddr缓存策略和传输接口方案,还没有类似整体系统的内核设计。

11、然而“功耗墙”、“内存墙”和“性能墙”等问题日益突出,这不仅仅需要优化算法或者接口的某一方面,而是需要系统整体的架构优化。

技术实现思路

1、本发明的目的是面向cmos图像传感器量身定制一种压缩存储内核,用于实时压缩和存储大量的数据,通过整体架构优化和定制设计,保证数据准确性和更低的功耗。

2、本发明的技术方案为:

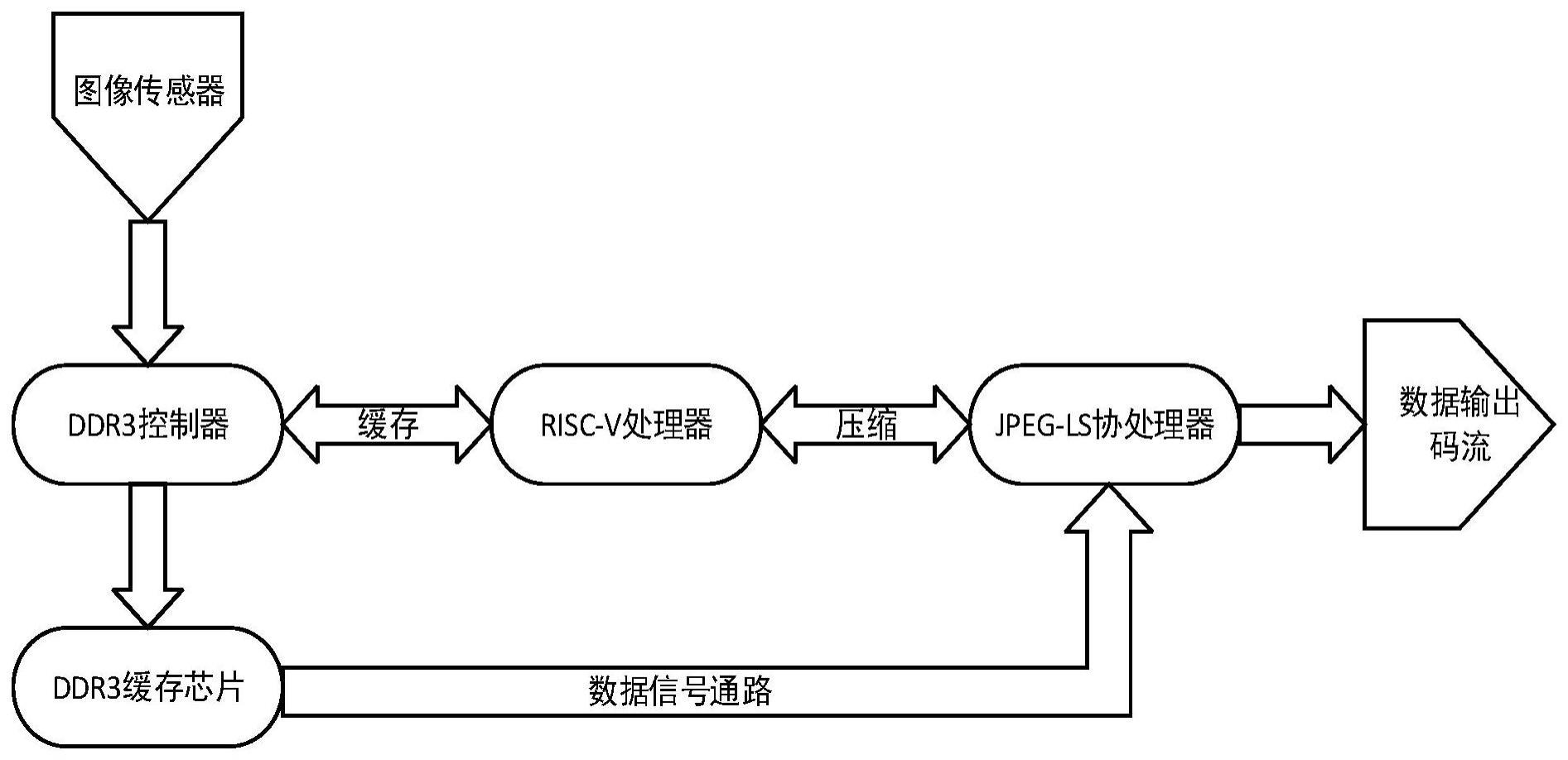

3、一种面向cmos图像传感器的实时压缩存储内核,包括ddr3接口控制模块、risc-v处理器模块以及jpeg-ls协处理器模块。

4、整体方案示意图如图1所示,ddr3芯片作为图像数据的缓存中心,由ddr3接口控制模块控制缓存图像传感器的图像数据;risc-v处理器模块定制了rv64im指令,支持裁剪版的rt-thread嵌入式操作系统,作为主控核心,调度在ddr3芯片内缓存的图像数据以及控制jpeg-ls协处理器的码流;jpeg-ls协处理器模块实现了jpeg-ls压缩算法,受risc-v处理器模块控制,压缩来自ddr3芯片的图像数据并输出。

5、所述的ddr3接口控制模块如图2所示,用于控制向ddr3芯片写入图像传感器的数据以及从ddr3芯片读出数据到jpeg-ls协处理器的数据流向。ddr3接口控制模块物理层基于xilinx公司的mig ip配置ddr3的参数,包括ddr3芯片的工作频率(i/o频率)、用户端时钟频率、突发长度、数据位宽、读取模式、阻抗匹配、端口电平和引脚对应关系。ddr3接口控制模块用户层设计主要包括读/写状态机和fifo缓冲区。

6、所述的读/写状态机如图3所示,包括复位状态、空闲状态、写入状态、顺序读出状态和指定读出状态。当一帧图像空间存满或者复位信号有效时,进入复位状态;复位初始化完成后进入空闲状态等待命令;fifo缓冲区中的读/写缓冲区可分别发出读出/写入有效信号,写入有效信号优先级高于读出有效信号,该组信号使读/写状态机从空闲状态切换为顺序读出状态/写入状态;risc-v处理器模块发来的指定位置读出信号优先级最高,使读/写状态机从空闲状态切换为指定读出状态。

7、所述的fifo缓冲区包括ddr3芯片读/写缓冲区和数据同步模块,由读/写状态机、图像传感器接口信号和risc-v处理器模块共同控制。其中,写入缓冲区检测图像传感器的数据同步信号、本级缓冲区和读/写状态机的状态,决定是否接收来自图像传感器的数据以及转发本级缓冲区数据给ddr3芯片缓存;读出缓冲区检测本级缓冲区和读/写状态机的状态,以及risc-v处理器模块的控制信号,决定是否从ddr3芯片读出数据以及转发本级缓冲区数据给jpeg-ls协处理器;数据同步模块在ddr3接口控制模块的最后一级,负责输出数据的位宽转换和跨时钟域同步处理。

8、综上所述,顺序传输时:ddr3接口控制模块整体完成初始化后,自动连续缓存图像传感器的图像数据,由图3所示读/写状态机、写入缓冲区和图像传感器的数据同步信号控制,顺序缓存图像数据到ddr3芯片;由risc-v处理器模块、读/写状态机模块和读出缓冲区控制,顺序读出数据;由risc-v处理器模块校验读出的数据,无误后经过数据同步模块输出到jpeg-ls协处理器模块。指定位置传输或者数据校验出错时:由risc-v处理器模块发出指定图像帧的指定地址信号,重新传输该段数据,完成后重复顺序传输过程。当且仅当本帧图像数据由risc-v处理器模块校验完成后,ddr3接口控制模块才释放该缓存区域,此时该区域可被新一帧图像数据覆盖。

9、所述的risc-v处理器模块如图4所示,包括in-order六级流水线模块、l1级cache模块、axi4总线及仲裁器和外设模块。其中,in-order六级流水线模块取指部分采用静态分支预测,预测后的指令输出到一级译码模块;一级译码对指令解码,重编码,并生成用来读出通用寄存器组的使能和地址信号;32个64位通用寄存器组模块根据一级译码和写回寄存器组模块的读/写信号以及地址信息,对本模块的通用寄存器进行读/写操作;二级译码对一级译码重编码的指令进行指令融合,生成执行阶段所需的操作数和操作符等信号;执行阶段包括多个逻辑和算术运算alu模块,集中进行运算,运算结果输出到访问内存模块;访问内存根据运算结果和指令信息,处理总线访问对齐及数据掩码,连续访存指令策略是插入气泡,阻塞流水线;最终,写回寄存器模块根据指令判断是否写回到32个64位通用寄存器组模块。clint(core local interrupt)模块是核内本地中断,用来处理时钟中断,该模块优先级最高,能够随时中断正在运行的流水线。l1级cache模块包括i-cache和d-cache,均采用两路组相联结构,cache line为128bit,每个cache容量为4kb,替换算法为采用伪lru算法,设置1bit年龄位判断;基本策略是write back和write allocate,该模块作为指令(instruction)和数据(data)的高速缓存,直接与取指模块和访问内存模块进行数据交互,通过如图4所示的axi4仲裁器与axi4总线进行数据交互(即同时只能有一个cache或者一个直接访问外设命令和axi4总线交互)。外设模块包括ram、ddr3接口控制模块、jpeg-ls协处理器和图像传感器接口;其中由于本发明定制设计的risc-v处理器支持裁剪版的rt-thread操作系统,所以可使用小容量ram作为内存。

10、综上所述,risc-v处理器模块由底层in-order六级流水线模块执行指令,由l1级cache和axi4总线交互,由axi4总线和各个外设交互。从宏观功能上看,risc-v处理器模块调度ddr3芯片缓存的图像数据,数据校验无误后开启jpeg-ls协处理器,同时控制ddr3接口控制模块转发对应数据;若有误,则控制ddr3接口控制模块重新传输指定错误位置的数据;最后控制jpeg-ls协处理器的码率控制器模块拼接数据,根据系统前后接口的带宽控制码率并输出压缩后的数据。

11、所述的jpeg-ls协处理器模块,如图5所示,主要包括建模预处理模块、编码控制模块以及码率控制器模块。其中,建模预处理模块由risc-v处理器模块控制,由ddr3接口控制器模块转发数据;编码控制模块包括正常模式编码——golomb编码和游程模式编码,由模块内部扫描确定编码方式;所述的码率控制器模块,拼接编码后的数据并做数据对齐处理,由risc-v处理器模块控制码率。

12、所述的jpeg-ls协处理器模块内部数据流向为:

13、(1)建模预处理模块接收控制和状态寄存器信号,开始接收数据,并进行局部梯度值的计算、量化和判断选择,输出结果到编码控制模块;

14、(2)编码控制模块根据具体梯度值结果信号决定编码模式:正常编码(golomb编码)和游程编码。正常编码时,对计算出来的预测误差进行golomb编码映射,更新像素数据,输出到码率控制器模块。游程编码时,基于建模的模板对数据进行游程长度扫描,记录扫描的数据的地址区间,记为游程长度(局部梯度值全为0);若扫描到本组数据末尾或者判断建模的局部梯度值不全为0时,则跳出游程扫描,记录地址区间,跳出之前记为游程长度,跳出之后记为中断长度;然后对游程长度内进行归一化编码处理,对中断长度内编码进行golomb编码并输出到码率控制器模块;

15、(3)码率控制器模块,受risc-v处理器模块控制,将本次正常编码和游程编码的码流拼接到一起,拼接完成的码流由risc-v处理器模块控制进入协处理器内部缓存,一帧图像统一输出,并控制输出码率。

16、本发明的有益效果:本发明为通用型压缩存储内核设计,将压缩算法固化为硬件协处理器加速压缩过程,并且通过定制risc-v处理器最大化减少了电路面积,且通过系统层面优化控制,使ddr3接口控制器模块和jpeg-ls协处理器模块高效稳定工作。

17、本发明使用时可作为自定义ip,给出输入端(图像传感器数据输入)和输出端(传输接口使能信号和数据通道)的信号,并且编写能被risc-v交叉编译工具链编译通过的运行在risc-v处理器上的程序,即可实现大量数据的自定义压缩存储。

- 还没有人留言评论。精彩留言会获得点赞!