一种基于ELoran系统的信号接收装置

一种基于eloran系统的信号接收装置

技术领域

1.本实用新型属于信号接收装置技术领域,特别涉及一种基于eloran系统的信号接收装置。

背景技术:

2.loran-c系统(示例性解释的,包括bpl长波授时系统和长河二号导航系统)通过建立与国家标准时间utc(ntsc)的溯源关系,保持与协调世界时(utc)的同步,进而通过无线电信号的发播实现高精度的授时,并且以其地波相位稳定、抗干扰能力强、覆盖范围广、建设成本低以及具有差分增强功能等优点,已经成为了最主要的陆基授时手段,是国家时间频率体系架构中不可或缺的重要组成部分。

3.其中,bpl长波授时系统和长河二号导航系统已于2008年完成技术升级改造,采用eurofix技术增加了时码信息等数据发播功能,具备eloran信号发射条件,构建成eloran系统。基于此,目前的现有信号接收装置一般是基于fpga+dsp架构或者fpga+mcu架构的装置,装置硬件构成复杂,信号数据传输过程复杂,耗费时间长,亟需一种新的信号接收装置。

技术实现要素:

4.本实用新型的目的在于提供一种基于eloran系统的信号接收装置,以解决上述存在的一个或多个技术问题。

5.为达到上述目的,本实用新型采用以下技术方案:

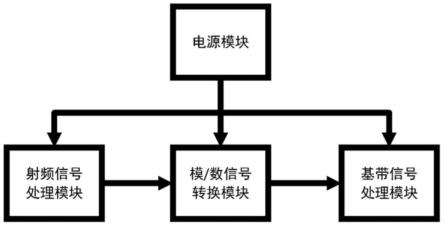

6.本实用新型提供的一种基于eloran系统的信号接收装置,包括:电源模块、射频信号处理模块、模数信号转换模块和基带信号处理模块;

7.所述电源模块用于为所述射频信号处理模块、模数信号转换模块和基带信号处理模块供电;

8.所述射频信号处理模块用于采集获取eloran天线信号并进行初步处理,输出初步处理后的eloran信号;所述初步处理包括带通滤波、自适应陷波和自动增益控制处理;

9.所述模数信号转换模块用于输入所述初步处理后的eloran信号,进行单端信号转换差分信号以及模数信号转换处理,输出低电压差分信号;

10.所述基带信号处理模块用于输入所述低电压差分信号,进行信号解调解码处理,获得解调解码数据;基于解调解码数据输出秒脉冲;

11.其中,所述基带信号处理模块采用xilinx zynq7z020处理器芯片,所述xilinxzynq7z020处理器芯片集成有直连的可编程逻辑资源和处理系统。

12.本实用新型装置的进一步改进在于,所述电源模块包括:

13.直流电压转换芯片lmr16030,用于输入dc+18~+24v电压,转换输出+5v电压;

14.直流电压转换芯片lt1931,用于输入+5v电压,转换输出-5v电压;

15.直流电压转换芯片ld1117-3.3v,用于输入+5v电压,转换输出+3.3v电压;

16.直流电压转换芯片ld1117-1.8v,用于输入+3.3v电压,转换输出+1.8v电压。

17.本实用新型装置的进一步改进在于,所述电源模块的输入端设置有自恢复保险丝、压敏电阻和二极管;其中,所述自恢复保险丝用于防止电源回路中电流过大,所述压敏电阻用于防止输入电压幅值过大,所述二极管用于防止输入电源反接。

18.本实用新型装置的进一步改进在于,所述射频信号处理模块包括带通滤波器、自适应陷波器和自动增益控制电路;其中,所述带通滤波器用于输入eloran天线信号进行带通滤波处理,输出一次处理后信号;所述自适应陷波器用于输入所述一次处理后信号进行自适应陷波处理,输出二次处理后信号;所述自动增益控制电路用于输入所述二次处理后信号进行自动增益控制处理,输出初步处理后的eloran信号。

19.本实用新型装置的进一步改进在于,所述模数信号转换模块包括高速运算放大器lt1819cs8和高速模数转换芯片ltc2324ukg-16;其中,所述高速运算放大器lt1819cs8用于输入初步处理后的eloran信号,转化为差分信号输出;所述高速模数转换芯片ltc2324ukg-16用于输入所述差分信号,转化为低电压差分信号输出。

20.本实用新型装置的进一步改进在于,初步处理后的eloran信号的参考地线端输入所述高速运算放大器lt1819cs8的5号引脚,初步处理后的eloran信号的信号线端输入所述高速运算放大器lt1819cs8的3号引脚,所述高速运算放大器lt1819cs8输出的1号引脚和7号引脚作为一个通道差分信号线的两端。

21.本实用新型装置的进一步改进在于,所述高速模数转换芯片ltc2324ukg-16的输入引脚14号和输入引脚13号为第一对差分信号的输入引脚,输出引脚27和输出引脚28为对应的第一对低电压差分信号输出引脚;所述高速模数转换芯片ltc2324ukg-16的输入引脚11号和输入引脚10号为第二对差分信号的输入引脚,输出引脚29和输出引脚30为对应的第二对低电压差分信号输出引脚;所述高速模数转换芯片ltc2324ukg-16的输入引脚4号和输入引脚5号为第三对差分信号的输入引脚,输出引脚35和输出引脚36为对应的第三对低电压差分信号输出引脚;所述高速模数转换芯片ltc2324ukg-16的输入引脚24号为芯片的使能工作引脚。

22.本实用新型装置的进一步改进在于,所述处理系统为双核arm cortex-a9处理器;所述可编程逻辑资源为artix-7架构28nm可编程逻辑资源。

23.本实用新型装置的进一步改进在于,所述xilinx zynq7z020处理器芯片的y14号引脚和aa14号引脚为第一对低电压差分信号的输入;所述xilinx zynq7z020处理器芯片的aa17号引脚和ab17号引脚为第二对低电压差分信号的输入;所述xilinx zynq7z020处理器芯片的y19号引脚和aa19号引脚为第三对低电压差分信号的输入;所述xilinx zynq7z020处理器芯片的v15号引脚为控制芯片ltc2324ukg的使能工作引脚,v9号引脚为秒脉冲的输出引脚。

24.与现有技术相比,本实用新型具有以下有益效果:

25.本实用新型提供的信号接收装置,采用zynq7z020作为装置的主芯片,其内部同时具有pl(program logic,可编程逻辑)和ps(program system,处理系统),能够完成多种信号接收装置功能,可简化硬件组成;同时,装置中的部分功能模块都集成在该芯片内部,可优化信号数据传输过程,提高装置的信号接受处理速度。

附图说明

26.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面对实施例或现有技术描述中所需要使用的附图做简单的介绍;显而易见地,下面描述中的附图是本实用新型的一些实施例,对于本领域普通技术人员来说,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

27.图1是本实用新型实施例的一种基于eloran系统的信号接收装置的示意框图;

28.图2是本实用新型实施例中,电源模块原理示意图;其中,图2中(a)为+5v电源模块原理示意图,图2中(b)为-5v电源模块原理示意图,图2中(c)为+3.3v电源模块原理示意图,图2中(d)为+1.8v电源模块原理示意图;

29.图3是本实用新型实施例中,射频信号处理模块原理示意图;

30.图4是本实用新型实施例中,模数信号转换模块单端信号转换原理示意图;

31.图5是本实用新型实施例中,模数信号转换模块ltc2324ukg-16原理示意图;

32.图6是本实用新型实施例中,基带信号处理模块硬件示意框图。

具体实施方式

33.请参阅图1,本实用新型实施例的一种基于eloran系统的信号接收装置,包括:电源模块、射频信号处理模块、模数信号转换模块和基带信号处理模块。

34.所述电源模块,用于为射频信号处理模块、模数信号转换模块和基带信号处理模块供电;

35.射频信号处理模块,用于采集获取eloran天线信号并进行初步处理,输出初步处理后的eloran信号;其中,所述初步处理包括:带通滤波、射频放大、自适应陷波和自动增益控制处理;

36.模数信号转换模块,用于输入所述初步处理后的eloran信号,进行单端信号转换差分信号和模数信号转换处理,输出低电压差分信号;

37.基带信号处理模块,用于输入所述低电压差分信号,进行信号解调解码处理,获得解调解码数据;基于解调解码数据输出秒脉冲;

38.其中,基带信号处理模块采用zynq7z020作为主芯片,其内部同时具有pl(program logic,可编程逻辑)和ps(program system,处理系统),用于完成多种信号接收装置功能。

39.请参阅图2,本实用新型实施例装置中的电源模块主要由直流电压转换芯片和电源状态指示组成,用于完成整个装置各模块的电源供应,确保装置运行正常。如图2中(a)所示,电源模块的输入电压为dc+18~+24v,电源接线端子power的1号引脚为输入电压,2号引脚为信号地,3号引脚为输入电压的参考地,在输入端添加自恢复保险丝f500、压敏电阻rl500和二极管d500(解释性的,自恢复保险丝是为了防止电源回路中电流过大;压敏电阻是为了防止输入电压幅值过大;二极管是为了防止输入电源反接)对电源模块做自保护,直流电压转换芯片lmr16030将输入电压变换成+5v输出,lmr16030的2号引脚为输入电压,7号引脚和8号引脚为输入电压和输出电压的参考地,8号引脚为输出电压;其中电阻r503和r504决定转换后的输出电压幅值,计算公式为输出电压vout=(r503/r504+1)*0.75,电容c501、c502作为+5v输出电压的滤波电容,减少其电压纹波变化的影响,r501用于芯片en使能引脚(第3号引脚)的电流限制,r502用于控制该电源芯片的开关频率,d501为续流二极管

给电感l500提供反向放电回路以保护后级电路。

40.当有+5v电源输出时,led指示灯pwr常亮,如图2中(b)所示,直流电压转换芯片lt1931将+5v输入转换为-5v输出,5号引脚为+5v电压输入,2号引脚为+5v输入和-5v输出参考电源地,1号引脚为-5v电压输出,其中r506,r507决定转换后输出电压幅值,计算公式为输出电压vout=(r507/r506+0.9996)*1.255,电容c521、c520作为+5v输出电压的滤波电容,减少其电压纹波变化的影响,r505用于芯片4号引脚使能引脚的电流限制,d502为续流二极管给电感l502提供反向放电回路以保护后级电路。

41.如图2中(c)所示,直流电压转换芯片ld1117-3.3v将输入的+5v变换成+3.3v输出,3号引脚为+5v电压输入,1号引脚为+5v电压输入和+3.3v电压输出的参考地,2号引脚为+3.3v电压输出,其中电容c508和c509作为+3.3v电源输出的滤波电容,减少其电压纹波变化的影响。

42.如图2中(d)所示,直流电压转换芯片ld1117-1.8v将输入的+3.3v变换成+1.8v输出,3号引脚为+3.3v电压输入,1号引脚为+3.3v电压输入和+1.8v电压输出的参考地,2号引脚为+1.8v电压输出,3,其中电容c512和c513作为+1.8v电源输出的滤波电容,减少其电压纹波变化的影响。

43.请参阅图3,本实用新型实施例装置中的射频信号处理模块主要由带通滤波器、自动增益控制电路和陷波器等组成,天线信号接口连接带通滤波器输入,带通滤波器输出连接自适应陷波器输入,自适应陷波器输出连接自动增益控制器输入,自动增益控制器输出初步处理的eloran信号,该模块用于完成eloran天线信号的采集和简单初步处理,将初步处理的eloran信号传输给模数信号转换模块。如图3所示,天线采集的eloran信号经过带通滤波器,自适应陷波器和自动增益控制器处理后,得到单端信号传输至模数信号转换模块。

44.请参阅图4和图5,本实用新型实施例装置中的模数信号转换模块主要由同步采样模数转化器及其相关配套电路组成,该模块用于完成单端信号转换和模拟信号转换为数字信号等功能。示例性的,如图4所示,使用高速运算放大器lt1819cs8将输入单端信号转化为差分信号,模数信号转换模块中可同时处理三通道数据,由于三个通道结构相同,只叙述一个通道连接关系。初步处理后的eloran信号参考地线端输入lt1819cs8的5号引脚,信号线端输入3号引脚,输出的1号引脚和7号引脚为一个通道差分信号线的两端。如图5所示,该模块采用高速模数转换芯片ltc2324ukg-16,该芯片支持四通道高速同步采样,具有16位分辨率、差分输入和宽输入共模范围。该模块使用运放芯片lt1819cs8将射频信号处理模块传输的单端信号转换为差分信号,模数转换芯片再将其转换为lvds(低电压差分信号)传输至基带信号处理模块,ltc2324ukg-16可以处理四通道的差分信号,装置中只有三通道,其中输入引脚14号和输入引脚13号为第一对差分信号的输入引脚,输出引脚27和输出引脚28为对应的第一对lvds输出引脚,输入引脚11号和输入引脚10号为第二对差分信号的输入引脚,输出引脚29和输出引脚30为对应的第二对lvds输出引脚,输入引脚4号和输入引脚5号为第三对差分信号的输入引脚,输出引脚35和输出引脚36为对应的第三对lvds输出引脚,输入引脚24号为该芯片的使能工作引脚。

45.请参阅图6,本实用新型实施例装置中的基带信号处理模块主要由xilinx zynq7z020可编程soc(soc:片上系统/系统级芯片)及其相关配套电路组成,该模块主要完成eloran信号的搜索与捕获、载波相位跟踪与周期识别、信息解调与解码和产生定时信号

等功能。该模块采用xilinx zynq7z020处理器芯片,其具备优异的计算及图形显示性能,在芯片上集成了双核arm cortex-a9处理器(ps:program system),同时集成有artix-7架构28nm可编程逻辑资源(pl:program logic);该模块同时配备有1gb ddr3l sdram(采用32位总线,数据速率1066mhz)、256mb spi flash、64gb emmc存储器等能够满足基带信号处理需求,该模块接收模数信号转换模块传输的lvds信号,应用信号处理算法进行信号峰值检测完成eloran信号的搜索与捕获,再完成载波相位跟踪与周期识别,再经过eloran信息解调、rs解码、crc解码和电文解算得出时码数据,并根据时码数据产生定时信号秒脉冲1pps(pulse per second),zynq7z020的y14号引脚和aa14号引脚为第一对lvds信号的输入,aa17号引脚和ab17号引脚为第二对lvds信号的输入,y19号引脚和aa19号引脚为第三对lvds信号的输入,v15号引脚为控制芯片ltc2324ukg的工作使能,v9号引脚为秒脉冲的输出引脚。输入的lvds信号由芯片内部的ps和pl处理,ps和pl在芯片内部直连,极大的提高了信号处理传输速率,同时也简化了系统的硬件构成。

46.最后应当说明的是:以上实施例仅用以说明本实用新型的技术方案而非对其限制,尽管参照上述实施例对本实用新型进行了详细的说明,所属领域的普通技术人员应当理解:依然可以对本实用新型的具体实施方式进行修改或者等同替换,而未脱离本实用新型精神和范围的任何修改或者等同替换,其均应涵盖在本实用新型的权利要求保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1