一种通过分立器件实现的4M速率1553B通信电路的制作方法

一种通过分立器件实现的4m速率1553b通信电路

技术领域

1.本实用新型电路属于航空航天数据总线通信技术领域,特别涉及一种通过分立器件实现的不同速率的1553b通信电路。

背景技术:

2.mil-std-1553数据总线因其高可靠性、实时性和稳定性等优点,现在已普遍用于民用和军用航天器的机载数据处理系统。早期的1553b速率仅为1mb/s,但随着科技的发展,机载传感器、武器等各种电子装备的信息数据量已经越来越繁琐复杂,1553b仅仅1mb/s的数据传输速度已经无法满足数据量的传输要求。

3.目前在国外的通信技术中,1553总线历经数十年的发展,传输速度也从最先的lmb/s变成了10mb/s甚至更高。但是我国在高速1553总线方面的研究尚处于起步阶段,由于国外在高速1553总线上采取技术封锁,目前国内使用的比较前沿的1553b总线速率为4mb/s。

4.1553b总线的架构可以分为协议处理器和收发器两部分组成。协议芯片主要处理1553b的特定协议,可以通过专用的协议芯片或者fpga(现场可编程逻辑)实现。而收发器的话,与外部总线相连,其稳定性和可靠性至关重要,因而成为整个1553b总线电路设计的关键因素。

5.从实现形式上,大致可以把目前国内的1553高速收发器分为两类:一类是基于原低速1mb/s的1553收发器进行设计参数的调整,使其工作4mb/s甚至更高速率;另一类是采用其他电平符合相关标准的其他总线收发器代替1553收发器,如rs485总线收发器,其速率也可以达到4mb/s。但两种方案均存在一定的缺陷:第一类采用更改设计参数的方式,由于受到原低速电路设计的局限,部分外围电路需要重新设计,同时使用低速收发器进行高速应用,稳定性和可靠性受到了一定的制约。第二类采用其他通用型收发器的方案尽管芯片本身不用重新设计,但原来的传输介质都需要更换,整个系统需要重新布局,投入的成本十分高昂。

技术实现要素:

6.本实用新型的目的在于提供一种通过分立器件实现的4m速率1553b通信电路,以解决上述问题。

7.为实现上述目的,本实用新型采用以下技术方案:

8.一种通过分立器件实现的4m速率1553b通信电路,包括双路p型mos管q1、电阻r1、电阻r2、电阻r3、电阻r4、电阻r5、双路比较器u1、电阻r6、电阻r7、电阻r8、电阻r9、电阻r10、电容c1、电容c2和变压器t1;电阻r1的一端连接第一路pmos的源极,第一路pmos的漏极连接变压器的1管脚;电阻r2的一端连接第二路pmos的源极,第二路pmos的漏极连接变压器的3管脚;r4的一端接第一路比较器的正向输入管脚和电阻r3,电阻r3另一端接第一路比较器的输出管脚,第一路比较器的负向输入接电阻r5和电容c1,电容c1另一端接电阻r6,电阻r6

另一端接变压器t1初级1脚;r8的一端接第一路比较器的正向输入管脚和电阻r7,电阻r7另一端接第一路比较器的输出管脚,第一路比较器的负向输入接电阻r9和电容c2,电容c2另一端接电阻r10,电阻r10另一端接变压器t1初级3脚,变压器t1的2脚接地。

9.进一步的,电阻r1和电阻r2的另一端连接电源vcc5v。

10.进一步的,电阻r4、电阻r5、电阻r8和电阻r9的另一端连接ref1v5。

11.进一步的,第一路pmos管的栅极连接输出tx_p。

12.进一步的,第二路pmos管的栅极连接输出tx_n。

13.进一步的,比较器的7脚接rx_p,比较器的6脚接rx_n。

14.进一步的,变压器次级的5脚连接1553_p。

15.进一步的,变压器次级的7脚连接1553_n。

16.与现有技术相比,本实用新型有以下技术效果:

17.本实用新型采用市场上常用的分立器件进行搭建,价格较低且容易采购,使得通信可以达到4mb/s,而且与原系统进行通信的话,也无需作任何调整,兼顾了电路设计与后期重新布局的成本。

18.此外,在不同速率下使用时,只需更换不同型号的分立器件即可,不用更换已布局好的传输介质线缆及接口。当发器参数需要进行调整时,只需简单更换型号不同的分立器件即可,不用改换钱缆及接口方式,节省了大量成本与时间。对应用者来说,是一种十分便捷的、兼容性高的、扩展性强的设计。

附图说明

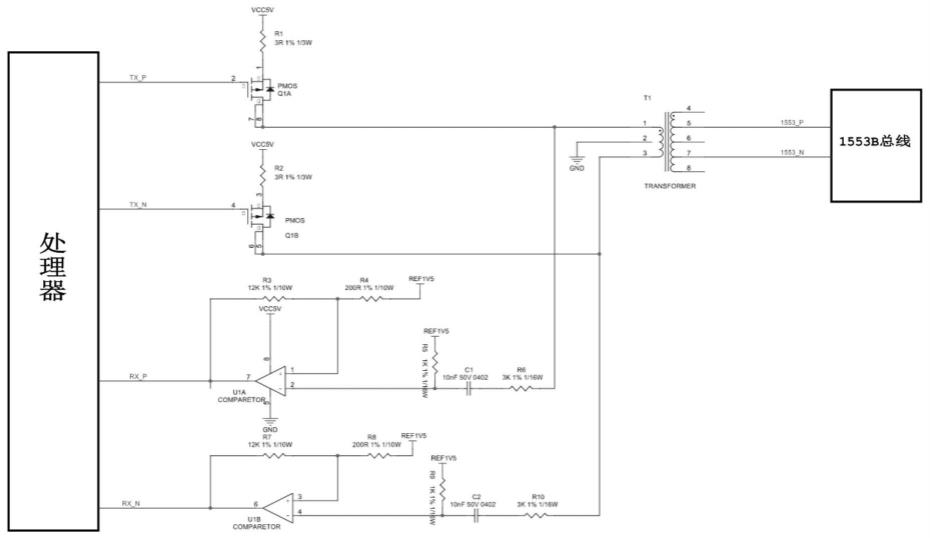

19.图1:本实用新型电路的原理图;

20.图2:本实用新型电路的发送阶段示波器实测波形;

21.图3:本实用新型电路的接收阶段示波器实测波形;

具体实施方式

22.以下结合附图对本实用新型进一步说明:

23.请参阅图1至图3,一种通过分立器件实现的4m速率1553b通信电路,包括电源vcc5v、双路p型mos管q1、电阻r1、电阻r2、电阻r3、电阻r4、电阻r5、比较器u1、电阻r6、电阻r7、电阻r8、电阻r9、电阻r10、电容c1、电容c2、变压器t1。如图1所示。

24.电源vcc5v连接电阻r1,电阻r1的另一端连接第一路pmos的源极,第一路pmos的漏极连接变压器的1管脚;电源vcc5v连接电阻r2,电阻r2的另一端连接第二路pmos的源极,第二路pmos的漏极连接变压器的3管脚;电源ref1v5连接电阻r4,r4的另一端接第一路比较器的正向输入管脚和电阻r3,电阻r3另一端接第一路比较器的输出管脚,第一路比较器的负向输入接电阻r5和电容c1,电阻r5的另一端接ref1v5,电容c1另一端接电阻r6,电阻r6另一端接变压器t1初级1脚;电源ref1v5连接电阻r8,r8的另一端接第一路比较器的正向输入管脚和电阻r7,电阻r7另一端接第一路比较器的输出管脚,第一路比较器的负向输入接电阻r9和电容c2,电阻r9的另一端接ref1v5,电容c2另一端接电阻r10,电阻r10另一端接变压器t1初级3脚,变压器t1的2脚接地。第一路pmos管的栅极连接输出tx_p;第二路pmos管的栅极连接输出tx_n;比较器的7脚接rx_p;比较器6脚接rx_n;变压器次级的5脚连接1553_p;变压

器次级的7脚连接1553_n。

25.在通信电路发送阶段,tx_p和tx_n为处理器发送过来的一组差分电平,当tx_p为高、tx_n为低时,使得q1a关端、q1b导通,相关的,使得vvc5v电源,通过电阻r4、q1b、变压器初级的3管脚,导通至变压器初级的2脚到地。此时同通过变压器t1的耦合,在变压器t1次级的管脚5和管脚7之间,会输出一个差分的低信号,在对外的1553b总线上,对外输出低电平。

26.同样的,当tx_p为低、tx_n为高时,使得q1a导通、q1b关端,相关的,使得vvc5v电源,通过电阻r1、q1a、变压器初级的1管脚,导通至变压器初级的2脚到地。此时同通过变压器t1的耦合,在变压器t1次级的管脚5和管脚7之间,会输出一个差分的高信号,在对外的1553b总线上,对外输出高电平。

27.发送阶段1553b总线的实测波形如图2所示,其中总线上幅值为24v,半个周期时长约为120ns(示波器精度影响,测量有误差),满足4mb/s 1553b标准。

28.在通信接收阶段,当外接的1553b总线上,接收到高电平时,变压器t1次级的5脚为高,7脚为低,耦合到变压器t1的初级,使得变压器t1初级1脚为高,3脚为低,经过电阻r9、c2、r13、c3的隔直和电压抬升,经过比较器u1后,rx_p和rx_n就会接收到对应的差分高电平,传送给处理器内部。

29.同样的,当外接的1553b总线上,接收到低电平时,变压器t1次级的5脚为低,7脚为高,耦合到变压器t1的初级,使得变压器t1初级1脚为低,3脚为高,经过电阻r9、c2、r13、c3的隔直和电压抬升后,再经过比较器u1,rx_p和rx_n就会接收到对应的差分低电平,传送给处理器内部。

30.接收阶段处理器侧rx_p和rx_n的实测波形如图3所示,为差分信号,半个周期时长约为140ns(示波器精度影响,测量有误差),满足4mb/s 1553b标准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1