一种高速长线列CMOS探测器成像电路的制作方法

一种高速长线列cmos探测器成像电路

技术领域

1.本实用新型涉及cmos探测器成像电路技术领域,具体为一种高速长线列cmos探测器成像电路。

背景技术:

2.cmos探测器是一种应用于可见光波段成像的半导体器件,该器件由光电二极管、模数转换器、信号放大器、行/列驱动装置、信号传输及控制装置集成。cmos探测器具有集成度高、功耗低、成本低、抗辐射性强等优点。高分辨率成像系统在航天遥感、工业检测、医学成像等诸多领域都发挥着非常重要的作用。随着半导体设计和加工技术的迅猛发展,cmos探测器的分辨率、噪声抑制、抗辐射等方面性能得到了突破。cmos探测器将进一步扩展其在星敏感器、对地观测、深空探测等高端领域的应用。

3.在航天遥感领域,可见光成像探测是航天探测的重要组成部分,可见光探测技术是指传感器工作在400-650nm波段之间的遥感技术。目前,为了获取更高分辨率的图像数据,对遥感相机分辨率以及观测幅宽要求越来越高,需要采用较长线列的可见光cmos探测器,或者采用多片探测器光刻拼接的方式来满足高分辨率和幅宽要求。

4.目前单片长线列可见光探测器的总长度一般在10cm-20cm,单行像元数更是达到了16k或者32k,行扫描频率更是以万级为趋势,这导致产生的图像数据量迅速增加,传输带宽不断增大,采集速率也随着提升,这对数据的采集,传输和可靠的存储技术提出了更高的要求,而目前的单片长线列可见光探测器已满足不了高分辨率高速成像的需求,因此我们需要提出一种高速长线列cmos探测器成像电路来满足高分辨率高速成像的需求。

技术实现要素:

5.本实用新型的目的在于提供一种高速长线列cmos探测器成像电路,通过图像传感器、驱动电路和数传电路的配合,采用大容量缓存的数据缓存电路和高速信号传输电路解决了高速数据输出问题,满足高分辨高速探测器的需求,以解决背景技术中提出的问题。

6.为实现上述目的,本实用新型提供如下技术方案:一种高速长线列cmos探测器成像电路,包括图像传感器、驱动电路和数传电路,所述图像传感器分别与驱动电路和数传电路电性连接,所述图像传感器包括内部含有128寄存器的gl1608芯片;所述驱动电路包括探测器外围电路和按照cmos探测器启动顺序要求依次作用于时钟、复位、电源使能和驱动spi总线驱动器对cmos进行寄存器配置、控制cmos探测器帧频和积分时间的时序电路,所述探测器外围电路与时序电路电性连接;所述数传电路包括大容量缓存的数据缓存电路、数字图像处理电路和高速信号传输电路,所述数字图像处理电路分别与数据缓存电路和高速信号传输电路电性连接。

7.优选的,所述时序电路包括用于对用户输入信息进行逻辑计算的积分控制电路、控制探测器扫描行频的帧频控制电路和寄存器配置电路,所述积分控制电路与帧频控制电路均与寄存器配置电路电性连接。

8.优选的,所述寄存器配置电路包括计数器、将串行输入的1bit数字信号不断地缓存进一个12bit移位寄存器的串并转换电路、将串转并得到的数据与正确数据进行对比的数据对齐电路、控制计数器保持或计数的触发脉冲产生电路和将外部信号保存在内部寄存器中的锁存器,所述计数器与串并转换电路电性连接,所述串并转换电路与数据对齐电路电性连接,所述数据对齐电路与触发脉冲产生电路电性连接,所述触发脉冲产生电路与锁存器电性连接。

9.优选的,所述探测器外围电路包括电源电路、偏置电路和外部数字接口电路,所述电源电路分别与图像传感器和偏置电路电性连接,所述偏置电路与外部数字接口电路电性连接,所述外部数字接口电路与时序电路电性连接。

10.优选的,所述电源电路包括电源芯片,所述电源芯片设置为tps74801ldo电源芯片,所述电源芯片的七脚连接有cc2,所述cc2的一端与电源芯片一脚之间连接有cc1,所述电源芯片的六脚与八脚之间连接有rc2,所述电源芯片的八脚与九脚之间连接有rc1、所述电源芯片的十一脚与九脚之间连接有cc3。

11.优选的,所述数据缓存电路包括ddr3-sdram芯片,所述ddr3-sdram芯片含有四个512mb内存和32bit位宽。

12.优选的,所述数字图像处理电路包括型号为xc7z035-ffg676-21的图像处理器,所述图像处理器分别与图像传感器和ddr3-sdram芯片连接。

13.优选的,所述高速信号传输电路包括万兆以上的以太网传输器和上位机,所述以太网传输器与上位机电性连接,所述上位机通过rs232接口与数据处理器连接。

14.与现有技术相比,本实用新型的有益效果是:本实用新型主要通过图像传感器、驱动电路和数传电路的配合,采用大容量缓存的数据缓存电路和高速信号传输电路解决了高速数据输出问题,满足高分辨高速探测器的需求。

附图说明

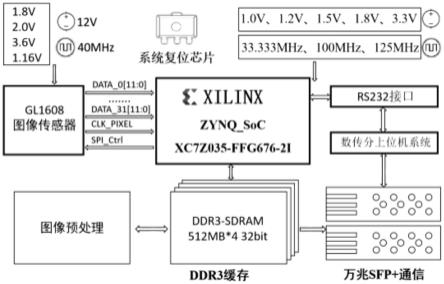

15.图1为本实用新型硬件电路架构结构示意图;

16.图2为本实用新型时序电路逻辑层次划分图;

17.图3为本实用新型cmos控制器的输入输出数据接口图;

18.图4为本实用新型cmos控制器的输入数据接口图;

19.图5为本实用新型的cmos控制器的输出数据接口图;

20.图6为本实用新型的cmos驱动控制模块状态机;

21.图7为本实用新型的电源芯片电路图;

22.图8为本实用新型的gl1608芯片电路图。

具体实施方式

23.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

24.请参阅图1-8,本实用新型提供一种技术方案:一种高速长线列cmos探测器成像电

路,包括图像传感器、驱动电路和数传电路,所述图像传感器分别与驱动电路和数传电路电性连接,所述图像传感器包括内部含有128寄存器的gl1608芯片;如图8所示,gl1608芯片的内部集成了采样电路、放大电路、数模转换电路、行列像素转移等多个功能模块,每个模块都需要提供单独的电源和偏置驱动。目前常用的电源芯片有dc-dc和ldo两种,它们的特点与区别有:dc-dc是将固定电压范围的直流电源变换其他固定电压直流电源的装置,开关型电源虽然在转换效率上的提升明显,但也带来了较大输出纹波的问题,从而导致了噪声、emi、负载响应较差等问题;ldo是一种只能使用在输出电压小于输入电压应用环境中的低压差线性稳压器,能提供负载电流以保证输出电压稳定。这种电压变换器的优点是噪声低和纹波较小。与dc-dc相比,ldo芯片的噪声更小。由于图像传感器对噪声非常敏感,外部噪声的提高会影响cmos成像质量,因此采用tps74801ldo电源芯片作为gl1608芯片的电源。通过调节对应的输入输出电阻使其输出不同的电压,并且加上旁路电容进行解耦。控制信号由spi_clk,spi_read与spi_sync组成,由此定义spi数据传输协议。gl1608芯片内部光电转换电路将采集到的光信号转换为模拟电信号,再通过adc将模拟电信号转换为数字信号,最后通过电平转换电路将数字信号转换为lvds信号输出。由于zynq-7035的单端i/o口输出信号为ttl电平,所以检测器的输入控制信号端口可以直接连接到bank4引脚上。32对lvds图像数据接口和1对lvds参考时钟接口直接连接到zynq-7035的hr-bank2的lvds引脚上。

25.所述驱动电路包括探测器外围电路和按照cmos探测器启动顺序要求依次作用于时钟、复位、电源使能和驱动spi总线驱动器对cmos进行寄存器配置、控制cmos探测器帧频和积分时间的时序电路,所述探测器外围电路与时序电路电性连接;所述数传电路包括大容量缓存的数据缓存电路、数字图像处理电路和高速信号传输电路,所述数字图像处理电路分别与数据缓存电路和高速信号传输电路电性连接;

26.所述时序电路包括用于对用户输入信息进行逻辑计算的积分控制电路、控制探测器扫描行频的帧频控制电路和寄存器配置电路,所述积分控制电路与帧频控制电路均与寄存器配置电路电性连接,时序电路需要将各部分功能模块划分开来,将系统分为若干个二级单元,然后把各个二级单元划分为下一级的基本单元,直到能够使用基本模块或者ip核为止。并且要对每个模块的输入输出接口和资源进行评估,在顶层文件中例化子模块时,需要匹配所有接口的数据传输速率和数据位宽,其逻辑层次划分如图2所示。它由如下几个模块组成;cmos探测器启动顺序要求依次作用于时钟,复位,电源使能和驱动spi总线驱动器对cmos进行寄存器配置,控制cmos探测器的帧频和积分时间。cmos的启动顺序如图3所示。时序电路主要包括配置寄存器、控制积分、帧频及触发控制等功能。输入输出接口包括时钟信号,复位信号,spi接口信号,时序控制信号,ddr3-sdram读写控制信号,lvds数据通道。它的作用主要是通过主状态机,按照顺序实现了cmos探测器的启动和图像数据的接收。cmos控制器的输入输出数据接口及其含义如图4和图5所示。cmos驱动控制模块状态机如图6所示,它是核心处理板zynq的主状态机。idle:初始状态。复位就进入power_up状态。power_up:数字电源,clk_cmos,rst_cmos,模拟电源按顺序变化。这些都变化后,进入reg_config状态。reg_config:向上位机索要配置数据,配置数据上传后,通过spi总线对cmos进行读写操作。所有寄存器配置好后进入training状态。training:配置完成后,cmos图像输出通道传来训练数据,对训练数据进行字对齐训练。对齐好后就进入working状态。working:字对齐训练完成后,帧频及触发控制模块开始工作,产生周期性的触发脉冲。power_down:cmos

寄存器设置为standby状态,之后依次关闭电源。

27.帧频及触发控制设计过程如下,一个计数器在训练数据完成字对齐之后,从0开始自增计数。计到一个固定的数后复位,再自增,如此循环往复。一个周期代表一帧的周期。上位机通过串口配置传入一个值,该值代表积分时间。当计数器为0时,产生触发信号上升沿,当计数器等于该值时,产生触发信号下降沿。如此,可以产生符合帧频和积分时间的触发信号。这个信号传递给cmos探测器,可以控制它的帧频和积分时间。只有在字对齐训练完成后,计数器才开始自增-》复位循环。当计数器为0时,trig_out为1,当计数器的高16位等于length_integration时,trig_out为0。

28.所述寄存器配置电路包括计数器、将串行输入的1bit数字信号不断地缓存进一个12bit移位寄存器的串并转换电路、将串转并得到的数据与正确数据进行对比的数据对齐电路、控制计数器保持或计数的触发脉冲产生电路和将外部信号保存在内部寄存器中的锁存器,所述计数器与串并转换电路电性连接,所述串并转换电路与数据对齐电路电性连接,所述数据对齐电路与触发脉冲产生电路电性连接,所述触发脉冲产生电路与锁存器电性连接。

29.帧频控制电路由用户输入信息,通过spi口写入cmos探测器内部寄存器,控制探测器扫描行频;积分控制电路用于对用户输入信息进行逻辑计算,当积分控制指令下发时,计算积分时间,计数器开始计数,当到达指定计数值时,逻辑电路发出指令,通过触发脉冲产生电路生成的触发脉冲,命令计数器停止计数,并且计数器清零;触发脉冲产生电路包括开关阵列和逻辑运算模块,所述触发脉冲产生电路生成的触发脉冲信号反馈到计数器使能端,控制计算器保持或计数;所述串并转换电路将串行输入的1bit数字信号不断地缓存进一个12bit移位寄存器。当移位寄存器满的时候,将该寄存器中的数字信号的值发送给数据对齐电路;所述数据对齐电路主状态机进入字对齐训练后,拉动“sync”高,然后探测器输出接口将不断连续输出训练字。训练过程中将串转并得到的数据和正确数据进行对比,若不正确,则移动采样窗口,直到得到正确数据;锁存器,当外部信号来临时,锁存器在pulse信号的控制下,将外部信号保存在内部寄存器中。

30.所述探测器外围电路包括电源电路、偏置电路和外部数字接口电路,所述电源电路分别与图像传感器和偏置电路电性连接,所述偏置电路与外部数字接口电路电性连接,所述外部数字接口电路与时序电路电性连接。

31.所述电源电路包括电源芯片,如图7所示,所述电源芯片设置为tps74801ldo电源芯片,所述电源芯片的七脚连接有cc2,所述cc2的一端与电源芯片一脚之间连接有cc1,所述电源芯片的六脚与八脚之间连接有rc2,所述电源芯片的八脚与九脚之间连接有rc1、所述电源芯片的十一脚与九脚之间连接有cc3。

32.所述数据缓存电路包括ddr3-sdram芯片,所述ddr3-sdram芯片含有四个512mb内存和32bit位宽,当帧触发信号出现下降沿,代表cmos积分阶段结束,每个通道往外输出1024字节图像数据。对应的,外部电路要把图像数据写入ddr3-sdram中。同时给数据赋予正确的地址,每个像素点有三个坐标值,分别是第几行,第几通道,在该行该通道中第几个像素。已知ddr3-sdram的地址位有16位,因此(cnt_line,cnt_channel,cnt_pix_in_line)三个坐标值(计数器)的拼接可以作为地址。缓存一帧后进行数据处理,并等待下一帧数据的到来。

33.所述数字图像处理电路包括型号为xc7z035-ffg676-21的图像处理器,所述图像处理器分别与图像传感器和ddr3-sdram芯片连接,数字图像处理电路采用线性插值算法还原rgb,插入像素值的颜色分量与该像素周围邻近像素呈线性关系,使用的线性传感器使用两列像素,每列像素被分成16列来读取lvds;以一个2

×

2sub-module为例,为了使四个移位寄存器中的值同时被2

×

2的值sub-module存储,添加了移位寄存器作为缓冲,移位寄存器的长度等于一行中包含的像素的数量传感器图像。定义4个8位寄存器line11,line12,line21,line22分别存储两个输入端口的数据。该数字图像处理电路输出每个像素rgb值为输入bayer数据进行线性插值后r,g,b三个分量的和,通过线性插值的方法,使得灰度像素转化为真彩色,发送至高速信号传输电路。

34.所述高速信号传输电路包括万兆以上的以太网传输器和上位机,所述以太网传输器与上位机电性连接,所述上位机通过rs232接口与数据处理器连接,高速信号传输电路以sfp+光模块作为数据传输接口,udp协议由于其控制选项少,所以在数据传输过程中延迟小,数据传输效率高。该高速信号传输电路的功能是实现硬件平台与上位机的通信,将未压缩的图像数据发送给上位机,并接收上位机的指令进行相应的处理。由于数据是单向传输,数据量大,可靠性要求不高,所以采用udp传输协议。

35.尽管已经示出和描述了本实用新型的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本实用新型的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本实用新型的范围由所附权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1