一种HART信号处理方法、装置、设备及存储介质与流程

本发明涉及信息通信领域,特别涉及一种hart信号处理方法、装置、设备及存储介质。

背景技术:

1、hart(highway addressable remote transducer,可寻址远程传感器高速通道的开放通信协议)通信是一种基于hart协议,采用半双工的通信方式,在现有模拟信号传输线上实现数字信号通信的通信方式,属于模拟系统向数字系统转变过程中的过渡性产品,采用hart通信可以保证信号与模拟系统间的兼容性。

2、现有技术中hart通信的实现方案一般是采用集成滤波、信号检测、调制、解调及hart信号波形整形等功能的hart器件,加上外围器件一同组成hart电路,用于支持hart协议的现场仪表与控制器中,并且大多数hart通信采用hart调制解调器集成芯片实现,满足hart物理层规范要求,外围添加部分控制电路即可实现。但是现有技术中实现hart通信采用的hart调制解调器成本太高,不利于在大规模应用。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种hart信号处理方法、装置、设备及存储介质,可以在基于fpga芯片设计的调制解调系统中利用基于fpga芯片设计的调制系统实现hart信号的调制,并利用基于fpga芯片设计的解调系统实现hart信号的解调,以实现hart通信,并且利用基于fpga芯片设计的调制解调系统,可以有效控制成本,以实现hart通信的大规模应用。其具体方案如下:

2、第一方面,本技术公开了一种hart信号处理方法,应用于调制解调系统,包括:

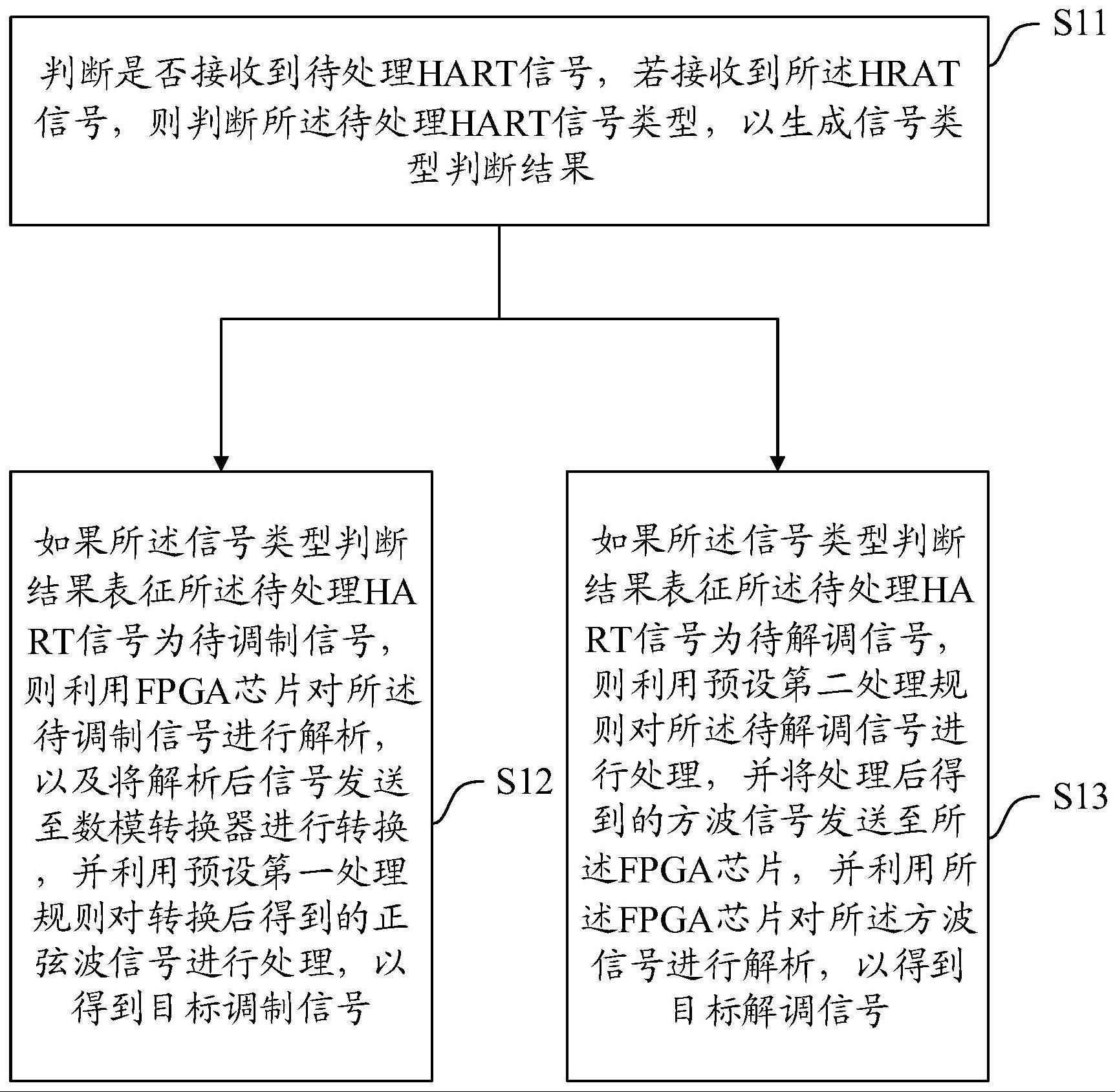

3、判断是否接收到待处理hart信号,若接收到所述hrat信号,则判断所述待处理hart信号类型,以生成信号类型判断结果;

4、若所述信号类型判断结果表征所述待处理hart信号为待调制信号,则利用fpga芯片对所述待调制信号进行解析,以及将解析后信号发送至数模转换器进行转换,并利用预设第一处理规则对转换后得到的正弦波信号进行处理,以得到目标调制信号;

5、若所述信号类型判断结果表征所述待处理hart信号为待解调信号,则利用预设第二处理规则对所述待解调信号进行处理,并将处理后得到的方波信号发送至所述fpga芯片,并利用所述fpga芯片对所述方波信号进行解析,以得到目标解调信号。

6、可选的,所述利用fpga芯片对所述待调制信号进行解析,以及将解析后信号发送至数模转换器进行转换,并利用预设第一处理规则对转换后得到的正弦波信号进行处理,以得到目标调制信号之前,还包括:

7、判断是否接收到目标通信指令,若接收到所述目标通信指令,则基于所述目标通信指令在所述fpga芯片内生成第一数据单元与第二数据单元;所述第一数据单元为存储频率为第一频率的信号的数据单元,所述第二数据单元为存储频率为第二频率的信号的数据单元。

8、可选的,所述利用fpga芯片对所述待调制信号进行解析,以及将解析后信号发送至数模转换器进行转换,包括:

9、判断所述待调制信号的频率,若所述待调制信号频率为所述第一频率,则将所述待调制信号存储至所述第一数据单元,若所述待调制信号频率为所述第二频率,则将所述待调制信号存储至所述第二数据单元;

10、利用所述fpga芯片对所述第一数据单元或所述第二数据单元中存储的所述待调制信号进行解析,并利用串行外设接口将所述解析后信号发送至数模转换器;

11、基于所述数模转换器对所述解析后信号进行转换,以得到与所述解析后信号对应的正弦波信号。

12、可选的,所述利用所述fpga芯片对所述第一数据单元或所述第二数据单元中存储的所述待调制信号进行解析,包括:

13、利用所述fpga芯片中的相位控制字、频率控制字、相位累加器、波形存储器对所述第一数据单元或所述第二数据单元中存储的待调制信号进行直接数字频率合成解析处理,以得到所述解析后信号。

14、可选的,所述利用预设第一处理规则对转换后得到的正弦波信号进行处理,以得到目标调制信号,包括:

15、利用预设隔直流电容对所述正弦波信号进行隔直流处理,并对隔直流后得到的目标隔直流信号进行降压扩流处理,以得到目标调制信号。

16、可选的,所述利用预设第二处理规则对所述待解调信号进行处理,并将处理后得到的方波信号发送至所述fpga芯片,包括:

17、利用所述预设隔直流电容以及过零比较器对所述待解调信号进行处理,以得到所述方波信号,并将所述方波信号发送至所述fpga芯片。

18、可选的,所述利用所述fpga芯片对所述方波信号进行解析,以得到目标解调信号,包括:

19、对所述方波信号进行高低电平宽度检测,并对进行所述高低电平宽度检测后得到的目标检测信号进行宽度解析,以得到目标解调信号。

20、第二方面,本技术公开了一种hart信号处理装置,应用于调制解调系统,包括:

21、信号判断模块,用于判断是否接收到待处理hart信号,若接收到所述hrat信号,则判断所述待处理hart信号类型,以生成信号类型判断结果;

22、信号调制模块,用于如果所述信号类型判断结果表征所述待处理hart信号为待调制信号,则利用fpga芯片对所述待调制信号进行解析,以及将解析后信号发送至数模转换器进行转换,并利用预设第一处理规则对转换后得到的正弦波信号进行处理,以得到目标调制信号;

23、信号解调模块,用于如果所述信号类型判断结果表征所述待处理hart信号为待解调信号,则利用预设第二处理规则对所述待解调信号进行处理,并将处理后得到的方波信号发送至所述fpga芯片,并利用所述fpga芯片对所述方波信号进行解析,以得到目标解调信号。

24、第三方面,本技术公开了一种电子设备,包括:

25、存储器,用于保存计算机程序;

26、处理器,用于执行所述计算机程序以实现如前述的hart信号处理方法。

27、第四方面,本技术公开了一种计算机可读存储介质,用于保存计算机程序,所述计算机程序被处理器执行时实现如前述的hart信号处理方法。

28、本技术中,需要先判断是否接收到待处理hart信号,若接收到所述hrat信号,则判断所述待处理hart信号类型,以生成信号类型判断结果,如果所述信号类型判断结果表征所述待处理hart信号为待调制信号,则利用fpga芯片对所述待调制信号进行解析,以及将解析后信号发送至数模转换器进行转换,并利用预设第一处理规则对转换后得到的正弦波信号进行处理,以得到目标调制信号,如果所述信号类型判断结果表征所述待处理hart信号为待解调信号,则利用预设第二处理规则对所述待解调信号进行处理,并将处理后得到的方波信号发送至所述fpga芯片,并利用所述fpga芯片对所述方波信号进行解析,以得到目标解调信号。由此可见,通过本技术中所述hart信号处理方法,可以在接收到待处理hart信号时,判断所述待处理hart信号的类型,并根据所述待处理hart信号的类型,利用基于fpga芯片设计的调制解调系统对所述待处理hart信号进行相应的调制或解调处理,以便基于fpga芯片设计的调制解调系统实现hart通信。这样一来,利用基于fpga芯片设计的调制解调系统实现hart通信,可以利用fpga芯片成本更低的特性,使实现hart通信的成本可控,以便实现hart通信的大规模应用。

- 还没有人留言评论。精彩留言会获得点赞!