一种低失真PAM-4光发射器

本发明涉及光发射器,更具体地说,它涉及一种低失真pam-4光发射器。

背景技术:

1、光纤网络凭借其高容量、低损耗、低成本的优势,被广泛用于数据中心、接入网、城域网等通信设施的建设中。光发射器是光纤网络的重要组成部分,它对前端通信模组输出的电信号进行电压-电流转换、摆幅放大、预失真处理,从而驱动激光器发射出低失真的光信号。激光器的非线性特性可分为静态非线性和动态非线性,前者指激光器的输入电流和输出光功率的大小呈非线性关系,后者指激光器的带宽随偏置电流的变化而变化。当用pam-4信号驱动激光器时,静态非线性特性会使发射出的光信号的三个子眼高度不一致,其中上眼的高度最小、下眼的高度最大,称此现象为幅度失真。随着信号速率增大,激光器的动态非线性特性会使此幅度失真现象进一步加剧。

2、传统的光发射器芯片通过将最低有效位(lsb,least significant bit)码流和最高有效位(msb,most significant bit)码流相加的方式得到pam-4信号,因此光信号上眼的高度和下眼的高度相互耦合、无法独立调节,难以解决激光器的静态非线性问题。传统的均衡方式亦无法应对激光器的动态非线性问题。

技术实现思路

1、本发明要解决的技术问题是针对现有技术的上述不足,本发明的目的是提供一种低失真pam-4光发射器。

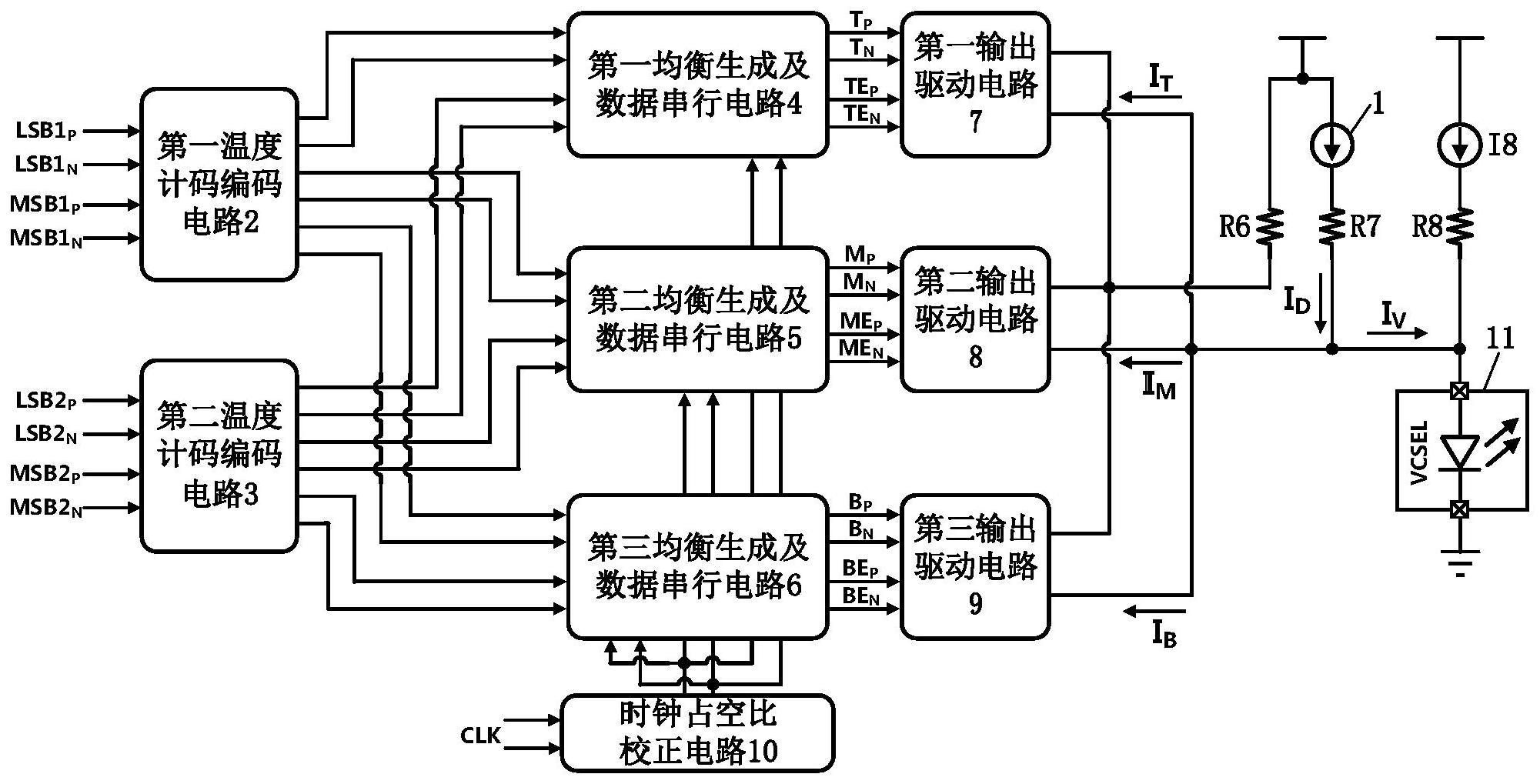

2、本发明技术方案是:一种低失真pam-4光发射器,包括偏置电流源,还包括第一温度计码编码电路、第二温度计码编码电路、第一均衡生成及数据串行电路、第二均衡生成及数据串行电路、第三均衡生成及数据串行电路、第一输出驱动电路、第二输出驱动电路、第三输出驱动电路、时钟占空比校正电路;

3、第一组四路半速率不归零差分信号输入第一温度计码编码电路得到第一组六路半速率一元nrz差分信号,第一组六路半速率一元nrz差分信号平均分为三组并分别输入第一均衡生成及数据串行电路、第二均衡生成及数据串行电路、第三均衡生成及数据串行电路;

4、第二组四路半速率不归零差分信号输入第二温度计码编码电路得到第二组六路半速率一元nrz差分信号,第二组六路半速率一元nrz差分信号平均分为三组并分别输入第一均衡生成及数据串行电路、第二均衡生成及数据串行电路、第三均衡生成及数据串行电路;

5、时钟占空比校正电路分别输出控制信号给第一均衡生成及数据串行电路、第二均衡生成及数据串行电路、第三均衡生成及数据串行电路;

6、第一均衡生成及数据串行电路输出第一组全速率的主抽头和均衡抽头nrz差分信号给第一输出驱动电路,第二均衡生成及数据串行电路输出第二组全速率的主抽头和均衡抽头nrz差分信号给第二输出驱动电路,第三均衡生成及数据串行电路输出第三组全速率的主抽头和均衡抽头nrz差分信号给第三输出驱动电路;

7、第一输出驱动电路输出第一电流信号,第二输出驱动电路输出第二电流信号,第三输出驱动电路输出第三电流信号,偏置电流源的输出电流将第一电流信号、第二电流信号和第三电流信号减去后得到pam-4格式的第四电流信号,第四电流信号输入至激光器以驱动其发出pam-4格式的光信号。

8、作为进一步地改进,第一温度计码编码电路、第二温度计码编码电路的结构相同,第一温度计码编码电路包括第一非门、第二非门、第三非门、第四非门、第五非门、第六非门、第七非门、第一与非门、第二与非门、第一或非门、第二或非门;第一非门的输出端分别连接第二或非门的第一输入端、第五非门的输入端、第二与非门的第一输入端,第一或非门的第一输入端分别连接第三非门的输入端、第一与非门的第一输入端,第一或非门的第二输入端连接第一与非门的第二输入端,第一或非门的输出端连接第四非门的输入端,第二非门的输出端分别连接第二或非门的第二输入端、第二与非门的第二输入端,第三非门的输出端连接第六非门的输入端,第一与非门的输出端连接第七非门的输入端,第一非门的输入端、第一或非门的第一输入端、第一或非门的第二输入端、第二非门的输入端作为第一温度计码编码电路的输入端,第二或非门的输出端、第四非门的输出端、第五非门的输出端、第六非门的输出端、第二与非门的输出端、第七非门的输出端作为第一温度计码编码电路的输出端。

9、进一步地,第一均衡生成及数据串行电路、第二均衡生成及数据串行电路、第三均衡生成及数据串行电路的结构相同,第一均衡生成及数据串行电路包括第一锁存器、第二锁存器、第三锁存器、第四锁存器、第一时钟延时调节电路、第二时钟延时调节电路、第三时钟延时调节电路、第四时钟延时调节电路、第一二比一串行器、第二二比一串行器,第一锁存器、第二锁存器的输出端连接第一二比一串行器的输入端,第三锁存器、第四锁存器的输出端连接第二二比一串行器的输入端,第二时钟延时调节电路的输出端连接第一锁存器、第二锁存器的控制端,第二时钟延时调节电路的输出端通过第四时钟延时调节电路连接第一二比一串行器的控制端,第一时钟延时调节电路的输出端连接第三锁存器、第四锁存器的控制端,第一时钟延时调节电路的输出端通过第三时钟延时调节电路连接第二二比一串行器的控制端,第一锁存器、第二锁存器、第三锁存器、第四锁存器的输入端作为第一均衡生成及数据串行电路的输入端,第一二比一串行器、第二二比一串行器的输出端作为第一均衡生成及数据串行电路的输出端。

10、进一步地,第一二比一串行器、第二二比一串行器的结构相同,第一二比一串行器包括第一电阻、第二电阻、第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管、第八晶体管、第九晶体管、第十晶体管、第十一晶体管、第十二晶体管,第一电阻、第二电阻的一端以及第三晶体管、第六晶体管、第九晶体管、第十二晶体管的源极连接供电端,第一电阻的另一端作为第一二比一串行器的第一输出端,并连接第二晶体管、第五晶体管的漏极,第二晶体管的源极连接第一晶体管、第三晶体管的漏极,第五晶体管的源极连接第四晶体管、第六晶体管的漏极,第一晶体管的栅极连接第三晶体管的栅极并作为第一二比一串行器的第一输入端,第四晶体管的栅极连接第六晶体管的栅极并作为第一二比一串行器的第二输入端,第二电阻的另一端作为第一二比一串行器的第二输出端,并连接第八晶体管、第十一晶体管的漏极,第八晶体管的源极连接第七晶体管、第九晶体管的漏极,第十一晶体管的源极连接第十晶体管、第十二晶体管的漏极,第七晶体管的栅极连接第九晶体管的栅极并作为第一二比一串行器的第三输入端,第十晶体管的栅极连接第十二晶体管的栅极并作为第一二比一串行器的第四输入端,第二晶体管、第五晶体管、第八晶体管、第十一晶体管的栅极作为时钟信号输入端,第一晶体管、第四晶体管、第七晶体管、第十晶体管的源极连接共地端。

11、进一步地,第一时钟延时调节电路、第二时钟延时调节电路、第三时钟延时调节电路、第四时钟延时调节电路的结构相同,第一时钟延时调节电路包括第一电流源、第二电流源、第三电流源、第十三晶体管、第十四晶体管、第十五晶体管、第十六晶体管,第一电流源、第二电流源的一端以及第十五晶体管、第十六晶体管的源极连接供电端,第一电流源的另一端连接第十五晶体管的漏极、第十三晶体管的漏极、第十六晶体管的栅极,并作为第一时钟延时调节电路的第一输出端,第二电流源的另一端连接第十六晶体管的漏极、第十四晶体管的漏极、第十五晶体管的栅极,并作为第一时钟延时调节电路的第二输出端,第三电流源的一端连接第十三晶体管、第十四晶体管的源极,另一端接地,第十三晶体管、第十四晶体管的栅极分别作为第一时钟延时调节电路的第一输入端、第二输入端。

12、进一步地,第一输出驱动电路、第二输出驱动电路、第三输出驱动电路的结构相同,第一输出驱动电路包括第十七晶体管、第十八晶体管、第十九晶体管、第二十晶体管、第二十一晶体管、第二十二晶体管、第二十三晶体管、第二十四晶体管、第三电阻、第四电阻、四个第五电阻、第一电容、第二电容、第四电流源、第五电流源、第六电流源、第七电流源,第十七晶体管的漏极连接第二十晶体管的漏极,并作为第一输出驱动电路的第一输出端,第十八晶体管的漏极连接第十九晶体管的漏极连接,并作为第一输出驱动电路的第二输出端,第十七晶体管的栅极通过两个第五电阻连接第十八晶体管的栅极,第十九晶体管的栅极通过两个第五电阻连接第二十晶体管的栅极,两个第五电阻之间的连接线设有偏置电压端,第十七晶体管的源极连接第二十一晶体管的漏极,第十八晶体管的源极连接第二十二晶体管的漏极,第十九晶体管的源极连接第二十三晶体管的漏极,第二十晶体管的源极连接第二十四晶体管的漏极,第二十一晶体管的源极连接第三电阻的一端、第一电容的一端、第四电流源的一端,第二十二晶体管的源极连接第三电阻的另一端、第一电容的另一端、第五电流源的一端,第二十三晶体管的源极连接第四电阻的一端、第二电容的一端、第六电流源的一端,第二十四晶体管的源极连接第四电阻的另一端、第二电容的另一端、第七电流源的一端,第四电流源、第五电流源、第六电流源、第七电流源的另一端接地,第二十一晶体管、第二十二晶体管、第二十三晶体管、第二十四晶体管的栅极分别作为第一输出驱动电路的四个输入端。

13、进一步地,时钟占空比校正电路包括第一反相器、第二反相器、第三反相器、第四反相器、第五反相器、第六反相器、第七反相器、第八反相器、第九反相器、第十反相器、第十一反相器、第十二反相器,第一反相器依次串接第二反相器、第三反相器、第四反相器,第九反相器依次串接第十反相器、第十一反相器、第十二反相器,第一反相器的输出端通过第五反相器连接第十二反相器的输入端、第七反相器的输入端、第八反相器输出端,第九反相器的输出端通过第六反相器连接第四反相器的输入端、第七反相器的输出端、第八反相器输入端,第一反相器的输入端、第九反相器的输入端作为时钟占空比校正电路的时钟信号输入端,第四反相器的输出端、第十二反相器的输出端作为时钟占空比校正电路的控制信号输出端。

14、有益效果

15、本发明与现有技术相比,具有的优点为:

16、本发明通过将lsb码流和msb码流转化为三路一元码流的方式,将光信号上眼、中眼和下眼之间的关系解耦,能够独立调节三个子眼的高度,从而可以解决由激光器静态非线性特性引起的幅度失真的问题。此外,通过对每路一元码流进行独立的均衡处理,能够使得激光器在四种pam4电平下的带宽接近一致,从而缓解激光器的动态非线性问题。

- 还没有人留言评论。精彩留言会获得点赞!