双通道自动化测试设备的制作方法

本发明涉及自动测试设备,特别涉及一种双通道自动化测试设备。

背景技术:

1、目前关于接收机测试方法主要为手动测试,其测试的方法相当繁琐,部分测试内容在不同条件下也需要重复测试。甚至于批量生产时,需要投入大量的人力物力,费时费力。

技术实现思路

1、本发明提供了一种双通道自动化测试设备,采用相互连接的通用仪器、控制机箱和模块夹具自动运行测试,自动输出报表,结构简单,便于搭建测试,省时省力。

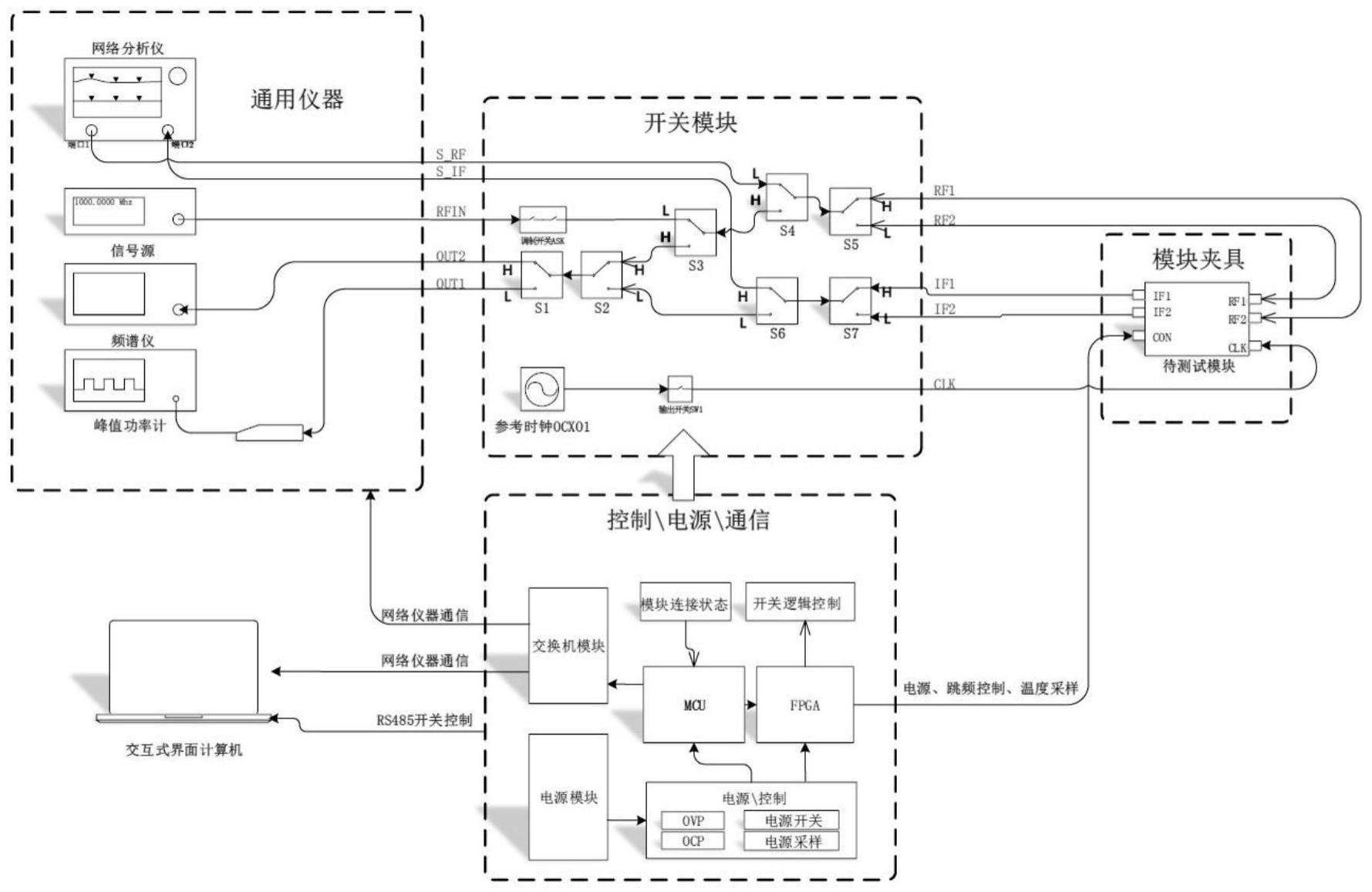

2、本发明提供了一种双通道自动化测试设备,包括通用仪器、控制机箱和模块夹具,所述控制机箱包括开关模块、电源供电及通信控制电路,所述开关模块分别连接所述通用仪器、模块夹具、电源供电及通信控制电路,所述电源供电及通信控制电路还连接所述模块夹具和通用仪器,所述电源供电及通信控制电路还连接交互式界面计算机,所述模块夹具用于承载并连接被测模块;

3、所述电源供电及通信控制电路包括mcu、fpga、交换机模块、电源\控制模块和电源模块,所述mcu分别连接所述交换机模块、fpga、电源\控制模块,所述电源\控制模块分别连接所述电源模块、fpga,fpga连接模块夹具,用于进行开关逻辑控制,所述交换机模块连接所述通用仪器和交互式界面计算机;

4、所述控制机箱提供被测模块所需要的射频测试信号、低频控制信号、电源,并通过射频开关模组实现各种信号方向的控制,配合所述通用仪器以实现各电性能指标的自动测试、数据收集和分析。

5、进一步地,所述开关模块具有多个输入输出接口,包括s_rf、s_if、rfin、out2、out1、clk、if1中频输入、if2中频输入、rf1射频输出、rf2射频输出;所述模块夹具具有多个输入输出接口,包括if1、if2、con、rf1、rf2、clk;

6、所述开关模块的s_rf、s_if口用于连接所述网络分析仪,所述开关模块的rfin口用于连接所述信号源,所述开关模块的out2口用于连接所述频谱仪,所述开关模块的out1口用于连接峰值功率计,所述开关模块的clk口用于连接所述模块夹具的clk口,所述开关模块的if1中频输入口连接所述模块夹具的if1口,所述开关模块的if2中频输入口连接所述模块夹具的if2口,所述开关模块的rf1射频输出口连接所述模块夹具的rf2口,所述开关模块的rf2射频输出口连接所述模块夹具的rf1口,所述模块夹具的con口连接fpga。

7、进一步地,所述模块夹具还包括射频电缆引出口if1、if2,所述被测模块具有if1口、if2口,所述被测模块的if1口连接所述模块夹具的射频电缆引出口if1,所述被测模块的if2口连接所述模块夹具的射频电缆引出口if2。

8、进一步地,所述通用仪器包括网络分析仪、信号源、频谱仪和峰值功率计,所述网络分析仪完成所述被测模块输出输入口的驻波测量,并通过所述开关模块实现通道切换;所述信号源通过开关模块切换rf1、rf2产生射频测试信号;所述频谱仪通过开关模块选择if1、if2中频信号输入至频谱仪以完成中频幅度测量;所述峰值功率计用于观察脉下工作状态。

9、进一步地,测试所需的电源由所述控制机箱内电源模块产生,并完成电流采样和开关控制,所述被测模块电源电压从夹具端口采样;交互式界面程序在交互式界面计算机中运行,通过网络交换机与通用仪器互联通信,开关模块中通道切换控制与电源控制通过机箱后串口实现通信。

10、进一步地,所述开关模块包括:

11、芯片d1的第一引脚连接电容c1的一端、电阻r2的一端,电容c1的另一端连接电阻r2的另一端并接地,芯片d1的第五引脚连接电阻r36的一端,电阻r36的另一端接地,芯片d1的第十四引脚连接电容c3的一端、电容c2的一端,电容c3的另一端连接电容c2的另一端并接地;

12、芯片u1的第一引脚连接电容c127的一端、芯片u1的第三引脚、电容c258的一端、电容c259的一端、电容c260的一端、电阻r1的一端,电容c127的另一端接地,电阻r1的另一端连接芯片u1的第二引脚和第四引脚,电容c258的另一端连接电容c259的另一端、电容c260的另一端、电容c111的一端、电容c112的一端、电容c97的一端、电容c98的一端并接地,电容c111的另一端连接电感t3的一端、芯片u1的第五引脚、第六引脚、第七引脚、第八引脚,电感t3的另一端连接电容c112的另一端、电容c97的另一端、电容c98的另一端、和芯片y1的第十四引脚,芯片y1的第八引脚连接电容c99的一端、电容c99的另一端连接电阻r89的一端、电阻r87的一端,电阻r89的另一端连接电阻r90的一端并接地,电阻r90的另一端连接电阻r87的另一端、电容c136的一端和sx1,电容c136的另一端连接电阻r66的一端,电阻r66的另一端连接二极管d7的一端,二极管d7的另一端连接电阻r65的一端和电容c135的一端,电容c135的另一端连接电容r65的另一端并接地;

13、芯片u3的第一引脚连接电容c29的一端,电容c29的另一端连接电容c28的一端并接地,电容c28的另一端连接芯片u3的第二引脚,芯片u3的第四引脚连接电容c43的一端,电容c43的另一端连接sx4,芯片u3的第八引脚连接电容c26的一端,电容c26的另一端连接电阻r3的一端,电阻r3的另一端接地,芯片u3的第五引脚连接电容c44的一端,电容c44的另一端连接电容c45的一端,电容c45的另一端连接芯片u6的第三引脚;

14、芯片u6的第一引脚连接电容c19的一端,电容c19的另一端连接电容c18的一端并接地,电容c18的另一端连接芯片u6的第二引脚,芯片u6的第八引脚连接电容c32的一端,电容c32的另一端连接电阻r4的一端,电阻r4的另一端接地,芯片u6的第五引脚连接电容c48的一端,电容c48的另一端连接电容c49的一端,电容c49的另一端连接芯片u8的第八引脚;

15、芯片u8的第五引脚连接电容c55的一端,电容c55的另一端连接电容c73的一端,电容c73的另一端连接芯片u14的第五引脚,芯片u8的第一引脚连接电容c33的一端、电容c14的一端,电容c33的另一端连接电容c14的另一端并接地,芯片u8的第二引脚连接电容c34的一端、电容c15的一端,电容c34的另一端连接电容c15的另一端并接地,芯片u8的第三引脚连接电容c54的一端,电容c54的另一端连接电容c50的一端,电容c50的另一端连接芯片u4的第五引脚;

16、芯片u4的第八引脚连接电容c36的一端,电容c36的另一端连接sx2,芯片u4的第一引脚连接电容c30的一端、电容c13的一端,电容c30的另一端连接电容c13的另一端并接地,芯片u4的第二引脚连接电容c24的一端、电容c10的一端,电容c24的另一端连接电容c10的另一端并接地,芯片u4的第三引脚连接电容c46的一端,电容c46的另一端连接电容c47的一端,电容c47的另一端连接芯片u5的第三引脚;

17、芯片u5的第一引脚连接电容c17的一端、电容c11的一端,电容c17的另一端连接电容c11的另一端并接地,芯片u5的第二引脚连接电容c16的一端、电容c9的一端,电容c16的另一端连接电容c9的另一端并接地,芯片u5的第八引脚连接电容c38的一端,电容c38的另一端连接电容c12的一端,电容c12的另一端连接芯片u2的第三引脚,芯片u5的第五引脚连接电容c51的一端,电容c51的另一端电容c57的一端,电容c57的另一端连接芯片u12的第三引脚;

18、芯片u2的第一引脚连接电容c7的一端、电容c5的一端、电阻r71的一端,电容c7的另一端连接电容c5的另一端并接地,芯片u2的第二引脚连接电容c6的一端、电容c4的一端,电容c6的另一端连接电容c4的另一端并接地,芯片u2的第八引脚连接电容c8的一端,电容c8的另一端连接sx3,芯片u2的第五引脚连接电容c20的一端,电容c20的另一端连接电阻r5的一端,电阻r5的另一端接地;

19、芯片u12的第一引脚连接电容c53的一端、电容c42的一端,电容c53的另一端连接电容c42的另一端并接地,芯片u12的第二引脚连接电容c52的一端、电容c40的一端,电容c52的另一端连接电容c40的另一端并接地,芯片u12的第八引脚连接电容c56的一端,电容c56的另一端连接电阻r6的一端,电阻r6的另一端接地,芯片u12的第五引脚连接电容c58的一端,电容c58的另一端连接sx5;

20、芯片u14的第一引脚连接电容c67的一端、电容c61的一端,电容c67的另一端连接电容c61的另一端并接地,芯片u14的第二引脚连接电容c66的一端、电容c59的一端,电容c66的另一端连接电容c59的另一端并接地,芯片u14的第三引脚连接电容c78的一端,电容c78的另一端连接电容c77的一端,电容c77的另一端连接芯片u13的第三引脚,芯片u14的第八引脚连接电容c80的一端,电容c80的另一端连接电容c81的一端,电容c81的另一端连接芯片u15的第八引脚;

21、芯片u13第一引脚连接电容c70的一端、电容c62的一端,电容c70的另一端连接电容c62的另一端并接地,芯片u13的第二引脚连接电容c68的一端、电容c60的一端,电容c68的另一端连接电容c60的另一端并接地,芯片u13的第八引脚连接电容c76的一端,电容c76的另一端连接sx6,芯片u13的第五引脚连接电容c79的一端,电容c79的另一端连接sx8;

22、芯片u15的第一引脚连接电容c75的一端、电容c69的一端,电容c75的另一端连接电容c69的另一端并接地,芯片u15的第二引脚连接电容c74的一端、电容c64的一端,电容c74的另一端连接电容c64的另一端并接地,芯片u15的第三引脚连接电容c83的一端,电容c83的另一端连接电容c84的一端,电容c84的另一端连接芯片u16的第三引脚;

23、芯片u16的第一引脚连接电容c72的一端、电容c65的一端,电容c72的另一端连接电容c65的另一端并接地,芯片u16的第二引脚连接电容c71的一端、电容c63的一端,电容c71另一端连接电容c63的另一端并接地,芯片u16的第八引脚连接电容c82的一端,电容c82的另一端连接sx7,芯片u16的第五引脚连接电容c86的一端,电容c86的另一端连接sx9;

24、芯片u17的第一引脚连接芯片u17的第二十引脚、电容c87的一端、电容c88的一端、电容c89的一端、电容c90的一端,电容c87的另一端连接电容c88的另一端、电容c89的另一端、电容c90的另一端并接地,芯片u17的第二引脚连接电阻r56,芯片u17的第二引脚连接电阻r57,芯片u17的第二引脚连接电阻r58,芯片u17的第二引脚连接电阻r59,芯片u17的第二引脚连接电阻r60,芯片u17的第二引脚连接电阻r61,芯片u17的第二引脚连接电阻r62。

25、本发明的有益效果为:

26、本发明的控制机箱连接模块夹具,模块夹具承载并连接接收机的被测模块,控制机箱提供被测模块所需要的射频测试信号、低频控制信号、电源,并通过射频开关模组实现各种信号方向的控制,配合所述通用仪器以实现各电性能指标的自动测试、数据收集和分析,能够自动运行测试,自动输出报表,结构简单,便于搭建测试,省时省力。

- 还没有人留言评论。精彩留言会获得点赞!