基于ARM架构的高精度时钟同步方法及系统与流程

本发明涉及分布式系统时钟同步领域,具体地,涉及基于arm架构的高精度时钟同步方法及系统,更为具体地,涉及一种arm架构主节点产生基准时间修正从节点时钟的同步技术。

背景技术:

1、在工业自动化和物联网等领域中,需要分布式系统中多传感器和执行器协同工作,与多节点数据通信和融合处理。然而多源异构的通信接口具有不同的电气特性和传输性能,往往导致数据的不同步,存在碰撞、延迟等问题,影响整体系统的实时性和运行性能。

2、专利文献cn112653532a(申请号202011433225.8)公开了一种时钟同步的方法、装置和系统。其中,该方法包括:确定视频输出节点的类型,其中,类型包括:主节点和从节点;依据预设协议对从节点与主节点进行时钟同步;通过定时器对时钟同步后的主节点和从节点输出的时钟信号进行修正。该发明没有选用没有选定高精度时钟源与配套的高精度计时方法。

3、文献“高精度计算机网络时钟同步技术的研究,北京化工大学”讨论了时钟源的模型和同步机制,并介绍了网络上应用最为广泛的网络时间协议—困次的模型和工作原理,然后给出了协议中使用的时间偏移计算算法时间过滤算法、选择算法和时钟合并算法自行开发了基于过滤、选择、合并算法的实验软件平台,并通过该平台的数据采集分析了这些算法的实现效果,并对时钟同步的精度进行了深入的讨论,提出了基于时钟服务器的改进方案。但该文献没有选定高精度时钟源与配套的高精度计时方法。

4、文献“基于arm的分布式测试系统时钟同步研究及实现”通过引入ptp精密时间协议并分析其工作原理,基于arm(stm32f407)芯片及其相关的外围电路设计了时钟同步与触发单元(mac层获取硬件时间戳),进而通过相关软件(包括时钟同步软件,tcp/ip协议栈移植等)设计从而实现分布式测试系统的时钟同步。大量相关实验(两时钟节点网线直连,两节点交换机相连,定时触发输出等)结果表明:组网的各时钟同步与触发单元实现了亚微秒级时钟同步精度和精确同步触发功能。该研究方法具有通用性,能够满足一般分布式测试系统同步需求。但该文献没有采用arm架构自带的时钟源,而是自行设计了复杂的时钟源,因此实现方式的代价更高。

5、本发明基于arm架构提供一种高精度的软件时钟同步方法,解决了多源异构通信接口的时钟同步问题。

技术实现思路

1、针对现有技术中的缺陷,本发明的目的是提供一种基于arm架构的高精度时钟同步方法及系统。

2、根据本发明提供的一种基于arm架构的高精度时钟同步方法,包括:

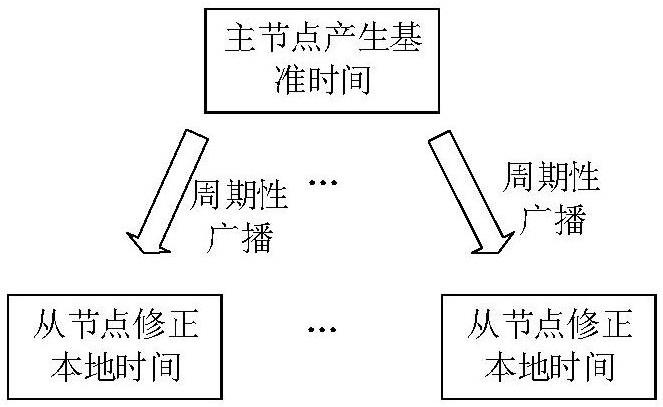

3、步骤s1:主节点产生基准时间,并以周期的时间间隔向等待时间同步的从节点广播基准时间;

4、步骤s2:从节点获取基准时间,并利用基准时间对从节点本地时间进行修正获得从节点本地标准时间。

5、优选地,所述步骤s1采用:

6、步骤s1.1:在第i个周期t起始时刻,当0<i≤1时,则获取系统时间t0,触发步骤s1.2;当i>1时,则读取寄存器pmccntr_el0值,计算周期起始时间ti-1,触发步骤s1.2;

7、步骤s1.2:将寄存器pmccntr_el0置零,计数n置零;

8、步骤s1.3:计数n加一并延时等待t/n时长,其中,n表示本周期的采用次数;

9、步骤s1.4:获取cpu工作频率fin,读寄存器pmccntr_el0值记为vin;

10、步骤s1.5:判断计数n是否小于本周期采样次数n,当计数n小于本周期采样次数n时,则重复触发步骤s1.3至步骤s1.5,直至计数n大于等于本周期采样次数n;

11、步骤s1.6:将n次采样获取的cpu工作频率序列{fi0,fi1,...,fin-1}取倒数{1/fi0,1/fi1,...,1/fin-1},记为{pi0,pi1,...,pin-1};

12、步骤s1.7:将{pi0,pi1,...,pin-1}与寄存器pmccntr_el0值序列{vi0,vi1,...,vin-1}进行积分运算得ti′;

13、步骤s1.8:获取cpu工作频率fin,读取寄存器pmccntr_el0值vin,计算tioffset=(1/fin)*(vin-vin-1)并计算基准时间ti=ti-1+ti′+tioffset;

14、步骤s1.9:将基准时间ti进行广播后重复触发步骤s1.1至步骤s1.9。

15、优选地,所述步骤s1.1采用:获取cpu工作频率fi-1n+1,读寄存器pmccntr_el0值vi-1n+1计算ti-1+(1/fi-1n+1)*(vi-1n+1-vi-1n)重记为ti-1作为本周期起始时间;

16、优选地,所述步骤s2采用:

17、步骤s2.1:记录本次接收的基准时间ti和本地时间tji′;

18、步骤s2.2:取m+1次本地时间tji′与基准时间ti的偏差值θji=tji′-ti,与基准时间ti形成序列{(ti-m,θji-m),...,(ti,θji)};

19、步骤s2.3:基于计算所得{(ti-m,θji-m),...,(ti,θji)}序列,使用最小二乘法计算本节点的时钟漂移率ρji和偏移量bji;

20、步骤s2.4:计算节点的标准时间tji=(1+ρji)*ti+bji+toffseti,其中,toffsetj为本节点调用补偿。

21、优选地,所述步骤s2.3采用:

22、步骤s2.3.1:计算偏差值序列{θji-m,...,θji}的均值oji;

23、步骤s2.3.2:计算基准时间序列{(ti-m,...,ti)}的均值ti;

24、步骤s2.3.3:计算中间量和中间量

25、步骤s2.3.4:若m>0则计算时钟漂移率ρji=tmpji2/tmpji1,偏移量bji=oji-ρji*ti;否则ρji=0,bji=oji。

26、根据本发明提供的一种基于arm架构的高精度时钟同步系统,包括:

27、模块m1:主节点产生基准时间,并以周期的时间间隔向等待时间同步的从节点广播基准时间;

28、模块m2:从节点获取基准时间,并利用基准时间对从节点本地时间进行修正获得从节点本地标准时间。

29、优选地,所述模块m1采用:

30、模块m1.1:在第i个周期t起始时刻,当0<i≤1时,则获取系统时间t0,触发模块m1.2;当i>1时,则读取寄存器pmccntr_el0值,计算周期起始时间ti-1,触发模块m1.2;

31、模块m1.2:将寄存器pmccntr_el0置零,计数n置零;

32、模块m1.3:计数n加一并延时等待t/n时长,其中,n表示本周期的采用次数;

33、模块m1.4:获取cpu工作频率fin,读寄存器pmccntr_el0值记为vin;

34、模块m1.5:判断计数n是否小于本周期采样次数n,当计数n小于本周期采样次数n时,则重复触发模块m1.3至模块m1.5,直至计数n大于等于本周期采样次数n;

35、模块m1.6:将n次采样获取的cpu工作频率序列{fi0,fi1,...,fin-1}取倒数{1/fi0,1/fi1,...,1/fin-1},记为{pi0,pi1,...,pin-1};

36、模块m1.7:将{pi0,pi1,...,pin-1}与寄存器pmccntr_el0值序列{vi0,vi1,...,vin-1}进行积分运算得ti′;

37、模块m1.8:获取cpu工作频率fin,读取寄存器pmccntr_el0值vin,计算tioffset=(1/fin)*(vin-vin-1)并计算基准时间ti=ti-1+ti′+tioffset;

38、模块m1.9:将基准时间ti进行广播后重复触发模块m1.1至模块m1.9。

39、优选地,所述模块m1.1采用:获取cpu工作频率fi-1n+1,读寄存器pmccntr_el0值vi-1n+1计算ti-1+(1/fi-1n+1)*(vi-1n+1-vi-1n)重记为ti-1作为本周期起始时间;

40、优选地,所述模块m2采用:

41、模块m2.1:记录本次接收的基准时间ti和本地时间tji′;

42、模块m2.2:取m+1次本地时间tji′与基准时间ti的偏差值θji=tji′-ti,与基准时间ti形成序列{(ti-m,θji-m),...,(ti,θji)};

43、模块m2.3:基于计算所得{(ti-m,θji-m),...,(ti,θji)}序列,使用最小二乘法计算本节点的时钟漂移率ρji和偏移量bji;

44、模块m2.4:计算节点的标准时间tji=(1+ρji)*ti+bji+toffseti,其中,toffsetj为本节点调用补偿。

45、优选地,所述模块m2.3采用:

46、模块m2.3.1:计算偏差值序列{θji-m,...,θji}的均值oji;

47、模块m2.3.2:计算基准时间序列{(ti-m,...,ti)}的均值ti;

48、模块m2.3.3:计算中间量和中间量

49、模块m2.3.4:若m>0则计算时钟漂移率ρji=tmpji2/tmpji1,偏移量bji=oji-ρji*ti;否则ρji=0,bji=oji。

50、与现有技术相比,本发明具有如下的有益效果:

51、1、本发明主节点利用arm架构自带的高精度pmccntr_el0寄存器作为时钟源,并采用积分算法实现精确计时,简明的提升了周期性基准时间的精度。

52、2、本发明从节点采用统计学方法进行本地时间修正,保证了时种同步的精度。

- 还没有人留言评论。精彩留言会获得点赞!