数据链路的训练方法和通信系统

本技术涉及芯粒,具体涉及一种数据链路的训练方法和通信系统。

背景技术:

1、芯粒技术集成的系统芯片中,由于芯粒与有源转接板内的布线长度和加工工艺参数的失配,会带来信号的延迟偏差,从而使芯粒与有源转接板进行通信时,本应同时到达的一组并行信号(一条主带通路中并行传输的多个信号)的到达时间不一致。因此在系统芯片工作之前,会对芯粒与有源转接板之间的数据链路进行链路训练,以消除延迟偏差,使数据链路能够进行正确的数据通信。

2、现有的链路训练,主要针对串行的时钟-数据流的通信方式,需要对时钟-数据流进行时钟信号提取、字符分隔符以及对数据信号的相位调整,其数据链路的训练过程非常繁琐,导致相位调节电路的规模比较复杂。并且,从时钟-数据流进行时钟信号提取过程,以及对时钟-数据流中的数据信号进行相位调整的过程,均需要较大的功耗,进而使系统芯片的功耗较高,从而影响用户体验。

技术实现思路

1、鉴于此,本技术提供一种数据链路的训练方法和通信系统,用于简化数据链路的训练过程和相位调节电路的规模,以及降低功耗。本技术技术方案如下:

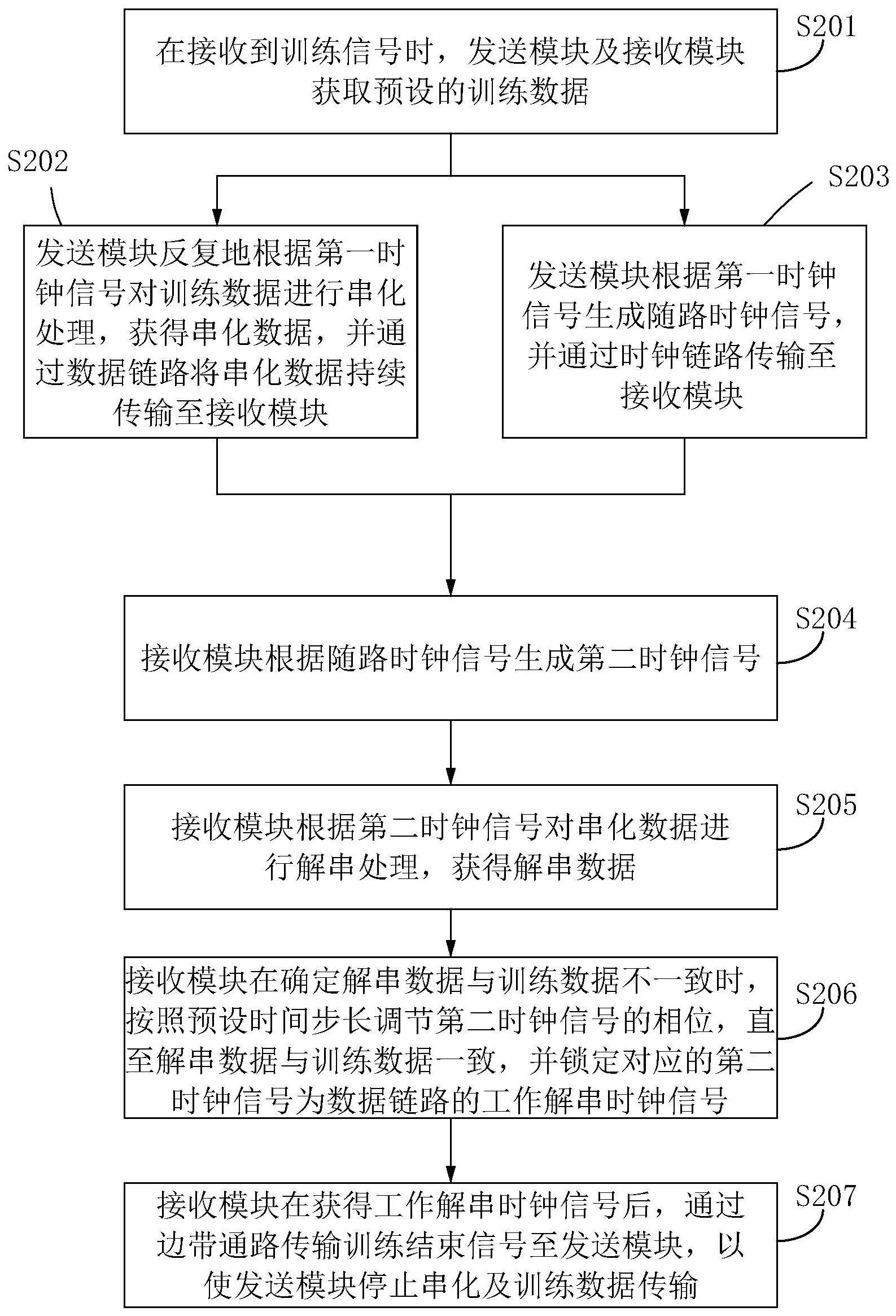

2、本技术第一方面提供一种数据链路的训练方法,应用于芯粒与有源转接板的通信系统,所述通信系统包括发送模块与接收模块,所述发送模块与所述接收模块通过所述数据链路、时钟链路以及边带通路连接;其中,所述训练方法包括:在接收到训练信号时,所述发送模块及所述接收模块获取预设的训练数据;所述发送模块反复地根据第一时钟信号对所述训练数据进行串化处理,获得串化数据,并通过所述数据链路将所述串化数据持续传输至所述接收模块;所述发送模块根据所述第一时钟信号生成随路时钟信号,并通过所述时钟链路传输至所述接收模块;所述接收模块根据所述随路时钟信号生成第二时钟信号;所述接收模块根据所述第二时钟信号对所述串化数据进行解串处理,获得解串数据;所述接收模块在确定所述解串数据与所述训练数据不一致时,按照预设时间步长调节所述第二时钟信号的相位,直至所述解串数据与所述训练数据一致,并锁定对应的所述第二时钟信号为所述数据链路的工作解串时钟信号;所述接收模块在获得所述工作解串时钟信号后,通过所述边带通路传输训练结束信号至所述发送模块,以使所述发送模块停止串化及训练数据传输。

3、在本技术一实施例中,所述训练方法还包括:所述接收模块在确定所述第二时钟信号延迟调节达到预设的边界值且所述解串数据与所述训练数据仍不一致时,通过所述边带通路传输训练失败信号至所述发送模块;所述发送模块按照预设频率步长降低所述第一时钟信号的频率,并返回至所述根据第一时钟信号对所述训练数据进行串化处理的步骤,直至所述解串数据与所述训练数据一致,并锁定对应的所述第一时钟信号为所述数据链路的工作串化时钟信号。

4、在本技术一实施例中,所述训练方法还包括:在训练结束且接收到工作信号时,所述发送模块根据所述工作串化时钟信号对数据进行串化处理,并通过所述数据链路传输至所述接收模块;所述接收模块根据所述工作解串时钟信号对从所述数据链路接收的数据进行解串处理。

5、在本技术一实施例中,所述训练方法还包括:所述发送模块确定所述第一时钟信号调节至最低频率且通过所述边带通路接收到所述训练失败信号时,停止串化及训练数据传输;所述发送模块通过所述边带通路传输训练失败信号至自身的上位控制模块。

6、在本技术一实施例中,所述第二时钟信号为所述随路时钟信号经相位延迟处理的信号;所述按照预设时间步长调节所述第二时钟信号的相位包括:按照所述预设时间步长推迟所述第二时钟信号。

7、本技术第二方面提供一种通信系统,应用于芯粒与有源转接板,所述通信系统包括发送模块与接收模块,所述发送模块与所述接收模块通过数据链路、时钟链路以及边带通路连接;所述发送模块包括:第一控制单元,用于在接收到训练信号时,发送第一训练指令至第一数据获取单元以及时钟产生单元;所述第一数据获取单元,用于在接收到所述第一训练指令时获取预设的训练数据;所述时钟产生单元,用于在接收到所述第一训练指令时生成第一时钟信号;串化单元,用于根据所述第一时钟信号对所述训练数据进行串化处理,获得串化数据;时钟分频单元,用于根据所述第一时钟信号生成随路时钟信号;第一发送单元,用于将所述串化数据持续传输至所述接收模块;第二发送单元,用于将所述随路时钟信号传输至所述接收模块;第一边带通信单元,用于接收训练结束信号并转发至所述第一控制单元,以停止串化及数据传输;所述接收模块包括:第一接收单元,用于接收所述串化数据;第二接收单元,用于接收所述随路时钟信号;相位调节单元,用于根据所述随路时钟信号生成第二时钟信号;解串单元,用于根据所述第二时钟信号对所述串化数据进行解串处理,获得解串数据;第二控制单元,用于在接收到所述训练信号时获取所述训练数据,在确定所述解串数据与所述训练数据不一致时,发送调节指令至所述相位调节单元,在所述解串数据与所述训练数据一致时,锁定对应的所述第二时钟信号为所述数据链路的工作解串时钟信号;所述相位调节单元还用于在接收到所述调节指令时,按照预设时间步长调节所述第二时钟信号的相位;第二边带通信单元,用于在获得所述工作解串时钟信号后发送所述训练结束信号。

8、在本技术一实施例中,所述第一边带通信单元还用于发送所述训练信号至所述第二边带通信单元,以使所述接收模块开始训练。

9、在本技术一实施例中,所述第一发送单元包括第一串化寄存器和第一发送驱动器,所述第二发送单元包括第二串化寄存器和第二发送驱动器,所述第一接收单元包括第一解串寄存器和第一接收驱动器,所述第二接收单元包括第二解串寄存器和第二接收驱动器;所述第一串化寄存器、所述第一发送驱动器、所述第一接收驱动器以及所述第一解串寄存器依次连接;所述第二串化寄存器、所述第二发送驱动器、所述第二接收驱动器以及所述第二解串寄存器依次连接;所述第一串化寄存器及所述第二串化寄存器与所述发送模块的物理端口相邻设置;所述第一解串寄存器及所述第二解串寄存器与所述接收模块的物理端口相邻设置。

10、在本技术一实施例中,所述数据链路包括:所述串化单元、所述第一发送单元、所述第一接收单元以及所述解串单元;所述时钟链路包括:所述时钟产生单元、所述时钟分频单元、所述第二发送单元、所述第二接收单元以及所述相位调节单元;所述边带通路包括:所述第一边带通信单元以及所述第二边带通信单元。

11、在本技术一实施例中,所述第二控制单元还用于在确定所述第二时钟信号延迟调节达到预设边界值且所述解串数据与所述训练数据仍不一致时,通过所述第二边带通信单元传输训练失败信号至所述发送模块;所述第一控制单元还用于控制所述时钟产生单元按照预设频率步长降低所述第一时钟信号的频率,直至所述解串数据与所述训练数据一致,并锁定对应的所述第一时钟信号为所述数据链路的工作串化时钟信号。

12、本技术在对数据链路进行训练时,通过发送模块对训练数据进行串化并持续发送至接收模块,通过接收模块对接收的串化数据进行解串恢复,并在解串数据与训练数据不一致时,不断去调节驱动解串的第二时钟信号,最终获得使解串数据与训练数据一致的解串时钟信号,由于整个训练过程仅需聚焦于调整第二时钟信号的相位的过程,从而使数据链路的训练过程比较简单,从而简化训练控制和相位调节电路的规模,并且,还由于设置时钟链路将随路时钟信号从发送模块传输至接收模块,从而节省了从时钟-数据流中进行时钟信号提取的过程,进而降低数据链路训练的功耗,进而降低芯片功耗,提高用户体验。

- 还没有人留言评论。精彩留言会获得点赞!