一种基于FPGA的万兆以太网接口扩展装置及方法与流程

本发明涉及以太网,尤其涉及一种基于fpga的万兆以太网接口扩展装置及方法。

背景技术:

1、potn设备的基本组成结构如图1所示,主要包括otu线路板、核心交换板、业务接入板,核心交换板与其它各板卡之间通过背板进行互连。业务接入板按业务类型可分为以太网接入板、e1接入板、sdh接入板,其中,以太网接入板实现以太网业务的接入。

2、传统的以太网业务接入方法如图2所示,采用n个phy芯片与核心交换板的以太网交换芯片的n个端口互连,外接的以太网接口与以太网交换芯片的端口一一对应。

3、传统的以太网业务接入方法存在的缺点,由于以太网交换芯片的10m/100m/1000m端口数量有限,可接入的以太网接口数量少,难以满足大规模的以太网业务接入需求;对于每一路以太网业务,每一个phy芯片均存在一组收发双向高速串行信号与以太网交换芯片进行连接,当存在多路以太网业务需要接入时,核心交换板与以太网接入板之间的板间连接信号数量大增,硬件设计难度变大,进一步限制了可接入的以太网接口数量。

技术实现思路

1、本发明的目的在于提供一种基于fpga的万兆以太网接口扩展装置及方法,旨在解决传统以太网业务接入方法,可接入的以太网接口数量少的问题。

2、为实现上述目的,第一方面,本发明提供了一种基于fpga的万兆以太网接口扩展装置,包括以太网交换芯片、fpga和phy芯片,所述以太网交换芯片与所述fpga之间通过万兆以太网接口互连;所述phy芯片与所述fpga之间通过sgmii接口互连;

3、所述以太网交换芯片具有万兆以太网接口,且万兆以太网接口可配置为汇聚链接模式,以太网交换芯片用于以太网数据包的交换,实现以太网数据包的存储转发;

4、所述phy芯片用于实现以太网接口的物理层功能,具备10m/100m/1000m速率自协商的能力,具有sgmii接口;

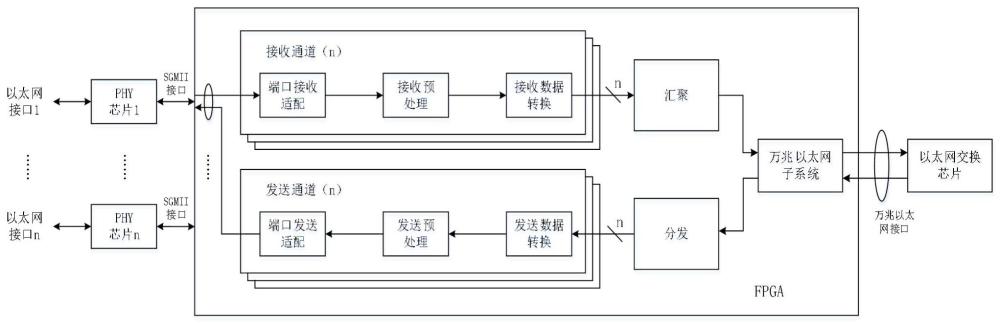

5、所述fpga包括n个接收通道模块、n个发送通道模块、汇聚模块、分发模块和万兆以太网子系统;

6、所述汇聚模块的输入端与n个接收通道模块连接,所述汇聚模块的输出端与万兆以太网子系统连接;

7、所述分发模块的输入端与万兆以太网子系统连接,所述分发模块的输出端与n个发送通道模块连接。

8、所述接收通道模块包括一组依次连接的端口接收适配模块、接收预处理模块和接收数据转换模块;

9、所述端口接收适配模块用于将sgmii接口信号转换为fpga内部的gmii信号,并根据phy芯片反馈的以太网接口速率进行10m/100m/1000m速率适配;

10、所述接收预处理模块将原始数据帧的前导码和crc校验值去除,并添加vlan标签,得到带标签净荷数据帧;

11、所述接收数据转换模块一方面将预处理后的以太网帧数据进行缓存,并做时钟域转换,另一方面,将gmii格式的数据帧转换成axi4-stream帧格式的数据帧;

12、所述发送通道模块包括一组依次连接的发送数据转换模块、发送预处理模块和端口发送适配模块;

13、所述发送数据转换模块一方面将axi4-stream帧格式的数据帧转换成gmii格式的数据帧,另一方面,将分发到该通道的数据进行缓存,并做时钟域转换;

14、所述发送预处理模块将带标签净荷数据帧中的vlan标签去除,并添加前导码和crc校验值恢复成原始数据帧;

15、所述端口发送适配模块用于将fpga内部的gmii信号转换成sgmii接口信号,并根据phy芯片反馈的以太网接口速率进行10m/100m/1000m速率适配;

16、所述原始数据帧包括前导码、目的地址、源地址、类型/长度、数据、填充和校验值;

17、所述带标签净荷数据帧包括目的地址、源地址、vlan标签、类型/长度、数据和填充。

18、所述汇聚模块将来自多个通道的axi4-stream数据帧汇聚成单个axi4-stream数据流输出;

19、所述汇聚模块包括选通逻辑、合路器和axi4数据fifo;

20、所述选通逻辑根据数据缓存非空信号、axi4数据fifo可写入信号和数据帧读取完毕信号控制各接收通道缓存读取进程,产生数据帧读取启动信号,并控制合路器的选通;

21、所述合路器将对应的接收通道数据帧入口与数据流出口连通;

22、所述axi4数据fifo的读时钟为万兆以太网子系统axi4-stream接口时钟;

23、所述axi4数据fifo的写时钟频率为读时钟频率的2倍,使用axi4数据fifo的写时钟作为从各接收通道数据缓存读取数据帧的时钟,可提高数据调度的速率;

24、所述axi4数据fifo已使用空间小于总存储空间的一半时,axi4数据fifo可写入信号有效,否则无效。

25、所述分发模块根据vlan标签将单个axi4-stream数据流分发到多个通道的axi4-stream数据帧输出;

26、所述分发模块包括分路器、数据寄存模块、vlan标签寄存模块和选通逻辑;

27、所述数据寄存模块将axi4-stream数据流进行寄存;

28、所述vlan标签寄存模块对vlan标签进行定位并寄存;

29、所述选通逻辑根据vlan标签控制分路器的选通;

30、所述分路器将axi4-stream数据流入口与对应的axi4-stream数据帧出口连通。

31、所述万兆以太网子系统实现万兆以太网的数据链路层、pcs子层和pma子层的功能;

32、所述万兆以太网子系统包括万兆以太网mac模块和万兆以太网pcs/pma模块;

33、所述万兆以太网mac模块和万兆以太网pcs/pma模块之间通过xgmii接口互连;

34、所述万兆以太网mac模块实现数据成帧及解帧、流量控制和差错检验功能;

35、所述万兆以太网pcs/pma模块实现数据的弹性缓存、64b/66b编解码、数据的加扰及解扰和数据同步功能。

36、第二方面,本发明还提供了一种基于fpga的万兆以太网接口扩展方法,包括sgmii接口至万兆以太网接口方向处理流程、万兆以太网接口至sgmii接口方向处理流程、汇聚模块处理流程、分发模块处理流程。

37、所述sgmii接口至万兆以太网接口方向处理流程包括以下步骤:

38、s101将sgmii接口信号转换为fpga内部的gmii信号;

39、s102将原始数据帧的前导码和crc校验值去除,并添加vlan标签,得到带标签净荷数据帧;

40、s103将gmii格式的数据帧转换成axi4-stream帧格式的数据帧,并做时钟域转换;

41、s104将来自多个接收通道的axi4-stream数据帧汇聚成单个axi4-stream数据流;

42、s105完成万兆以太网的数据流成帧、加扰以及64b/66b编码;

43、s106高速串行接口完成信号的并串转换,将信号发送至物理线路。

44、所述万兆以太网接口至sgmii接口方向处理流程包括以下流程:

45、s201高速串行接口从物理线路中恢复出时钟和数据,并完成信号的串并转换;

46、s202完成万兆以太网的数据同步、解扰、64b/66b解码及数据解帧;

47、s203将单个axi4-stream数据流分解到多个发送通道的axi4-stream数据帧;

48、s204将axi4-stream帧格式的数据帧转换成gmii格式的数据帧,并做时钟域转换;

49、s205将带标签净荷数据帧中的vlan标签去除,并添加前导码和crc校验值恢复成原始数据帧;

50、s206将fpga内部的gmii信号转换成sgmii接口信号。

51、所述汇聚模块处理流程包括以下步骤:

52、s301处于空闲状态时,实时检测是否存在接收通道的数据缓存为非空,如果检测到存在接收通道的数据缓存为非空,则执行s302,否则停留在空闲状态;

53、s302依次检测通道1至通道n的缓存是否为空,对于通道1至通道n-1,如果检测到当前通道缓存为空,则继续检测下一通道,否则进入通道缓存读取进程,通道缓存读取进程结束之后检测下一通道;对于通道n,如果检测到当前通道缓存为空,则返回空闲状态,否则进入通道缓存读取进程,通道缓存读取进程结束之后返回空闲状态;

54、其中,所述通道缓存读取进程包括以下步骤:

55、s303控制合路器将对应的接收通道数据帧入口与数据流出口连通;

56、s304检测到axi4数据fifo可写入信号是否有效,如果检测到axi4数据fifo可写入信号有效,则向选定的接收通道发出数据帧读取启动信号,否则继续等待axi4数据fifo可写入信号有效;

57、s305检测到数据帧读取完毕信号,则执行s306,否则继续等待数据帧读取;

58、s306复位合路器,结束通道缓存读取进程。

59、所述分发模块处理流程包括以下流程:

60、s401处于空闲状态时,实时检测是否存在数据流输入,如果检测到存在数据流输入,执行s402,否则停留在空闲状态;

61、s402启动数据帧写入进程,将输入的数据流进行寄存;

62、s403将vlan标签进行定位并寄存;

63、s404依据选通策略选定该数据帧的发送通道,并控制分路器将对应发送通道的数据帧出口与数据流入口连通,所述选通策略为,当vlan标签的tpid字段为0x8100时,记录vlan标签的vid字段的值为m,根据vid字段与axi4-stream数据帧的发送通道之间的对应关系选定第n路发送通道输出该数据帧;当vlan标签的tpid字段不是0x8100时,丢弃该数据帧;

64、s405实时检测数据帧输出是否结束,如检测到数据帧输出结束,则执行s406,否则继续等待数据帧输出;

65、s406复位分路器,结束数据帧写入进程,返回空闲状态。

66、本发明的一种基于fpga的万兆以太网接口扩展装置及方法,利用vlan标签对多个通道的以太网数据帧进行标识,单个万兆以太网链路可扩展成多个10m/100m/1000m以太网虚拟通道,可将单个万兆以太网接口扩展至多个10m/100m/1000m以太网接口,可满足大规模的以太网业务接入需求;对于单个万兆以太网接口,fpga只存在一组收发双向的高速串行信号与以太网交换芯片进行连接,从而大大减少了核心交换板与以太网接入板之间的板间连接信号数量,降低了硬件设计难度,增加了可接入的以太网接口数量。

- 还没有人留言评论。精彩留言会获得点赞!