支持高速电力线载波与无线射频双通信方式的双模芯片的制作方法

本发明涉及安全应用芯片,尤其涉及一种支持高速电力线载波与无线射频双通信方式的双模芯片。

背景技术:

1、目前在智能电网的应用场景中,基于高速电力线载波(high speed power linecarrier,hplc)以及各类无线射频(radio frequency,rf)技术实现的智能芯片都得到了广泛应用。但这些智能芯片大多只采用一种单模通信机制进行数据收发,这在一定程度上会降低互联互通效率。为解决这个问题就需要设计一种能同时支持hplc与rf方式的双模芯片。目前市面上的双模芯片方案是两个单模通信模组(主控+通信)与一个共享存储器构成的叠加方案。这种方案因为其本质是通过叠加模组实现的,所以内部会有多类功能重复的器件存在,诸如两组主控、两组内存、两组1/0等,而这些冗余配置自然就会导致芯片尺寸偏大、功耗偏高。

技术实现思路

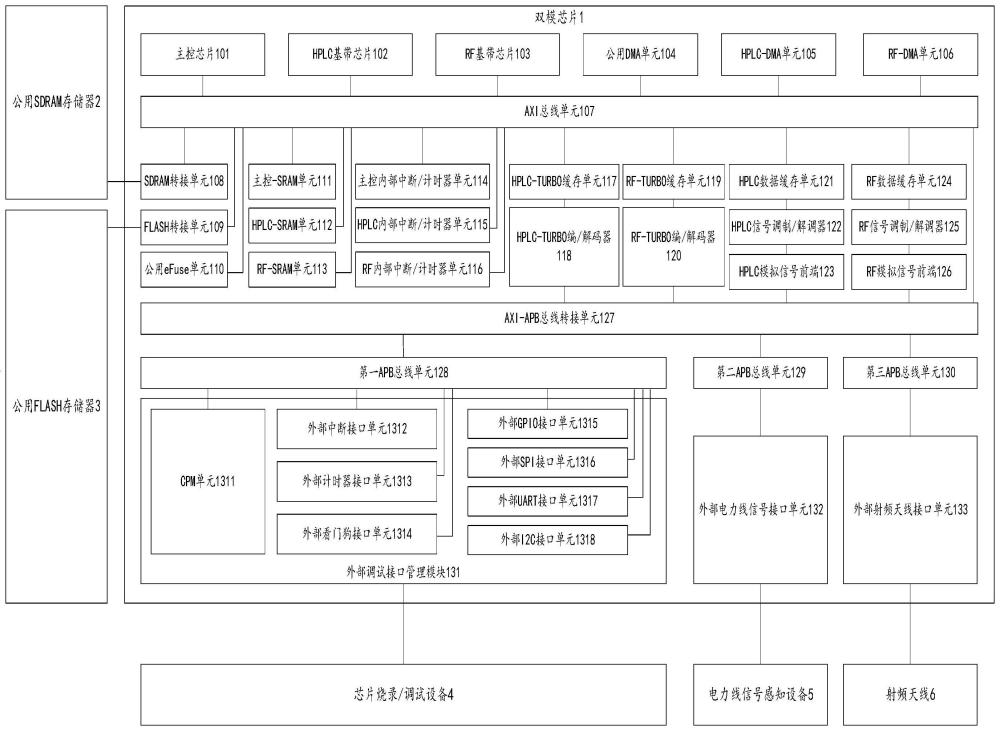

1、本发明的目的,就是针对上述技术缺陷,提供一种支持高速电力线载波与无线射频双通信方式的双模芯片。通过本发明给出的一种由一个主控芯片带两组通信逻辑(hplc/rf基带芯片+hplc/rf数据缓存单元+hplc/rf信号调制/解调器+hplc/rf模拟信号前端+外部电力线/射频天线信号接口单元)并共享存储介质与外部1/0接口的双模芯片方案,可以达到减小芯片尺寸、降低芯片功耗的目的。

2、为实现上述目的,本发明提供了一种支持高速电力线载波与无线射频双通信方式的双模芯片,包括:主控芯片、hplc基带芯片和rf基带芯片;

3、所述双模芯片分别与外部的电力线信号感知设备、射频天线和芯片烧录/调试设备连接;所述双模芯片还分别与片外的公用sdram存储器和公用flash存储器连接;所述电力线信号感知设备用于对电力线上的电力线信号进行信号感知并将感知到的第一电力线信号向所述双模芯片输入,并将所述双模芯片回送的第二电力线信号向电力线馈送;所述射频天线用于将接收到的第一射频信号向所述双模芯片输入,并对所述双模芯片回送的第二射频信号进行发送;所述芯片烧录/调试设备用于对所述双模芯片进行调试;

4、所述双模芯片用于接收所述电力线信号感知设备输入的所述第一电力线信号;并对所述第一电力线信号进行信号降噪与滤波处理得到对应的第一处理信号;并对所述第一处理信号进行信号解调处理得到对应的第一信号解调数据;并对所述第一信号解调数据进行解码处理得到对应的第一信号解码报文;并对所述第一信号解码报文进行报文解析得到对应的第一应用层数据;并基于对应的应用层数据处理代码对所述第一应用层数据进行处理得到对应的第一应用层反馈数据;并对所述第一应用层反馈数据进行报文封装得到对应的第一反馈报文;并对所述第一反馈报文进行编码得到对应的第一信号编码数据;并对所述第一信号编码数据进行信号调制得到对应的第二处理信号;并对所述第二处理信号进行信号增加得到对应的第二电力线信号向所述电力线信号感知设备发送;

5、所述双模芯片还用于接收所述射频天线输入的所述第一射频信号;并对所述第一射频信号进行信号降噪与滤波处理得到对应的第三处理信号;并对所述第三处理信号进行信号解调处理得到对应的第二信号解调数据;并对所述第二信号解调数据进行解码处理得到对应的第二信号解码报文;并对所述第二信号解码报文进行报文解析得到对应的第二应用层数据;并基于对应的应用层数据处理代码对所述第二应用层数据进行处理得到对应的第二应用层反馈数据;并对所述第二应用层反馈数据进行报文封装得到对应的第二反馈报文;并对所述第二反馈报文进行编码得到对应的第二信号编码数据;并对所述第二信号编码数据进行信号调制得到对应的第四处理信号;并对所述第四处理信号进行信号增加得到对应的第二射频信号向所述射频天线发送;

6、所述双模芯片还用于根据所述芯片烧录/调试设备输入的第一输入数据进行对应的烧录和调试处理。

7、优选的,所述双模芯片包括所述主控芯片、所述hplc基带芯片、所述rf基带芯片、公用dma单元、hplc-dma单元、rf-dma单元、axi总线单元、sdram转接单元、flash转接单元、公用efuse单元、主控-sram单元、hplc-sram单元、rf-sram单元、主控内部中断/计时器单元、hplc内部中断/计时器单元、rf内部中断/计时器单元、hplc-turbo缓存单元、hplc-turbo编/解码器、rf-turbo缓存单元、rf-turbo编/解码器、hplc数据缓存单元、hplc信号调制/解调器、hplc模拟信号前端、rf数据缓存单元、rf信号调制/解调器、rf模拟信号前端、axi-apb总线转接单元、第一apb总线单元、第二apb总线单元、第三apb总线单元、外部调试接口管理模块、外部电力线信号接口单元和外部射频天线接口单元;

8、所述axi总线单元的多个主设备接口分别与所述主控芯片、所述hplc基带芯片、所述rf基带芯片、所述公用dma单元、所述hplc-dma单元和所述rf-dma单元连接;所述axi总线单元的多个从设备接口分别与所述sdram转接单元、所述flash转接单元、所述公用efuse单元、所述主控-sram单元、所述hplc-sram单元、所述rf-sram单元、所述主控内部中断/计时器单元、所述hplc内部中断/计时器单元、所述rf内部中断/计时器单元、所述hplc-turbo缓存单元、所述rf-turbo缓存单元、所述hplc数据缓存单元、所述rf数据缓存单元和所述axi-apb总线转接单元连接;

9、所述axi-apb总线转接单元分别与所述hplc-turbo编/解码器、所述rf-turbo编/解码器、所述hplc模拟信号前端、所述rf模拟信号前端、所述第一apb总线单元、所述第二apb总线单元和所述第三apb总线单元连接;

10、所述第一apb总线单元与所述外部调试接口管理模块连接;

11、所述第二apb总线单元与所述外部电力线信号接口单元连接;

12、所述第三apb总线单元与所述外部射频天线接口单元连接。

13、优选的,所述sdram转接单元与所述公用sdram存储器连接;所述公用sdram存储器用于为所述主控芯片、所述hplc基带芯片和所述rf基带芯片提供共享的片外易失性数据存储区;

14、所述flash转接单元与所述公用flash存储器连接;所述公用flash存储器用于为所述主控芯片、所述hplc基带芯片和所述rf基带芯片提供共享的片外非易失性数据存储区;

15、所述公用efuse单元用于为所述主控芯片、所述hplc基带芯片和所述rf基带芯片提供共享的otp数据存储区;

16、所述主控-sram单元、所述hplc-sram单元和所述rf-sram单元用于分别为对应的所述主控芯片、所述hplc基带芯片和所述rf基带芯片提供专用的片内易失性数据存储区;

17、所述主控内部中断/计时器单元、所述hplc内部中断/计时器单元和所述rf内部中断/计时器单元各自都包括多个内部中断接口和内部计时器接口,三个内部中断/计时器单元的多个内部中断接口中都包括一个对应所述公用dma单元的中断接口;三个内部中断/计时器单元用于分别为对应的所述主控芯片、所述hplc基带芯片和所述rf基带芯片提供专用的片内中断接口与片内计时器接口;

18、所述公用dma单元用于为所述主控芯片、所述hplc基带芯片和所述rf基带芯片提供不占用芯片资源的存储数据搬移功能;所述hplc-dma单元仅用于为所述hplc基带芯片提供不占用基带芯片资源的存储数据搬移功能;所述rf-dma单元仅用于为所述rf基带芯片提供不占用基带芯片资源的存储数据搬移功能;所述存储数据搬移功能为从源存储介质的指定地址段内读取数据并复制到目标存储介质的指定地址段内。

19、优选的,所述hplc-turbo缓存单元与所述hplc-turbo编/解码器连接;

20、所述hplc-turbo缓存单元用于接收所述hplc基带芯片发送的待编码或待解码的原始数据向所述hplc-turbo编/解码器发送;所述hplc-turbo编/解码器用于对所述待编码或待解码的原始数据进行对应的turbo编码或解码操作,并将得到的编码或解码数据存入所述hplc-turbo缓存单元;所述hplc-turbo缓存单元还用于将所述编码或解码数据向所述hplc基带芯片回发;

21、所述hplc数据缓存单元与所述hplc信号调制/解调器连接;所述hplc信号调制/解调器与所述hplc模拟信号前端连接;所述hplc模拟信号前端通过所述axi-apb总线转接单元以及所述第二apb总线单元与所述外部电力线信号接口单元连接;所述外部电力线信号接口单元与外部的所述电力线信号感知设备的对应信号接口连接;

22、所述hplc模拟信号前端用于通过所述外部电力线信号接口单元接收所述电力线信号感知设备输入的电力线信号,并对当次输入的电力线信号进行滤波与降噪处理生成对应的处理信号向所述hplc信号调制/解调器发送;所述hplc信号调制/解调器用于对所述处理信号进行信号解调得到对应的信号解调数据存入所述hplc数据缓存单元;所述hplc数据缓存单元用于将所述信号解调数据向所述hplc基带芯片发送;

23、所述hplc基带芯片用于根据预设的双模通信规范中与高速载波物理层对应的接收端解码规则对所述信号解调数据进行解码,并在解码过程中为提高解码效率调用所述hplc-turbo缓存单元和所述hplc-turbo编/解码器进行turbo解码,并将按所述双模通信规范中与高速载波物理层对应的接收端解码规则进行解码得到的信号解码报文向所述主控芯片发送;

24、所述主控芯片用于根据预设的双模通信规范中与应用层对应的应用报文协议对所述信号解码报文进行报文解析得到对应的应用层数据;并调用对应的应用层数据处理代码对所述应用层数据进行处理得到对应的应用层反馈数据;并根据所述双模通信规范中与应用层对应的应用报文协议对所述应用层反馈数据进行报文封装得到对应的反馈报文向所述hplc基带芯片发送;

25、所述hplc基带芯片还用于根据预设的双模通信规范中与高速载波物理层对应的发送端编码规则对所述反馈报文进行编码,并在编码过程中为提高编码效率调用所述hplc-turbo缓存单元和所述hplc-turbo编/解码器进行turbo编码,并将按所述双模通信规范中与高速载波物理层对应的发送端编码规则进行编码得到的信号编码数据存入所述hplc数据缓存单元中;

26、所述hplc数据缓存单元还用于将所述hplc基带芯片存入的所述信号编码数据向所述hplc信号调制/解调器发送;所述hplc信号调制/解调器还用于对所述信号编码数据进行信号调制并将调制后得到的处理信号向所述hplc模拟信号前端发送;所述hplc模拟信号前端还用于对所述处理信号进行信号增强处理并将处理后得到的电力线信号通过所述外部电力线信号接口单元向所述电力线信号感知设备发送。

27、优选的,所述rf-turbo缓存单元与所述rf-turbo编/解码器连接;

28、所述rf-turbo缓存单元用于接收所述rf基带芯片发送的待编码或待解码的原始数据向所述rf-turbo编/解码器发送;所述rf-turbo编/解码器用于对所述待编码或待解码的原始数据进行对应的turbo编码或解码操作,并将得到的编码或解码数据存入所述rf-turbo缓存单元;所述rf-turbo缓存单元还用于将所述编码或解码数据向所述rf基带芯片回发;

29、所述rf数据缓存单元与所述rf信号调制/解调器连接;所述rf信号调制/解调器与所述rf模拟信号前端连接;所述rf模拟信号前端通过所述axi-apb总线转接单元以及所述第三apb总线单元与所述外部射频天线接口单元连接;所述外部射频天线接口单元与外部的所述射频天线连接;

30、所述rf模拟信号前端用于通过所述外部射频天线接口单元接收所述射频天线输入的射频信号,并对当次输入的射频信号进行滤波与降噪处理生成对应的处理信号向所述rf信号调制/解调器发送;所述rf信号调制/解调器用于对所述处理信号进行信号解调得到对应的信号解调数据存入所述rf数据缓存单元;所述rf数据缓存单元用于将所述信号解调数据向所述rf基带芯片发送;

31、所述rf基带芯片于根据预设的双模通信规范中与无线射频物理层对应的接收端解码规则对所述信号解调数据进行解码,并在解码过程中为提高解码效率调用所述rf-turbo缓存单元和所述rf-turbo编/解码器进行turbo解码,并将按所述双模通信规范中与无线射频物理层对应的接收端解码规则进行解码得到的信号解码报文向所述主控芯片发送;

32、所述主控芯片还用于根据预设的双模通信规范中与应用层对应的应用报文协议对所述信号解码报文进行报文解析得到对应的应用层数据;并调用对应的应用层数据处理代码对所述应用层数据进行处理得到对应的应用层反馈数据;并根据所述双模通信规范中与应用层对应的应用报文协议对所述应用层反馈数据进行报文封装得到对应的反馈报文向所述rf基带芯片发送;

33、所述rf基带芯片还用于根据预设的双模通信规范中与无线射频物理层对应的发送端编码规则对所述反馈报文进行编码,并在编码过程中为提高编码效率调用所述rf-turbo缓存单元和所述rf-turbo编/解码器进行turbo编码,并将按所述双模通信规范中与无线射频物理层对应的发送端编码规则进行编码得到的信号编码数据存入所述rf数据缓存单元中;

34、所述rf数据缓存单元还用于将所述rf基带芯片存入的所述信号编码数据向所述rf信号调制/解调器发送;所述rf信号调制/解调器还用于对所述信号编码数据进行信号调制并将调制后得到的处理信号向所述rf模拟信号前端发送;所述rf模拟信号前端还用于对所述处理信号进行信号增强处理并将处理后得到的射频信号通过所述外部射频天线接口单元向所述射频天线发送。

35、优选的,所述双模芯片具体用于在所述接收所述电力线信号感知设备输入的所述第一电力线信号时,由所述hplc模拟信号前端通过所述外部电力线信号接口单元接收所述电力线信号感知设备输入的所述第一电力线信号;

36、所述双模芯片具体用于在所述对所述第一电力线信号进行信号降噪与滤波处理得到对应的第一处理信号时,由所述hplc模拟信号前端对所述第一电力线信号进行滤波与降噪处理生成对应的所述第一处理信号向所述hplc信号调制/解调器发送;

37、所述双模芯片具体用于在所述对所述第一处理信号进行信号解调处理得到对应的第一信号解调数据时,由所述hplc信号调制/解调器用于对所述第一处理信号进行信号解调得到对应的所述第一信号解调数据存入所述hplc数据缓存单元;并由所述hplc数据缓存单元将所述第一信号解调数据向所述hplc基带芯片发送;

38、所述双模芯片具体用于在所述对所述第一信号解调数据进行解码处理得到对应的第一信号解码报文时,由所述hplc基带芯片根据所述双模通信规范中与高速载波物理层对应的接收端解码规则对所述第一信号解调数据进行解码得到对应的所述第一信号解码报文向所述主控芯片发送;

39、所述双模芯片具体用于在所述对所述第一信号解码报文进行报文解析得到对应的第一应用层数据时,由所述主控芯片根据所述双模通信规范中与应用层对应的应用报文协议对所述第一信号解码报文进行报文解析得到对应的所述第一应用层数据;

40、所述双模芯片具体用于在所述基于对应的应用层数据处理代码对所述第一应用层数据进行处理得到对应的第一应用层反馈数据时,由所述主控芯片调用对应的应用层数据处理代码对所述第一应用层反馈数据进行处理得到对应的所述第一应用层反馈数据;

41、所述双模芯片具体用于在所述对所述第一应用层反馈数据进行报文封装得到对应的第一反馈报文时,由所述主控芯片根据所述双模通信规范中与应用层对应的应用报文协议对所述第一应用层反馈数据进行报文封装得到对应的第一反馈报文向所述hplc基带芯片发送;

42、所述双模芯片具体用于在所述对所述第一反馈报文进行编码得到对应的第一信号编码数据时,由所述hplc基带芯片还根据所述双模通信规范中与高速载波物理层对应的发送端编码规则对所述第一信号编码数据进行编码得到对应的所述第一信号编码数据存入所述hplc数据缓存单元中;

43、所述双模芯片具体用于在所述对所述第一信号编码数据进行信号调制得到对应的第二处理信号时,由所述hplc数据缓存单元将所述hplc基带芯片存入的所述第一信号编码数据向所述hplc信号调制/解调器发送;并由所述hplc信号调制/解调器对所述第一信号编码数据进行信号调制得到对应的所述第二处理信号向所述hplc模拟信号前端发送;

44、所述双模芯片具体用于在所述对所述第二处理信号进行信号增加得到对应的第二电力线信号向所述电力线信号感知设备发送时,由所述hplc模拟信号前端对所述第二处理信号进行信号增强处理得到对应的所述第二电力线信号;并由所述hplc模拟信号前端通过所述外部电力线信号接口向所述电力线信号感知设备发送所述第二电力线信号。

45、优选的,所述双模芯片具体用于在所述接收所述射频天线输入的所述第一射频信号时,由所述rf模拟信号前端通过所述外部射频天线接口单元接收所述射频天线输入的所述第一射频信号;

46、所述双模芯片具体用于在所述对所述第一射频信号进行信号降噪与滤波处理得到对应的第三处理信号时,由所述rf模拟信号前端对所述第三处理信号进行滤波与降噪处理生成对应的所述第三处理信号向所述rf信号调制/解调器发送;

47、所述双模芯片具体用于在所述对所述第三处理信号进行信号解调处理得到对应的第二信号解调数据时,由所述rf信号调制/解调器对所述第三处理信号进行信号解调得到对应的所述第二信号解调数据存入所述rf数据缓存单元;并由所述rf数据缓存单元将所述第二信号解调数据向所述rf基带芯片发送;

48、所述双模芯片具体用于在所述对所述第二信号解调数据进行解码处理得到对应的第二信号解码报文时,由所述rf基带芯片于根据所述双模通信规范中与无线射频物理层对应的接收端解码规则对所述第二信号解调数据进行解码得到对应的所述第二信号解码报文向所述主控芯片发送;

49、所述双模芯片具体用于在所述对所述第二信号解码报文进行报文解析得到对应的第二应用层数据时,由所述主控芯片根据所述双模通信规范中与应用层对应的应用报文协议对所述第二应用层数据进行报文解析得到对应的所述第二应用层数据;

50、所述双模芯片具体用于在所述基于对应的应用层数据处理代码对所述第二应用层数据进行处理得到对应的第二应用层反馈数据时,由所述主控芯片调用对应的应用层数据处理代码对所述第二应用层数据进行处理得到对应的所述第二应用层反馈数据;

51、所述双模芯片具体用于在所述对所述第二应用层反馈数据进行报文封装得到对应的第二反馈报文时,由所述主控芯片根据所述双模通信规范中与应用层对应的应用报文协议对所述第二应用层反馈数据进行报文封装得到对应的所述第二反馈报文向所述rf基带芯片发送;

52、所述双模芯片具体用于在所述对所述第二反馈报文进行编码得到对应的第二信号编码数据时,由所述rf基带芯片根据所述双模通信规范中与无线射频物理层对应的发送端编码规则对所述第二反馈报文进行编码得到对应的所述第二信号编码数据存入所述rf数据缓存单元中;

53、所述双模芯片具体用于在所述对所述第二信号编码数据进行信号调制得到对应的第四处理信号时,由所述rf数据缓存单元将所述rf基带芯片存入的所述第二信号编码数据向所述rf信号调制/解调器发送;并由所述rf信号调制/解调器对所述第二信号编码数据进行信号调制得到对应的所述第四处理信号向所述rf模拟信号前端发送;

54、所述双模芯片具体用于在所述对所述第四处理信号进行信号增加得到对应的第二射频信号向所述射频天线发送时,由所述rf模拟信号前端对所述第四处理信号进行信号增强处理得到对应的所述第二射频信号;并由所述rf模拟信号前端通过所述外部射频天线接口单元向所述射频天线发送所述第二射频信号。

55、优选的,所述外部调试接口管理模块由一个cpm单元和多个外部通讯接口单元构成;所述多个外部通讯接口单元包括外部中断接口单元、外部计时器接口单元、外部看门狗接口单元、外部gpio接口单元、外部spi接口单元、外部uart接口单元和外部i2c接口单元;所述cpm单元以及各个所述外部通讯接口单元分别与所述第一apb总线单元连接;各个所述外部通讯接口单元还分别与外部的所述芯片烧录/调试设备的对应通讯接口连接;

56、所述cpm单元用于对各个所述外部通讯接口单元的数据收发进程进行控制管理;

57、各个所述外部通讯接口单元用于将所述芯片烧录/调试设备输入的所述第一输入数据向所述主控芯片发送;并接收所述主控芯片回发的第一输出数据向所述芯片烧录/调试设备返回;

58、所述第一输入数据包括第一类型和第一数据包;

59、所述第一类型包括烧录类型、第一调试类型和第二调试类型;

60、所述第一类型为烧录类型时,对应的所述第一数据包由多个第一烧录记录组成;所述第一烧录记录包括第一起始地址、第一烧录数据和第一校验码;

61、所述第一类型为第一调试类型时,对应的所述第一数据包由多个第一调试记录组成;所述第一调试记录包括第二起始地址和第一数据长度;

62、所述第一类型为第二调试类型时,对应的所述第一数据包由多个第二调试记录组成;所述第二调试记录包括第三起始地址和第一设置数据。

63、优选的,所述主控芯片还用于从所述第一输入数据中提取出对应的所述第一类型和所述第一数据包;

64、并在所述第一类型为烧录类型时,对所述第一数据包的各个所述第一烧录记录进行遍历;并在遍历过程中,将当前遍历的所述第一烧录记录作为对应的当前记录;并将内部或外部存储介质中与所述当前记录的所述第一起始地址对应的存储地址作为对应的当前起始地址;并将所述当前记录的所述第一烧录数据从所述当前起始地址起写入对应的存储介质中;并在当次写操作完成时,从所述当前起始地址起对本次写入的数据进行读取得到对应的第一读取数据;并基于预设的烧录数据校验算法根据所述第一读取数据进行校验码计算得到对应的当次校验码;并对所述当次校验码与所述当前记录的所述第一校验码是否匹配进行识别,若匹配则设置对应的第一烧录状态为成功,若不匹配则设置对应的所述第一烧录状态为失败;并在遍历结束时,对得到的所有所述第一烧录状态是否都为成功进行识别;若是,则设置对应的所述第一输出数据为烧录成功;若否,则设置对应的所述第一输出数据为烧录失败;

65、并在所述第一类型为第一调试类型时,对所述第一数据包的各个所述第一调试记录进行遍历;并在遍历过程中,将当前遍历的所述第一调试记录作为对应的当前记录;并将内部或外部存储介质中与所述当前记录的所述第二起始地址对应的存储地址作为对应的当前起始地址;并将所述当前记录的所述第一数据长度作为对应的当前数据长度;并从所述当前起始地址起读取数据长度为所述当前数据长度的一段存储数据作为对应的当前读取数据;并由所述当前起始地址、所述当前数据长度和所述当前读取数据组成一个对应的第一调试返回记录;并在遍历结束时,由得到的所有所述第一调试返回记录组成对应的所述第一输出数据;

66、并在所述第一类型为第二调试类型时,对所述第一数据包的各个所述第二调试记录进行遍历;并在遍历过程中,将当前遍历的所述第二调试记录作为对应的当前记录;并将内部或外部存储介质中与所述当前记录的所述第三起始地址对应的存储地址作为对应的当前起始地址;并将所述当前记录的所述第一设置数据从所述当前起始地址起写入对应的存储介质中;并在当次写操作完成时,从所述当前起始地址起对本次写入的数据进行读取得到对应的第二读取数据;并对所述第二读取数据与所述第一设置数据是否匹配进行识别;若匹配则设置对应的第一设置状态为成功,若不匹配则设置对应的所述第一设置状态为失败;并在遍历结束时,对得到的所有所述第一设置状态是否都为成功进行识别;若是,则设置对应的所述第一输出数据为设置成功;若否,则设置对应的所述第一输出数据为设置失败;

67、并将得到的所述第一输出数据向所述外部调试接口管理模块回发。

68、优选的,所述双模芯片具体用于在所述根据所述芯片烧录/调试设备输入的第一输入数据进行对应的烧录和调试处理时,由所述外部调试接口管理模块接收所述芯片烧录/调试设备输入的所述第一输入数据向所述主控芯片发送;并由所述主控芯片根据所述第一输入数据的所述第一类型进行对应的烧录和调试处理得到对应的所述第一输出数据向所述外部调试接口管理模块回发;并由所述外部调试接口管理模块将所述第一输出数据向所述芯片烧录/调试设备发送。

69、本发明提供一种支持高速电力线载波与无线射频双通信方式的双模芯片;该双模芯片包括主控芯片、hplc基带芯片、rf基带芯片、公用dma单元、hplc-dma单元、rf-dma单元、axi总线单元、sdram转接单元、flash转接单元、公用efuse单元、主控-sram单元、hplc-sram单元、rf-sram单元、主控内部中断/计时器单元、hplc内部中断/计时器单元、rf内部中断/计时器单元、hplc-turbo缓存单元、hplc-turbo编/解码器、rf-turbo缓存单元、rf-turbo编/解码器、hplc数据缓存单元、hplc信号调制/解调器、hplc模拟信号前端、rf数据缓存单元、rf信号调制/解调器、rf模拟信号前端、axi-apb总线转接单元、第一apb总线单元、第二apb总线单元、第三apb总线单元、外部调试接口管理模块、外部电力线信号接口单元和外部射频天线接口单元。本发明给出的这种由一个主控芯片带两组通信逻辑(hplc/rf基带芯片+hplc/rf数据缓存单元+hplc/rf信号调制/解调器+hplc/rf模拟信号前端+外部电力线/射频天线信号接口单元)并共享存储介质与外部1/0接口的双模芯片方案,一方面减小了芯片尺寸、降低了芯片功耗;另一方面通过两个硬件turbo编/解码器也提高了芯片的编/解码效率。

- 还没有人留言评论。精彩留言会获得点赞!