计数器及模数转换器的制作方法

本技术涉及图像传感器,特别是涉及一种计数器及模数转换器。

背景技术:

1、cmos图像传感器具有低电压、低功耗、低成本以及高集成度等优势,在机器视觉、消费电子、高清监控和医学成像等领域具有重要应用价值。模数转换器(analog-to-digital converter,adc)是cmos图像传感器读出电路的重要组成部分,承担着将像素输出的模拟信号转换为数字信号的功能。

2、cmos图像传感器中一般会采用列级adc,常见的有单斜坡adc(ss sdc)、逐次逼近型adc(sar adc)和循环式adc(cyclic adc),其中ss adc的电路简单,每列只需要一个比较器和一个计数器,并且所有列共用斜坡信号,列一致性比较好,因此,ss adc是cmos图像传感器中应用最广泛的列级adc。

3、传统ss adc的电路结构如图1所示,工作原理如图2所示,斜坡发生器产生一个斜坡信号并通过电容采样到每一列比较器的正输入端,比较器的负输入端采样各列的像素信号。以第一列为例,斜坡信号vramp会遍历整个量化电压范围,并与像素信号vin1进行比较,同时计数器开始计数,当斜坡信号vramp大于像素信号vin1时,比较器发生翻转,计数器停止计数,此时计数结果就是像素信号vin1量化后的数字码值。

4、采用列并行读出电路的cmos图像传感器会面临固定模式噪声(fpn)的问题,而采用4t有源像素结构可以进行相关双采样(correlated double sampling,cds)操作,需要分别读出像素的复位信号vrst和曝光信号vsig,然后将二者作差,由于两个信号中包含同样的fpn,通过作差可以消除fpn,提高成像质量。

5、cds操作是在ss adc中使用两段斜坡信号进行两次量化,第一次量化像素的复位信号vrst,第二次量化像素的曝光信号vsig,并控制计数器在两次量化期间分别向下和向上计数,从而将像素输出的模拟电压值在数字域作差。因此,该结构中的计数器为可逆计数器,即可以实现向上/向下计数的切换。

6、但是,由于计数时钟的工作频率特别高(通常在几百mhz甚至超过1ghz),可逆计数器需要在每一级d触发器之间插入二选一开关以及用于驱动的缓冲器,这会使功耗增加。同时,该结构面临着在向上/向下计数切换期间保持第一次量化结果稳定的问题,需要额外的保持电路,这会使版图更加复杂,使走线的寄生电容和电阻增加,使功耗进一步增加,并且限制了计数器的最高工作频率。

技术实现思路

1、鉴于以上所述现有技术的缺点,本实用新型的目的在于提供一种计数器及模数转换器,用于解决现有计数器在数字量化时存在电路结构复杂、功耗大的问题。

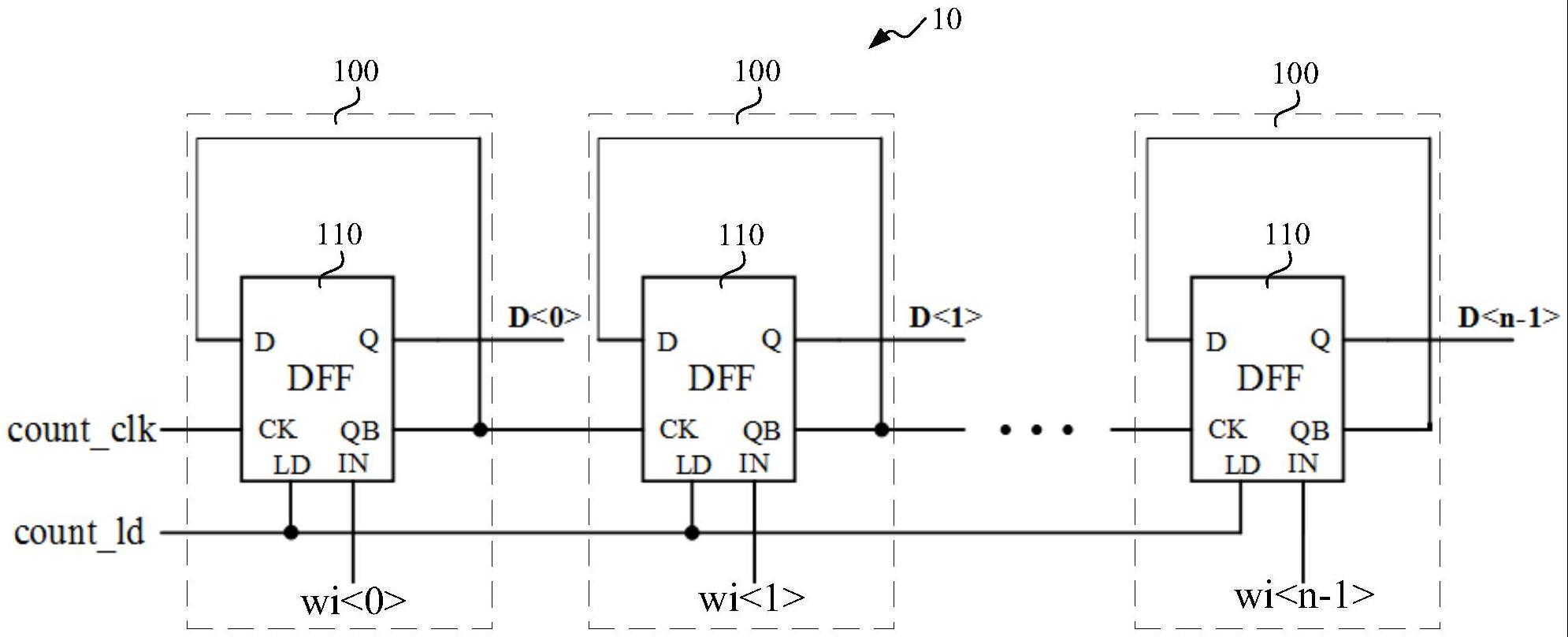

2、为实现上述目的及其他相关目的,本实用新型提供一种计数器,所述计数器包括:n个计数单元,所述计数单元包括可写入d触发器,n为大于等于1的整数;其中,后一级计数单元中可写入d触发器的时钟端连接前一级计数单元中可写入d触发器的反向输出端或正向输出端,第一级计数单元中可写入d触发器的时钟端连接时钟信号;每一级计数单元中可写入d触发器的反向输出端连接数据端,正向输出端生成计数结果,控制端连接控制信号,写入端连接写入信号;在所述控制信号有效时,将所述写入信号写入所述可写入d触发器中。

3、可选地,所述可写入d触发器包括:写控模块、输入级模块、主级传输锁存模块、中间级模块、从级传输锁存模块及输出级模块;其中,

4、所述写控模块连接所述可写入d触发器的控制端和写入端,用于对所述控制信号和所述写入信号进行逻辑运算并生成第一写控信号和第二写控信号;

5、所述输入级模块连接所述可写入d触发器的时钟端和数据端,用于在所述时钟端的输入时钟的控制下,对所述数据端输入的第一数据信号进行传输并生成第二数据信号;

6、所述主级传输锁存模块连接所述写控模块和所述输入级模块的输出端并连接所述可写入d触发器的时钟端,用于在所述输入时钟、所述第一写控信号和所述第二写控信号的控制下,对所述第二数据信号进行传输并生成第三数据信号,及对所述第二数据信号和所述第三数据信号进行锁存;

7、所述中间级模块连接所述主级传输锁存模块的输出端并连接所述可写入d触发器的时钟端,用于在所述输入时钟控制下,对所述第三数据信号进行传输并生成第四数据信号;

8、所述从级传输锁存模块连接所述写控模块和所述中间级模块的输出端并连接所述可写入d触发器的时钟端,用于在所述输入时钟、所述第一写控信号和所述第二写控信号的控制下,对所述第四数据信号进行传输并生成第五数据信号,及对所述第四数据信号和所述第五数据信号进行锁存;

9、所述输出级模块连接所述从级传输锁存模块的输出端,所述输出级模块的输出端作为所述反向输出端和正向输出端,分别用于对所述第五数据信号及其反向信号进行输出。

10、可选地,所述写控模块包括:第一与非门、第二与非门及第一反相器;所述第一与非门的第一输入端连接所述控制信号,第二输入端经由所述第一反相器连接所述写入信号,输出端生成所述第一写控信号;所述第二与非门的第一输入端连接所述控制信号,第二输入端连接所述写入信号,输出端生成所述第二写控信号;

11、所述主级传输锁存模块包括:主级传输部分及主级锁存部分;其中,

12、所述主级传输部分包括:第三与非门;所述第三与非门的第一输入端连接所述第二数据信号,第二输入端连接所述第二写控信号,输出端生成所述第三数据信号;

13、所述主级锁存部分包括:第一pmos管、第二pmos管、第三pmos管、第一nmos管、第二nmos管及第三nmos管;所述第一pmos管的栅极连接所述第一写控信号,源极连接参考电压,漏极连接所述第二pmos管的漏极;所述第二pmos管的栅极连接所述第三与非门的输出端,源极连接所述参考电压,漏极连接所述第三pmos管的源极;所述第三pmos管的栅极连接所述输入时钟的反向信号,漏极连接所述第一nmos管的漏极及所述第三与非门的第一输入端;所述第一nmos管的栅极连接所述输入时钟,源极连接所述第二nmos管的漏极;所述第二nmos管的栅极连接所述第三与非门的输出端,源极连接所述第三nmos管的漏极;所述第三nmos管的栅极连接所述第一写控信号,源极连接参考地;

14、所述从级传输锁存模块包括:从级传输部分及从级锁存部分;其中,

15、所述从级传输部分包括:第四与非门;所述第四与非门的第一输入端连接所述第四数据信号,第二输入端连接所述第一写控信号,输出端生成所述第五数据信号;

16、所述从级锁存部分包括:第四pmos管、第五pmos管、第六pmos管、第四nmos管、第五nmos管及第六nmos管;所述第四pmos管的栅极连接所述第二写控信号,源极连接所述参考电压,漏极连接所述第五pmos管的漏极;所述第五pmos管的栅极连接所述第四与非门的输出端,源极连接所述参考电压,漏极连接所述第六pmos管的源极;所述第六pmos管的栅极连接所述输入时钟,漏极连接所述第四nmos管的漏极及所述第四与非门的第一输入端;所述第四nmos管的栅极连接所述输入时钟的反向信号,源极连接所述第五nmos管的漏极;所述第五nmos管的栅极连接所述第四与非门的输出端,源极连接所述第六nmos管的漏极;所述第六nmos管的栅极连接所述第二写控信号,源极连接参考地。

17、可选地,所述可写入d触发器还具有复位功能,此时,所述可写入d触发器还包括:第一复位管、第二复位管及第三复位管;所述第一复位管并联于所述第一pmos管的两端,栅极连接复位触发器信号的反向信号;所述第二复位管串联于所述第三nmos管的源极和参考地之间,栅极连接所述复位触发器信号的反向信号;所述第三复位管的栅极连接所述复位触发器信号的反向信号,源极连接所述参考电压,漏极连接所述第四与非门的输出端。

18、可选地,所述写控模块包括:第二反相器及第三反相器;所述第二反相器的输入端连接所述控制信号,输出端生成所述第一写控信号;所述第三反相器的输入端连接所述写入信号,输出端生成所述第二写控信号;

19、所述主级传输锁存模块包括:主级传输部分及主级锁存部分;其中,

20、所述主级传输部分包括:第七pmos管、第八pmos管、第九pmos管、第七nmos管、第八nmos管及第九nmos管;所述第七pmos管的栅极连接所述第二写控信号,源极连接参考电压,漏极连接所述第八pmos管的源极;所述第八pmos管的栅极连接所述第一写控信号,漏极连接所述第九pmos管的漏极;所述第九pmos管的栅极连接所述第七nmos管的栅极并连接所述第二数据信号,源极连接所述参考电压,漏极连接所述第七nmos管的漏极并生成所述第三数据信号;所述第七nmos管的源极连接所述第八nmos管及所述第九nmos管的漏极;所述第八nmos管的栅极连接所述第二写控信号,源极连接参考地;所述第九nmos管的栅极连接所述第一写控信号,源极连接参考地;

21、所述主级锁存部分包括:第十pmos管、第十一pmos管、第十二pmos管、第十三pmos管、第十nmos管、第十一nmos管、第十二nmos管及第十三nmos管;所述第十pmos管的栅极连接所述写入信号,源极连接所述参考电压,漏极连接所述第十一pmos管的源极;所述第十一pmos管的栅极连接所述第一写控信号,漏极连接所述第十二pmos管的漏极;所述第十二pmos管的栅极连接所述第十一nmos管的栅极并连接所述第七nmos管的漏极,源极连接所述参考电压,漏极连接所述第十三pmos管的源极;所述第十三pmos管的栅极连接所述输入时钟的反向信号,漏极连接所述第十nmos管的漏极并连接所述第七nmos管的栅极;所述第十nmos管的栅极连接所述输入时钟,源极连接所述第十一nmos管的漏极;所述第十一nmos管的源极连接所述第十二nmos管及所述第十三nmos管的漏极;所述第十二nmos管的栅极连接写入信号,源极连接参考地;所述第十三nmos管的栅极连接所述第一写控信号,源极连接参考地;

22、所述从级传输锁存模块包括:从级传输部分及从级锁存部分;其中,

23、所述从级传输部分包括:第十四pmos管、第十五pmos管、第十六pmos管、第十四nmos管、第十五nmos管及第十六nmos管;所述第十四pmos管的栅极连接所述写入信号,源极连接所述参考电压,漏极连接所述第十五pmos管的源极;所述第十五pmos管的栅极连接所述第一写控信号,漏极连接所述第十六pmos管的漏极;所述第十六pmos管的栅极连接所述第十四nmos管的栅极并连接所述第四数据信号,源极连接所述参考电压,漏极连接所述第十四nmos管的漏极并生成所述第五数据信号;所述第十四nmos管的源极连接所述第十五nmos管及所述第十六nmos管的漏极;所述第十五nmos管的栅极连接所述写入信号,源极连接参考地;所述第十六nmos管的栅极连接所述第一写控信号,源极连接参考地;

24、所述从级锁存部分包括:第十七pmos管、第十八pmos管、第十九pmos管、第二十pmos管、第十七nmos管、第十八nmos管、第十九nmos管及第二十nmos管;所述第十七pmos管的栅极连接所述第二写控信号,源极连接所述参考电压,漏极连接所述第十八pmos管的源极;所述第十八pmos管的栅极连接所述第一写控信号,漏极连接所述第十九pmos管的漏极;所述第十九pmos管的栅极连接所述第十八nmos管的栅极并连接所述第十四nmos管的漏极,源极连接所述参考电压,漏极连接所述第二十pmos管的源极;所述第二十pmos管的栅极连接所述输入时钟,漏极连接所述第十七nmos管的漏极并连接所述第十四nmos管的栅极;所述第十七nmos管的栅极连接所述输入时钟的反向信号,源极连接所述第十八nmos管的漏极;所述第十八nmos管的源极连接所述第十九nmos管及所述第二十nmos管的漏极;所述第十九nmos管的栅极连接第二写控信号,源极连接参考地;所述第二十nmos管的栅极连接所述第一写控信号,源极连接参考地。

25、可选地,所述可写入d触发器还具有复位功能,此时,所述可写入d触发器还包括:第四复位管、第五复位管及第六复位管;所述第四复位管的栅极连接复位触发器信号的反向信号,源极连接所述第十pmos管的源极,漏极连接所述第十一pmos管的漏极;所述第五复位管的栅极连接所述复位触发器信号的反向信号,漏极连接所述第十二nmos管和所述第十三nmos管的源极,源极连接参考地;所述第六复位管的栅极连接所述复位触发器信号的反向信号,源极连接所述参考电压,漏极连接所述第十六pmos管的漏极。

26、可选地,所述输入级模块包括:第一三态反相器;其中,所述第一三态反相器在所述输入时钟为低电平时处于工作状态,在所述输入时钟为高电平时处于高阻状态;和/或,所述中间级模块包括:第一传输门;其中,所述第一传输门在所述输入时钟为低电平时截止,在所述输入时钟为高电平时导通。

27、可选地,采用锁存逻辑替换第一级计数单元中的可写入d触发器,所述锁存逻辑包括锁存器,且所述锁存逻辑的控制端连接控制信号,写入端连接写入信号,在所述控制信号有效时,将所述写入信号写入所述锁存逻辑中。

28、可选地,所述锁存逻辑还包括:第一选择开关、第一或非门、第四反相器、第五反相器、第六反相器、第七反相器、第八反相器及第九反相器;所述时钟信号经过所述第四反相器和所述第五反相器连接所述第一选择开关的第一输入端,所述第四反相器的输出端连接所述第一选择开关的第二输入端;所述第一选择开关的控制端连接所述写入信号,输出端连接所述锁存器的数据端;所述第一或非门的第一输入端连接所述控制信号,第二输入端连接计数使能信号,输出端经过所述第六反相器连接所述锁存器的时钟端;所述锁存器的输出端依次连接所述第七反相器、所述第八反相器和所述第九反相器,其中,所述第八反相器的输出端作为所述锁存逻辑的正向输出端,所述第九反相器的输出端作为所述锁存逻辑的反向输出端。

29、可选地,所述锁存器包括:第一反相逻辑门、第二传输门、第二反相逻辑门及第二三态反相器;所述第一反相逻辑门、所述第二传输门和所述第二反相逻辑门依次串联于所述锁存器的数据端和输出端,所述第二三态反相器并联于所述第二反相逻辑门的两端;其中,所述第二传输门在所述锁存器时钟端输入的控制时钟为低电平时截止,在所述控制时钟为高电平时导通;所述第二三态反相器在所述控制时钟为低电平时处于工作状态,在所述控制时钟为高电平时处于高阻状态。

30、可选地,所述计数单元还包括:第一存储器,至少用于提供所述写入信号。

31、可选地,所述第一存储器还用于存储所述计数结果,其中,所述第一存储器的存控端连接存储使能信号,输入端连接所述计数结果,写出端生成所述写入信号。

32、可选地,所述第一存储器的反向输出端作为其写出端;和/或,所述第一存储器具有复位功能及读出功能中的至少一种,在所述第一存储器还具有复位功能时,所述第一存储器的复位端连接复位存储器信号,在所述第一存储器还具有读出功能时,所述第一存储器的读控端连接读出使能信号,读出端生成读出信号。

33、可选地,所述计数单元还包括:第一存储器、第二存储器及第二选择开关,基于所述第二选择开关的选通,所述第一存储器或所述第二存储器提供所述写入信号。

34、可选地,所述第一存储器和所述第二存储器还用于存储所述计数结果;其中,所述第一存储器的存控端连接第一存储使能信号,输入端连接所述计数结果,写出端连接所述第二选择开关的第一输入端;所述第二存储器的存控端连接第二存储使能信号,输入端连接所述计数结果,写出端连接所述第二选择开关的第二输入端;所述第二选择开关的控制端连接选控信号,输出端生成所述写入信号。

35、可选地,所述第一存储器的反向输出端作为其写出端,所述第二存储器的反向输出端作为其写出端;和/或,所述第一存储器具有复位功能及读出功能中的至少一种,所述第二存储器具有复位功能及读出功能中的至少一种;其中,在所述第一存储器还具有复位功能时,所述第一存储器的复位端连接第一复位存储器信号,在所述第一存储器还具有读出功能时,所述第一存储器的读控端连接第一读出使能信号,读出端生成第一读出信号;在所述第二存储器还具有复位功能时,所述第二存储器的复位端连接第二复位存储器信号,在所述第二存储器还具有读出功能时,所述第二存储器的读控端连接第二读出使能信号,读出端生成第二读出信号。

36、可选地,在相应存储器的反向输出端作为其写出端且不具有复位功能和读出功能时,包括:第三传输门、第三反相逻辑门及第三三态反相器,所述第三传输门和所述第三反相逻辑门依次串联于相应存储器的输入端和写出端之间,所述第三三态反相器并联于所述第三反相逻辑门的两端;其中,所述第三传输门在相应存储使能信号为低电平时截止,在相应存储使能信号为高电平时导通;所述第三三态反相器在相应存储使能信号为低电平时处于工作状态,在相应存储使能信号为高电平时处于高阻状态;

37、在相应存储器具有复位功能时,还包括:第七复位管及第八复位管;所述第七复位管并联于参考电压和所述第三三态反相器的输出端之间,栅极连接相应复位存储器信号的反向信号;所述第八复位管串联于所述第三三态反相器中nmos管的源极和参考地之间,栅极连接相应复位存储器信号的反向信号;

38、在相应存储器具有读出功能时,还包括:第四反相逻辑门及第四传输门,所述第四反相逻辑门和所述第四传输门依次串联于相应存储器的写出端和读出端之间;其中,所述第四传输门在相应读出使能信号为低电平时截止,在相应读出使能信号为高电平时导通。

39、可选地,在所述第一存储器不具有读出功能且所述第二存储器具有读出功能时,所述计数器还包括:第三存储器及第三选择开关,所述第三存储器与所述第一存储器配合,实现读出功能;其中,所述第三存储器的存控端连接第三存储使能信号,输入端连接所述计数结果,读控端连接第三读出使能信号,正向输出端作为其读出端;所述第三选择开关的控制端连接读控信号,第一输入端连接所述第二存储器的读出端,第二输入端连接所述第三存储器的读出端,输出端生成读出信号。

40、可选地,所述第三存储器包括:第五传输门、第五反相逻辑门、第四三态反相器、第六反相逻辑门及第六传输门,所述第五传输门、所述第五反相逻辑门、所述第六反相逻辑门及所述第六传输门依次串联于所述第三存储器的输入端和读出端之间,所述第四三态反相器并联于所述第五反相逻辑门的两端;其中,

41、所述第五传输门在所述第三存储使能信号为低电平时截止,在所述第三存储使能信号为高电平时导通;所述第四三态反相器在所述第三存储使能信号为低电平时处于工作状态,在所述第三存储使能信号为高电平时处于高阻状态;所述第六传输门在所述第三读出使能信号为低电平时截止,在所述第三读出使能信号为高电平时导通。

42、本实用新型还提供一种模数转换器,所述模数转换器包括:至少一列模数转换单元,所述模数转换单元包括:比较器及如上任意一项记载的所述计数器;

43、所述比较器用于比较斜坡信号和输入信号并生成比较信号;

44、所述计数器连接所述比较器的输出端,用于根据所述比较信号对所述输入信号进行数字量化。

45、可选地,所述模数转换单元还包括:第一采样器及第二采样器,用于分别采样所述输入信号和所述斜坡信号;和/或,所述模数转换器还包括:斜坡生成电路,用于生成所述斜坡信号。

46、可选地,在所述计数器中的所述计数单元包括第一存储器时,所述模数转换器实现相关双采样;在所述计数器中的所述计数单元包括第一存储器、第二存储器及第二选择开关,或第一存储器、第二存储器、第三存储器、第二选择开关及第三选择开关时,所述模数转换器实现不同增益下的相关双采样。

47、如上所述,本实用新型的计数器及模数转换器,提出一种全新的计数器电路结构,同时兼具计数功能和写入功能;将其应用于模数转换器中进行像素量化时,可实现cds操作或pghdr模式下的cds操作,实现减小版图面积和优化走线,降低功耗和提高计数频率的目的。

- 还没有人留言评论。精彩留言会获得点赞!