设计短训练序列的方法和装置与流程

本技术涉及通信,并且更具体地,涉及一种设计短训练序列的方法和装置。

背景技术:

1、从802.11a经802.11g、802.11n、802.11ac到802.11ax的演进过程中,可用频段包括2.4吉赫(ghz)和5ghz。随着开放的频段越来越多,802.11所支持的最大信道带宽从20兆赫(mhz)扩展到40mhz再扩展到160mhz。2017年,美国联邦通信委员会(federalcommunications commission,fcc)开放了一段新的免费频段6ghz(5925-7125mhz),802.11ax标准工作者在802.11ax项目授权申请书(project authorization requests,par)中把802.11ax设备工作范围从2.4ghz,5ghz拓展到2.4ghz,5ghz和6ghz。由于新开放的6ghz频段可用带宽更大,可以预见,在802.11ax之后的下一代标准演进中,会支持大于160mhz的信道带宽。

2、那么,针对更大的信道带宽,如何设计短训练字段(short training field,stf),是一个值得关心的问题。

技术实现思路

1、本技术提供一种设计短训练序列的方法和装置,能够针对更大的信道带宽,设计短训练序列,并且能够向后兼容。

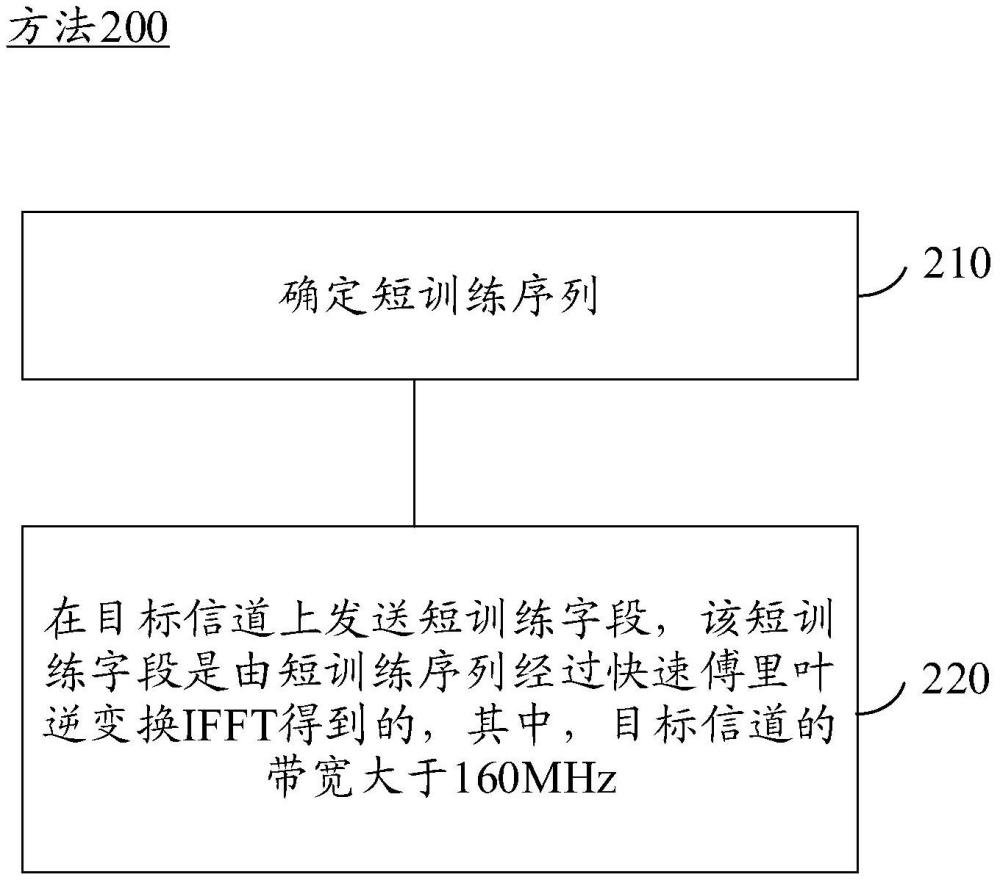

2、第一方面,提供了一种发送短训练字段的方法,该方法包括:确定短训练序列;在目标信道上发送短训练字段,所述短训练字段是由所述短训练序列经过快速傅里叶逆变换ifft得到的,其中,所述目标信道的带宽大于160mhz。

3、基于上述技术方案,确定更大信道带宽所对应的短训练序列,可以支持接收端对在更大信道带宽上传输的数据进行自动增益控制。该短训练序列可以基于现有信道带宽的短训练序列得到,并且,通过仿真计算,例如调节参数,可以获得性能较好的短训练序列。然后,该短训练序列经过快速傅立叶变换得到短训练字段。根据本技术实施例,不仅可以满足实际中的更大信道带宽,且向后兼容,而且通过对参数进行穷举仿真验证了本技术实施例提供的短训练序列,峰均功率值papr较小,性能较优,进而提高接收端的自动增益控制电路的估计效果,从而降低接收误码率。

4、结合第一方面,在第一方面的某些实现方式中,所述短训练序列是基于m序列变换得到的;或,所述短训练序列是基于参考信道的带宽所对应的高效频域序列hes变换得到的,其中,所述参考信道的带宽小于或等于160mhz。

5、基于上述技术方案,针对更大信道的带宽所对应的短训练序列,可以是直接基于m序列得到,例如,根据标准802.11ax可知,he-stf的高效短训练序列是基于m序列,通过复用、相位旋转和拼接构建而成。m序列在802.11ax标准中定义为m={-1,-1,-1,1,1,1,-1,1,1,1,-1,1,1,-1,1}。或者,也可以是基于现有信道所对应的高效频域序列hes得到,例如80mhz或160mhz对应的hes,从而可以与现有的短训练序列兼容。关于hes,在标准中,802.11ax定义了he-stf在频域上的值hesa:b:c,其中,a、c表示的是起始子载波的下标标号,b表示间隔。a:b:c表示从子载波a开始每隔b个子载波到子载波c。在其它子载波上,hes值为0。

6、结合第一方面,在第一方面的某些实现方式中,所述目标信道的带宽为240mhz,当所述短训练字段包括的周期长度为0.8μs时,所述短训练序列表示为:

7、

8、

9、其中,l1表示为{m,1,-m},r1表示为{-m,1,-m},-l1表示为{-m,-1,m},-r1表示为{m,-1,m}。

10、上述技术方案中,240mhz带宽共有3072个子载波,当短训练字段包括的周期长度为0.8μs时,短训练序列可以表示为s-1520:16:1520。其中,-1520、1520表示的是起始子载波的下标标号,16表示间隔。-1520:16:1520表示从下标为-1520的子载波开始每隔16个子载波到下标为1520的子载波。在其它子载波上,频域序列值为0。因此,上述短训练序列给出的这些值分别对应从下标为-1520的子载波开始每隔16个子载波到下标为1520的子载波的频域序列值。l1、r1为与80mhz、周期长度为0.8μs的短训练字段所对应的短训练序列相关的序列。从而240mhz的短训练序列可以与80mhz的短训练序列兼容。且上述240mhz的短训练序列,可以支持大带宽(带宽大于160mhz)信道上的自动增益控制,并且经过仿真验证,这些短训练序列的峰均功率比较小,可以支持大带宽信道上的自动增益控制,并且可以提高接收端的自动增益控制电路的估计效果,从而降低接收误码率。

11、结合第一方面,在第一方面的某些实现方式中,所述目标信道的带宽为240mhz,当所述短训练字段包括的周期长度为1.6μs时,所述短训练序列表示为:

12、

13、其中,l2表示为{m,-1,m,-1,-m,-1,m},r2表示为{-m,1,m,1,-m,1,-m},-l2表示为{-m,1,-m,1,m,1,-m},-r2表示为{m,-1,-m,-1,m,-1,m}。

14、上述技术方案中,240mhz带宽共有3072个子载波,当短训练字段包括的周期长度为1.6μs时,短训练序列可以表示为s-1528:8:1528。其中,-1528、1528表示的是起始子载波的下标标号,8表示间隔。-1528:8:1528表示从下标为-1528的子载波开始每隔8个子载波到下标为1528的子载波。在其它子载波上,频域序列值为0。因此,上述短训练序列给出的这些值分别对应从下标为-1528的子载波开始每隔8个子载波到下标为1528的子载波的频域序列值。其中,l2、r2为与80mhz、1.6μs的短训练序列相关的序列。从而240mhz的短训练序列可以与80mhz的短训练序列兼容。且上述240mhz的短训练序列,可以支持大带宽(带宽大于160mhz)信道上的自动增益控制,并且经过仿真验证,这些短训练序列的峰均功率比较小,可以支持大带宽信道上的自动增益控制,并且可以提高接收端的自动增益控制电路的估计效果,从而降低接收误码率。

15、结合第一方面,在第一方面的某些实现方式中,所述目标信道的带宽为320mhz,当所述短训练字段包括的周期长度为0.8μs时,所述短训练序列表示为:

16、

17、其中,l1表示为{m,1,-m},r1表示为{-m,1,-m},-l1表示为{-m,-1,m},-r1表示为{m,-1,m}。

18、上述技术方案中,320mhz带宽共有4096个子载波,当短训练字段包括的周期长度为0.8μs时,短训练序列可以表示为s-2032:16:2032。其中,-2032、2032表示的是起始子载波的下标标号,16表示间隔。-2032:16:2032表示从下标为-2032的子载波开始每隔16个子载波到下标为2032的子载波。在其它子载波上,频域序列值为0。因此,上述短训练序列给出的这些值分别对应从下标为-2032的子载波开始每隔16个子载波到下标为2032的子载波的频域序列值。其中,l1、r1为与80mhz、周期长度为0.8μs所对应的短训练序列相关的序列。从而320mhz的短训练序列可以与80mhz的短训练序列兼容。且上述320mhz的短训练序列,可以支持大带宽(带宽大于160mhz)信道上的自动增益控制,并且经过仿真验证,这些短训练序列的峰均功率比较小,可以支持大带宽信道上的自动增益控制,并且可以提高接收端的自动增益控制电路的估计效果,从而降低接收误码率。

19、结合第一方面,在第一方面的某些实现方式中,所述目标信道的带宽为320mhz,当所述短训练字段包括的周期长度为0.8μs时,所述短训练序列表示为:

20、

21、其中,l3表示为{m,1,-m,0,-m,1,-m},r3表示为{-m,-1,m,0,-m,1,-m},-l3表示为{-m,-1,m,0,m,-1,m},-r3表示为{m,1,-m,0,m,-1,m}。

22、上述技术方案中,320mhz带宽共有4096个子载波,当短训练字段包括的周期长度为0.8μs时,短训练序列可以表示为s-2032:16:2032。其中,-2032、2032表示的是起始子载波的下标标号,16表示间隔。-2032:16:2032表示从下标为-2032的子载波开始每隔16个子载波到下标为2032的子载波。在其它子载波上,频域序列值为0。因此,上述短训练序列给出的这些值分别对应从下标为-2032的子载波开始每隔16个子载波到下标为2032的子载波的频域序列值。其中,l3、r3为与160mhz、周期长度为0.8μs所对应的短训练序列相关的序列。从而320mhz的短训练序列可以与160mhz的短训练序列兼容。且上述320mhz的短训练序列,可以支持大带宽(带宽大于160mhz)信道上的自动增益控制,并且经过仿真验证,这些短训练序列的峰均功率比较小,可以支持大带宽信道上的自动增益控制,并且可以提高接收端的自动增益控制电路的估计效果,从而降低接收误码率。

23、结合第一方面,在第一方面的某些实现方式中,所述目标信道的带宽为320mhz,当所述短训练字段包括的周期长度为1.6μs时,所述短训练序列表示为:

24、

25、其中,l2表示为{m,-1,m,-1,-m,-1,m},r2表示为{-m,1,m,1,-m,1,-m},-l2表示为{-m,1,-m,1,m,1,-m},-r2表示为{m,-1,-m,-1,m,-1,m}。

26、上述技术方案中,320mhz带宽共有4096个子载波,当短训练字段包括的周期长度为1.6μs时,短训练序列可以表示为s-2024:8:2024。其中,-2024、2024表示的是起始子载波的下标标号,8表示间隔。-2024:8:2024表示从下标为-2024的子载波开始每隔8个子载波到下标为2024的子载波。在其它子载波上,频域序列值为0。因此,上述短训练序列给出的这些值分别对应从下标为-2024的子载波开始每隔8个子载波到下标为2024的子载波的频域序列值。其中,l2、r2为与80mhz、周期长度为1.6μs时所对应的短训练序列相关的序列。从而320mhz的短训练序列可以与80mhz的短训练序列兼容。且上述320mhz的短训练序列,可以支持大带宽(带宽大于160mhz)信道上的自动增益控制,并且经过仿真验证,这些短训练序列的峰均功率比较小,可以支持大带宽信道上的自动增益控制,并且可以提高接收端的自动增益控制电路的估计效果,从而降低接收误码率。

27、结合第一方面,在第一方面的某些实现方式中,所述目标信道的带宽为320mhz,当所述短训练字段包括的周期长度为1.6μs时,所述短训练序列表示为:

28、

29、其中,l4表示为{m,-1,m,-1,-m,-1,m,0,-m,1,m,1,-m,1,-m},r4表示为{-m,1,-m,1,m,1-m,0,-m,1,m,1,-m,1,-m},-l4表示为{-m,1,-m,1,m,1,-m,0,m,-1,-m,-1,m,-1,m},-r4表示为{m,-1,m,-1,-m,-1,m,0,m,-1,-m,-1,m,-1,m}。

30、上述技术方案中,320mhz带宽共有4096个子载波,当短训练字段包括的周期长度为1.6μs时,短训练序列可以表示为s-2040:8:2040。其中,-2040、2040表示的是起始子载波的下标标号,8表示间隔。-2040:8:2040表示从下标为-2040的子载波开始每隔8个子载波到下标为2040的子载波。在其它子载波上,频域序列值为0。因此,上述短训练序列给出的这些值分别对应从下标为-2040的子载波开始每隔8个子载波到下标为2040的子载波的频域序列值。其中,l4、r4为与160mhz、周期长度为1.6μs时所对应的短训练序列相关的序列。从而320mhz的短训练序列可以与160mhz的短训练序列兼容。且上述320mhz的短训练序列,可以支持大带宽(带宽大于160mhz)信道上的自动增益控制,并且经过仿真验证,这些短训练序列的峰均功率比较小,可以支持大带宽信道上的自动增益控制,并且可以提高接收端的自动增益控制电路的估计效果,从而降低接收误码率。

31、第二方面,提供了一种发送短训练字段的装置,该装置包括:确定模块,用于确定短训练序列;发送模块,用于在目标信道上发送短训练字段,所述短训练字段是由所述短训练序列经过快速傅里叶逆变换ifft得到的,其中,所述目标信道的带宽大于160mhz。

32、第三方面,提供了一种发送短训练字段的装置,该装置包括:处理器,用于确定短训练序列;收发器,用于在目标信道上发送短训练字段,所述短训练字段是由所述短训练序列经过快速傅里叶逆变换ifft得到的,其中,所述目标信道的带宽大于160mhz。

33、第四方面,提供了一种处理器,包括:输入电路、输出电路和处理电路。所述处理电路用于通过所述输入电路接收信号,并通过所述输出电路发射信号,使得所述处理器执行第一方面以及第一方面任一种可能实现方式中的方法。

34、在具体实现过程中,上述处理器可以为芯片,输入电路可以为输入管脚,输出电路可以为输出管脚,处理电路可以为晶体管、门电路、触发器和各种逻辑电路等。输入电路所接收的输入的信号可以是由例如但不限于接收器接收并输入的,输出电路所输出的信号可以是例如但不限于输出给发射器并由发射器发射的,且输入电路和输出电路可以是同一电路,该电路在不同的时刻分别用作输入电路和输出电路。本技术实施例对处理器及各种电路的具体实现方式不做限定。

35、第五方面,提供了一种通信设备,其特征在于,包括:处理器,可选的,还包括存储器,所述存储器和处理器耦合,所述处理器用于执行上述第一方面以及第一方面任一种可能的实现方式中的方法。

36、可选地,所述处理器为一个或多个,所述存储器为一个或多个。

37、可选地,所述存储器可以与所述处理器集成在一起,或者所述存储器与处理器分离设置。

38、在具体实现过程中,存储器可以为非瞬时性(non-transitory)存储器,例如只读存储器(read only memory,rom),其可以与处理器集成在同一块芯片上,也可以分别设置在不同的芯片上,本技术实施例对存储器的类型以及存储器与处理器的设置方式不做限定。

39、可选地,所述处理器包括至少一个电路,用于确定短训练序列;包括至少一个电路,用于通过所述发射器发送所述短训练字段。

40、上述第五方面中的处理装置可以是一个芯片,该处理器可以通过硬件来实现也可以通过软件来实现,当通过硬件实现时,该处理器可以是逻辑电路、集成电路等;当通过软件来实现时,该处理器可以是一个通用处理器,通过读取存储器中存储的软件代码来实现,该存储器可以集成在处理器中,可以位于该处理器之外,独立存在。

41、第六方面,提供了一种计算机程序,当所述计算机程序被计算机执行时,用于执行上述第一方面以及第一方面任一种可能的实现方式中的方法。所述程序可以全部或者部分存储在与处理封装在一起的存储介质上,也可以部分或者全部存储在不与处理器封装在一起的存储器上。

42、第七方面,提供了一种计算机可读存储介质,该计算机可读存储介质存储有计算机程序,该计算机程序包含至少一段代码,该至少一段代码可由计算机执行,以控制所述计算机上述第一方面以及第一方面任一种可能的实现方式中的方法。

- 还没有人留言评论。精彩留言会获得点赞!