令牌添加数量的配置方法及装置、存储介质、电子设备与流程

本技术实施例涉及计算机领域,具体而言,涉及一种令牌添加数量的配置方法及装置、存储介质、电子设备。

背景技术:

1、令牌桶算法(token bucket)是流量整形(traffic shaping)和速率限制(ratelimiting)中最常用的一种算法,它可以控制数据传输的速率,即限制流量。

2、在该算法中,一个固定量的令牌(token)桶会以恒定的速率往其中添加令牌。同时,请求者可以从令牌桶中获取令牌,但是每次获取令牌后,请求者必须消耗掉一定量令牌。如果令牌桶中没有足够的令牌,则请求这无法获取令牌,从而限制了请求者的访问速率。一个令牌可以代表一个数据包,或者一个字节,如果代表一个数据包,那么令牌桶最终实现的就是pps整形,如果代表的是一个字节,那么令牌桶最终实现的就是bps整形。

3、具体地,令牌桶算法可以分为两个部分:令牌产生和令牌消耗。

4、其中,令牌产生实现的两个重要参数就是桶深和单次添加令牌的数量。周期性的添加令牌的方式是芯片设计实现的关键,令牌添加的策略直接决定了令牌桶的精度和限速的效果。

5、一般令牌桶算法的常见实现方案中,单次添加的令牌数量受时钟频率和配置速率的影响,不同的芯片设计需要根据时钟频率和限速范围定制化的给出单次添加的令牌数量的方案,因此复用性和继承性很差,不光给芯片设计带来了很大的工作量,同时也使得验证的复杂度大大提高。

6、针对相关技术,不同的芯片设计需要根据时钟频率和整形速率的范围定制化的给出单次的令牌添加数量的方案,因此复用性和继承性很差的问题,目前尚未提出有效的解决方案。

7、因此,有必要对相关技术予以改良以克服相关技术中的所述缺陷。

技术实现思路

1、本技术实施例提供了一种令牌添加数量的配置方法及装置、存储介质、电子设备,以至少解决相关技术中不同的芯片设计需要根据时钟频率和整形速率的范围定制化的给出单次的令牌添加数量的方案,因此复用性和继承性很差的问题。

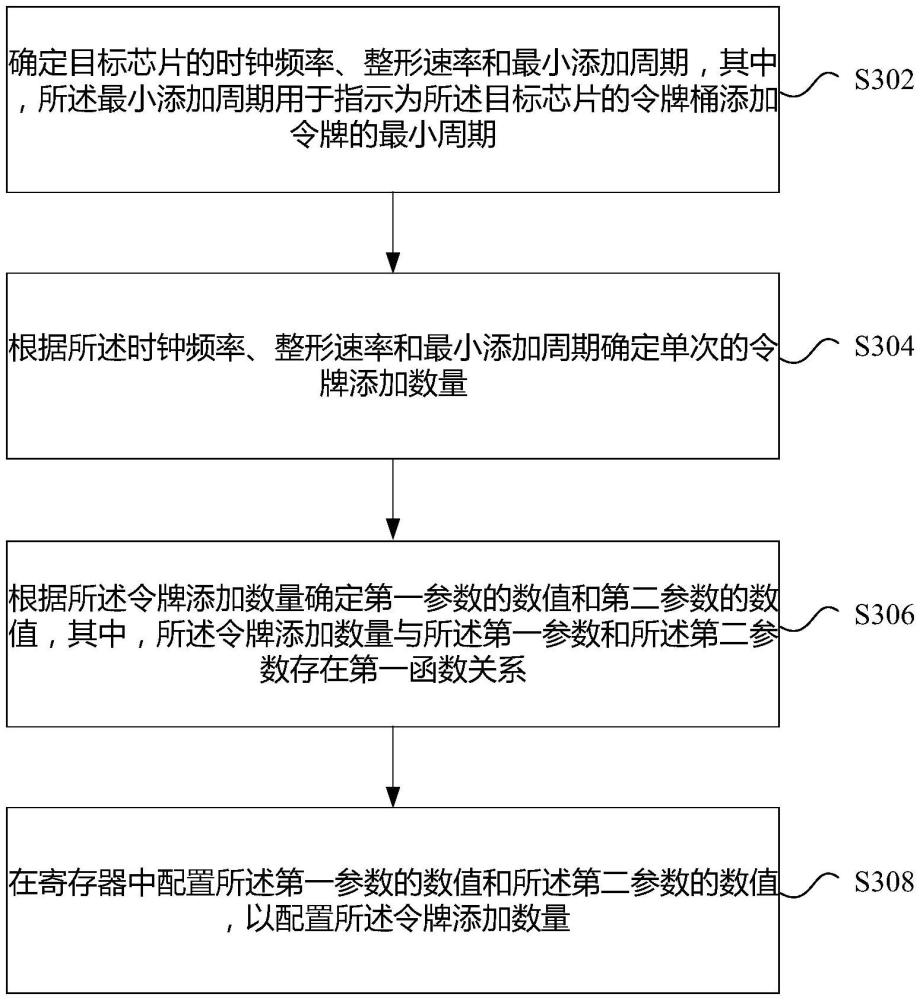

2、根据本技术的一个实施例,提供了一种令牌添加数量的配置方法,包括:确定目标芯片的时钟频率、整形速率和最小添加周期,其中,所述最小添加周期用于指示为所述目标芯片的令牌桶添加令牌的最小周期;根据所述时钟频率、整形速率和最小添加周期确定单次的令牌添加数量;根据所述令牌添加数量确定第一参数的数值和第二参数的数值,其中,所述令牌添加数量与所述第一参数和所述第二参数存在第一函数关系;在寄存器中配置所述第一参数的数值和所述第二参数的数值,以配置所述令牌添加数量。

3、在一个示例性实施例中,根据所述时钟频率、整形速率和最小添加周期确定单次的令牌添加数量,包括:根据所述最小添加周期确定目标添加周期;确定所述目标添加周期与所述整形速度的第一乘积,以及确定所述第一乘积与所述时钟频率的第一商值;根据所述第一商值确定所述令牌添加数量。

4、在一个示例性实施例中,根据所述令牌添加数量确定第一参数的数值和第二参数的数值,包括:确定所述令牌添加数量与目标数值的第二商值,以及确定所述第二商值与预设数值的第一大小关系;在所述第一大小关系指示所述第二商值大于或者等于所述预设数值的情况下,确定所述第二商值与所述目标数值的第三商值,以及确定所述第三商值与所述预设数值的第二大小关系;在所述第一大小关系指示所述第二商值小于所述预设数值的情况下,确定所述第二商值是否为目标类型的数值;在所述第二商值为所述目标类型的数值的情况下,确定所述第二商值与所述目标数值的第四商值,以及确定所述第四商值是否为所述目标类型的数值;在所述第二商值不是所述目标类型的数值的情况下,确定所述第二商值为所述第一参数的数值;确定所述令牌添加数量与所述第一参数的数值的第五商值;根据所述第五商值和所述目标数值确定所述第二参数。

5、在一个示例性实施例中,根据所述令牌添加数量确定第一参数的数值和第二参数的数值之后,所述方法还包括:确定所述令牌桶的桶深与所述令牌添加数量的倍数;根据所述倍数、所述第一参数的数值和所述第二参数的数值确定第三参数的数值和第四参数的数值,其中,所述桶深与所述第三参数和所述第四参数存在第二函数关系;在寄存器中配置所述第三参数的数值和所述第四参数的数值,以配置所述令牌桶的桶深。

6、在一个示例性实施例中,在寄存器中配置所述第一参数的数值和所述第二参数的数值之后,所述方法还包括:确定所述令牌桶对应的调度器的单层级的结点数量,其中,所述调度器为所述目标芯片的调度器;根据所述结点数量和所述最小添加周期确定为每个结点对应的令牌桶添加令牌的时间段;根据所述每个结点对应的时间段为所述每个结点的令牌桶添加所述令牌添加数量的令牌。

7、在一个示例性实施例中,根据所述每个结点对应的时间段为所述每个结点的令牌桶添加所述令牌添加数量的令牌之后,所述方法还包括:根据所述令牌添加数量与所述每个结点对应的令牌桶的令牌剩余数量确定所述每个结点对应的令牌桶的第一令牌总数量;确定所述第一令牌总数量是否大于所述每个结点对应的令牌桶的桶深;在所述第一令牌总数量大于所述每个结点对应的令牌桶的桶深的情况下,在所述每个结点对应的存储器中的目标字段写入所述桶深对应的数值,其中,所述目标字段用于指示所述每个结点对应的令牌桶的令牌数量;在所述第一令牌总数量小于或者等于所述每个结点对应的令牌桶的桶深的情况下,在所述每个结点对应的存储器中的目标字段写入所述第一令牌总数量对应的数值。

8、在一个示例性实施例中,在寄存器中配置所述第一参数的数值和所述第二参数的数值之后,所述方法还包括:在接收到芯片处理报文的情况下,在目标结点的令牌桶中获取目标数量的令牌;在获取到目标数量的令牌的情况下,确定是否存在对所述目标结点的存储器进行读写的目标操作;在不存在对所述目标结点的存储器进行读写的目标操作的情况下,根据所述目标数量与所述目标结点对应的令牌桶的令牌剩余数量确定所述目标结点对应的令牌桶的第二令牌总数量;在所述目标结点对应的存储器中的目标字段写入所述第二令牌总数量对应的数值。

9、根据本技术的另一个实施例,提供了一种令牌添加数量的配置装置,包括:第一确定模块,用于确定目标芯片的时钟频率、整形速率和最小添加周期,其中,所述最小添加周期用于指示为所述目标芯片的令牌桶添加令牌的最小周期;第二确定模块,用于根据所述时钟频率、整形速率和最小添加周期确定单次的令牌添加数量;第三确定模块,用于根据所述令牌添加数量确定第一参数的数值和第二参数的数值,其中,所述令牌添加数量与所述第一参数和所述第二参数存在第一函数关系;配置模块,用于在寄存器中配置所述第一参数的数值和所述第二参数的数值,以配置所述令牌添加数量。

10、根据本技术的又一个实施例,还提供了一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,其中,所述计算机程序被设置为运行时执行上述任一项方法实施例中的步骤。

11、根据本技术的又一个实施例,还提供了一种电子设备,包括存储器和处理器,所述存储器中存储有计算机程序,所述处理器被设置为运行所述计算机程序以执行上述任一项方法实施例中的步骤。

12、根据本技术的又一个实施例,还提供了一种计算机程序产品,包括计算机程序,所述计算机程序被处理器执行时实现上述任一项方法实施例中的步骤。

13、通过本技术中的系统,确定目标芯片的时钟频率、整形速率和最小添加周期,其中,所述最小添加周期用于指示为所述目标芯片的令牌桶添加令牌的最小周期;根据所述时钟频率、整形速率和最小添加周期确定单次的令牌添加数量;根据所述令牌添加数量确定第一参数的数值和第二参数的数值,其中,所述令牌添加数量与所述第一参数和所述第二参数存在第一函数关系;在寄存器中配置所述第一参数的数值和所述第二参数的数值,以配置所述令牌添加数量。在本技术实施例中,可以通过在寄存器中灵活配置第一参数和第二参数的数值,进而达到灵活配置单次的令牌添加数量,因此,可以解决相关技术中,不同的芯片设计需要根据时钟频率和整形速率的范围定制化的给出单次的令牌添加数量的方案,因此复用性和继承性很差的问题。本技术根据时钟频率、整形速率和最小添加周期确定时钟频率、整形速率和最小添加周期,在寄存器中配置所述第一参数的数值和所述第二参数的数值,以实现配置所述令牌添加数量,不会因为时钟频率的改变而修改令牌桶的实现方案,只需要调整寄存器中的参数,大大提高了这种方案的复用性。

- 还没有人留言评论。精彩留言会获得点赞!