一种基于Rossler混沌系统的芯片扫描测试加密电路及测试方法

本发明涉及集成电路测试技术,特别是集成电路可测试性设计安全性领域。

背景技术:

1、基于扫描链的jtag-dft测试方案,提高了集成电路的可控性和可观察性,方便了芯片的测试和维护,但也成为窃取寄存器内存储的重要信息、推测电路结构和实现细节等的后门,引入了不可忽视的隐患。为确保芯片测试的安全性,可在扫描测试时引入加密措施。

2、为有效抵抗扫描链的旁路攻击,一些安全扫描措施相继提出,列举如下:(1)扫描链结构乱序或混淆,如在串联的某些扫描寄存器之间额外插入非门;(2)测试芯片后切断扫描链,物理去除测试模式;(3)正常工作模式切换到测试模式时扫描寄存器清零;(4)使用扫描链测试前需输入预留密码验证(lock and key, l&k);(5)每条测试向量增设一组动态变化的密码进行验证;(6)基于物理不可克隆函数(puf)的加密方案;(7)基于线性反馈移位寄存器(lfsr)的测试向量加密方案等。

3、上述的扫描安全措施的不足如下。l&k方案较为简单,只在芯片进入测试模式时验证一次密码,安全强度有限。动态密码验证增大了破解难度和攻击成本,安全性更高,但每条测试向量都多出额外的数据流,小幅增加了测试时间。puf方案的环形振荡器等亚稳态电路,受芯片工作环境(如温度等)的影响,或因puf输出值不稳定而验证失败。近些年,已有针对线性lfsr的代数攻击和非线性fsr的立方攻击的报道,这类传统的流加密方案面临挑战。

4、为此,本专利提出一种基于rossler混沌系统的流密码加密方案。利用混沌系统高度的初值敏感性和非线性,提升扫描测试的安全性。其特点是:

5、(1)混沌系统的非线性特性有助于抵御针对经典流密码的攻击。本方案利用混沌系统的强非线性特点,能有效抵抗针对线性lfsr的代数攻击和非线性fsr的立方攻击。此外,混沌系统对模块参数敏感,即便微调某个参数,生成的随机序列也大不相同;能更有效的防止暴力破解。

6、(2)本方案可调参数丰富,加密方案的组合多样化,密钥空间广,能有效抵御暴力破解。

7、(3)rossler混沌系统的微分方程组中乘法少,电路的组合逻辑相对简单。

8、(4)混沌序列生成电路采用近似乘法器代替乘法器,电路面积减半;近似乘法虽降低了计算精度,但本模块目的是产生伪随机序列,并不要求硬件运算的高准确性。

9、(5)测试机上存储加密的测试向量及其响应,在芯片测试接口电路中完成加解密操作。测试机存储的都是加密后的密文数据,能有效预防攻击者通过测试厂泄露出的测试向量及其响应等数据来反推待测电路结构和功能等细节信息。

10、(6)测试中无需密码认证,操作时序更简便,节约测试时间。

11、(7)本方案与标准jtag接口兼容,可沿用现有的测试机设备和测试程序。

技术实现思路

1、为弥补上述芯片扫描测试方面的安全隐患,让芯片抵御借由扫描测试电路发起的攻击,提高芯片测试的安全性,本发明提供一种基于rossler混沌系统的芯片扫描测试加密电路及配套的测试方法。

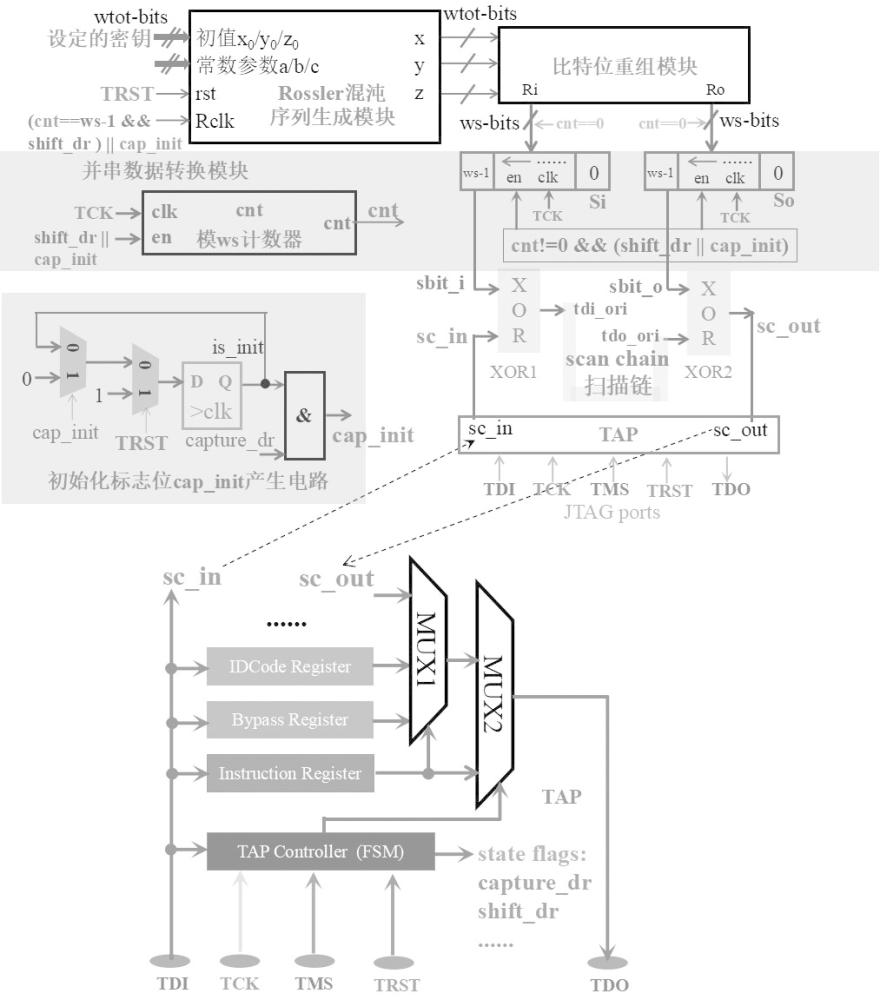

2、第一方面,本发明实施例提供的基于rossler混沌系统的芯片扫描测试加密电路,该混沌系统的微分方程组为,

3、,

4、其中x、y、z是待求的三组混沌序列,a、b、c为常数;其特征在于,包括:

5、rossler混沌序列生成模块,输出三组混沌序列x、y、z;

6、比特位重组模块,其输入是所述x、y、z,其输出是将输入的比特位重组的两组数据ri和ro;

7、内部或边界扫描链,是由扫描寄存器串接组成的链条;

8、基于ieee-1149协议的测试访问控制器tap,经入口端sc_in和出口端sc_out,挂载所述扫描链;

9、并串数据转换模块,其并行输入是ri和ro,其串行输出端口为sbit_i和sbit_o;

10、位于所述扫描链入口位置的、用于解密输入的测试向量的二输入端异或门xor1,一输入端接所述sbit_i,另一输入端接所述sc_in;

11、位于所述扫描链出口位置的、用于加密输出的测试向量响应的二输入端异或门xor2,一输入端接所述sbit_o,另一输入端接所述sc_out。

12、所述rossler混沌序列生成模块,采用差分算法实现,包括:

13、初值x0、y0和z0输入端口,总位宽均为wtot比特;

14、分别存储xyz序列当前值的寄存器组x、y和z,其时钟端口的输入均为脉冲信号rclk,总位宽均为wtot比特;所述xyz序列是等间隔时间点上的离散值;

15、rossler微分方程组右侧表达式对应的四则运算电路,其输入是所述xyz寄存器组的输出端q;

16、右移电路,将所述rossler微分方程组右侧表达式运算电路的输出结果右移整数dt比特位,以递推出步长为δt=2-dt的时间间隔后xyz的增量,即下一组xyz值相较于所述xyz寄存器组当前值的增量;

17、将所述xyz寄存器组的输出与所述xyz增量相加的加法电路,其输出为更新的下一组xyz序列值xnew、ynew和znew;

18、选通电路mux,由二选一数据选择器实现,其两个输入端,其一接所述初始值x0、y0和z0,其二接所述更新值xnew、ynew和znew截断的最高wtot比特位;当复位端trst(ieee-1149协议定义的测试端口)输入复位电平时,mux选通前者,否则选通后者;复位端连接trst

19、选通电路mux的输出,接所述x、y和z寄存器组的输入端口d。

20、所述rossler微分方程组右侧表达式对应的四则运算电路,包括:

21、采用近似定点乘法器代替定点乘法器,在不影响混沌效果的同时进一步减少电路面积;

22、为确保呈现出混沌轨迹效果,近似定点乘法器加入溢出限制功能,即乘法结果一旦超过定点数表示范围的上下限,要强制将计算结果钳位于上下限;

23、定点数x/y/z的最高位为符号位,小数部分位宽为wf;依rossler混沌解xyz的取值范围,整数部分位宽固定为5;故总位宽wtot=wf+6;

24、所述定点数小数部分位宽wf、所述近似乘法器的被乘数的有效位宽k、及前述整数dt均是本模块的可调参数,这些可调参数经组合能构造出xyz数值迥异的混沌序列,增加破解难度。

25、所述的rossler混沌序列生成模块,还包括微扰单元,插入于所述加法电路和所述选通电路mux之间,包括:

26、xnew/ynew/znew的最低2比特位记作xp/yp/zp,其翻转最为频繁、更具伪随机性,但因截断而未进入x/y/z寄存器去直接参与递推;在特定的xp/yp/zp取值下,触发x/y/z寄存器组的最低比特位翻转,以加剧x/y/z序列的复杂度和不可预测性,更难破解;

27、所述特定的xp/yp/zp取值如,若xp各比特位均为1,触发x寄存器组最低比特位翻转。

28、所述比特位重组模块,包括:

29、将所述rossler混沌序列生成电路输出的x/y/z定点数序列,经打乱高低比特位顺序、交叉组合、逻辑运算生成新值等方式,生成位宽3×wtot的伪随机序列,再将其从中间对半分成两组位宽各为ws=3×wtot/2比特的二进制码ri和ro;

30、定点数位宽为wtot时,比特乱序生成的伪随机序列,按w≤wtot/3比特一组分割出的0~2w-1范围内的整数,取值为0~2w-1的频率分布均匀;增大电路参数wf,可提高伪随机序列的长程性,但电路面积大。

31、本模块通过乱序重组混沌序列xyz的比特位,来提高暴力破解难度;且能让伪随机序列中0和1的占比近似各半,攻击者难以从中统计出有效信息。

32、所述并串数据转换模块,包括:

33、位宽为ws的移位寄存器组,用于存放所述比特位重组模块的两组输出ri和ro;在tap处于shift_dr态(ieee-1149协议中状态机的状态之一)的每个时钟周期,或在tap复位后首次进入capture_dr态(ieee-1149协议中状态机的状态之一)时的一个时钟周期,触发一次移位;

34、模ws计数器,计数范围0~ws-1,用于控制移位寄存器组si和so的并串转换;且在所述shift_dr态下,当计数一轮后,生成所述rclk脉冲信号,用于触发所述混沌序列生成模块的xyz寄存器组进行一次递推。

35、所述的基于rossler混沌系统的芯片扫描测试加密电路,还包括初始化标志位cap_init产生电路;当所述tap复位后,tap首次进入capture_dr态时,此电路让cap_init信号置位,以在此时使能所述模ws计数器、及所述si和so移位寄存器组;

36、其作用是,让电路复位初始化后,第一次进入shift_dr态前,所述混沌序列生成模块能触发一次递推,让移位寄存器组si和so能加载由初值x0/y0/z0递推出的第1组序列,而非直接加载初值;此举能提高加解密电路的安全性,即便通过版图逆向而拿到初值x0/y0/z0等密钥信息,若不了解混沌生成算法的细节和电路参数设置,也难以推出第一批次的si和so的值。

37、第二方面,本发明实施例提供的基于rossler混沌系统的芯片扫描加密测试方法,如下:

38、步骤1,电脑上仿真得出混沌伪随机序列,包括:

39、步骤1.1,确定各模块的可调参数,即所述wf//k/dt/x0/y0/z0/a/b/c等;

40、步骤1.2,据此运行电路仿真,递推m个时间步,算出每个时间步下混沌系统的输出x/y/z,进而得出各时间步对应的伪随机数ri和ro。

41、步骤2,电脑上准备加密的测试向量及其响应,由原始的测试向量及其响应与仿真出的混沌伪随机序列逐比特异或得到;包括:

42、步骤2.1,将某条测试向量及其响应分段,每段长ws比特,共m段;

43、步骤2.2,若该条测试向量及其响应的长度,不能被m整除,测试向量开头部分补0,向量的响应结尾部分补0,使这些向量长度l能被m整除;

44、步骤2.3,将第i段(i=0~m-1)测试向量与第i个时间步的ri按位异或,得第i个加密片段;

45、步骤2.4,将这m个加密片段按顺序拼接,即得加密的测试向量;

46、步骤2.5,加密测试向量响应的方法类似,区别是每段数据是与ro异或;

47、步骤2.6,测试机上的测试程序中,只需将测试向量及其响应的明文替换成加密的,涉及tap状态机状态跳转的时序流程并无改动。

48、步骤3,在tap状态机处于所述shift_dr态时,由tdi端口灌入上述加密的测试向量,同时测试机从tdo端口获取加密的上一条测试向量的响应;

49、步骤4,测试机上,将tdo端口读取的加密测试向量的响应,与测试机存储的加密测试向量的响应对比,若一致则此条测试向量通过,否则不通过。

- 还没有人留言评论。精彩留言会获得点赞!