一种面向TLS应用的存算系统及加速方法与流程

本发明属于数据读写,具体涉及面向tls应用的存算系统及加速方法。

背景技术:

1、随着信息技术的飞速发展,互联网已成为人们生活、工作中不可或缺的一部分。为了保护数据传输的安全,transport layer security(tls)协议被广泛应用于互联网通信中;tls通过使用加密算法来保护数据,从而防止数据在传输过程中被窃听或篡改。

2、然而,随着网络流量的不断增长,tls协议的实施带来了显著的性能开销。在web服务器等需要处理大量并发tls连接的场景中,tls操作对中央处理单元(cpu)的高需求成为了系统性能的瓶颈。

3、业界在优化tls性能上已经做了很多软件和协议层面的优化,包括:session复用、ocsp stapling、tls1.3协议等。尽管这些软件层面的优化在一定程度上提高了tls的性能,但在摩尔定律逐渐放缓的今天,单纯依靠软件优化已经难以满足日益增长的性能需求。

技术实现思路

1、本发明提供了一种面向tls应用的存算系统及加速方法,提高web服务器中计算密集的公钥加密以及数据压缩/解压的吞吐率,同时降低cpu的负载。

2、为达到上述目的,本发明所采用的技术方案是:

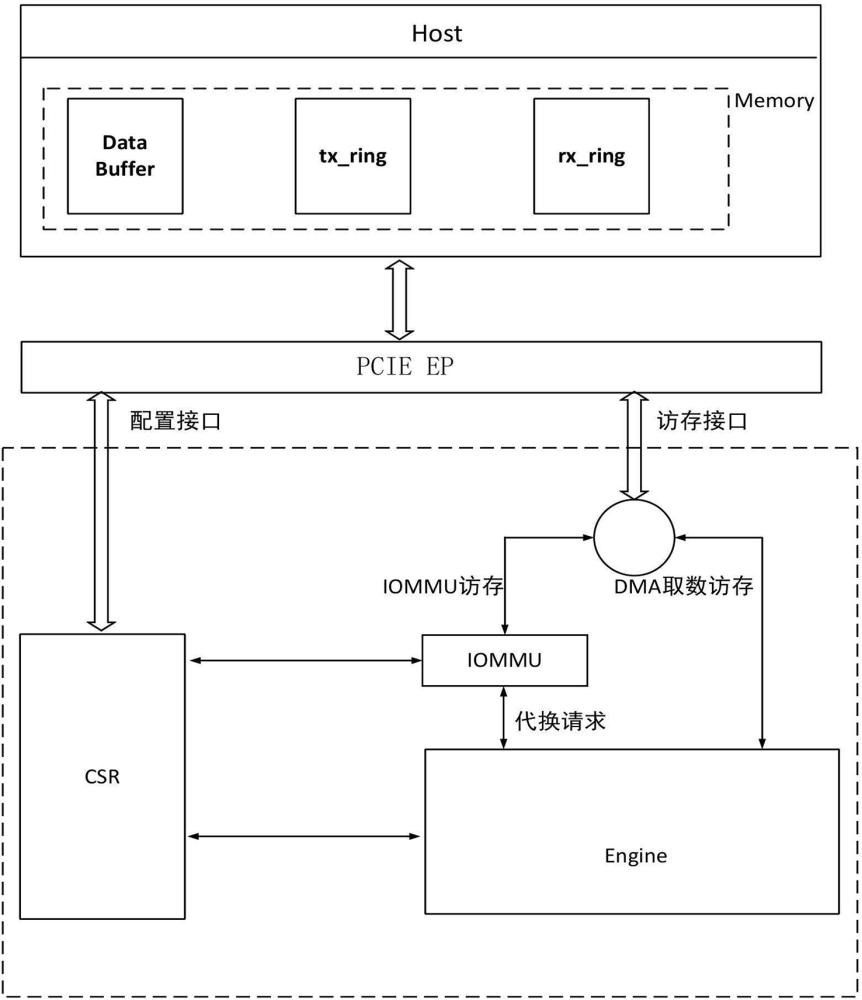

3、本发明第一方面提供了一种面向tls应用的存算系统,包括相互电性连接的寄存器控制模块csr、地址代换模块iommu和数据处理引擎;寄存器控制模块csr、地址代换模块iommu和数据处理引擎通过终端设备picie ep电性连接主存储器;

4、所述主存储器用于存储接收描述符、发送描述符和原始数据;

5、所述寄存器控制模块csr用存储所述发送描述符的head值和存储地址以及接收描述符的tail值;

6、所述地址代换模块iommu用于根据地址代换请求生成物理地址;

7、所述数据处理引擎,用于生成地址代换请求并发送至地址代换模块iommu,根据物理地址由主存储器读取发送描述符或原始数据;对原始数据压缩或解压处理、加密或解密处理后写入到主存储器;

8、响应于完成原始数据写入主存储器后,所述数据处理引擎生成接收描述符和中断信息;将接收描述符存储至主存储器,将接收描述符的tail值和中断信息登记至寄存器控制模块csr。

9、进一步的,所述数据处理引擎根据发送描述符的head值和存储地址生成发送描述符的地址代换请求;所述地址代换模块iommu根据发送描述符的地址代换请求生成所述发送描述符的物理地址和数据长度并反馈至所述数据处理引擎;

10、所述数据处理引擎根据所述发送描述符的物理地址和数据长度由主存储器中读取发送描述符,对发送描述符进行解析获得原始数据的存放地址和数据长度并生成原始数据的地址代换请求;

11、所述地址代换模块iommu根据原始数据的地址代换请求生成原始数据的物理地址和数据长度并反馈至所述数据处理引擎;

12、所述数据处理引擎根据原始数据的物理地址和数据长度由主存储器中读取原始数据。

13、进一步的,所述数据处理引擎包括读写描述符控制逻辑模块、描述符解析模块、dma控制器和算法ip模块;

14、所述读写描述符控制逻辑模块电性连接寄存器控制模块csr;所述读写描述符控制逻辑模块用于读取所述发送描述符的head值和存储地址,根据发送描述符的head值和存储地址生成发送描述符的地址代换请求,将接收描述符的tail值存储至寄存器控制模块csr;

15、所述描述符解析模块用于对发送描述符进行解析获得原始数据的存放地址和数据长度并生成原始数据的地址代换请求;

16、所述dma控制器用于与主存储器交互数据;

17、算法ip模块用于对原始数据进行压缩或解压处理、加密或解密处理。

18、进一步的,所述dma控制器包括读数据模块rdma和写数据模块wdma;

19、所述读数据模块rdma用于根据所述发送描述符的物理地址和数据长度由主存储器中读取发送描述符,根据原始数据的物理地址和数据长度由主存储器中读取原始数据;

20、所述写数据模块wdma将原始数据压缩或解压处理、加密或解密处理后写入到主存储器,将接收描述符存储至主存储器。

21、进一步的,所述算法ip模块用于执行对称加解密算法ip,非对称加解密算法ip,数据压缩算法ip和数据解压算法ip。

22、进一步的,所述算法ip模块通过转换接口电性连接dma控制器和ram寄存器;所述转换接口包括上游转换接口和下游转换接口;所述上游转换接口负责ram寄存器至算法ip模块的数据转换;所述下游转换接口负责算法ip模块至ram寄存器的数据转换。

23、进一步的,ram寄存器的数据位宽为128bits,所述算法ip模块中数据压缩算法ip的数据输入接口为64bits,数据解压算法ip的数据输入接口为16bits,数据加解密算法ip的数据输入接口为32bits;数据压缩算法ip和数据解压算法ip的数据输出接口为64bits,加解密算法ip的输出数据位宽是32bits。

24、进一步的,寄存器控制模块csr包括地址寄存器,head寄存器、tail寄存器和中断寄存器;

25、所述地址寄存器记录所述主存储器中tx-ring发送队列和rx_ring接收队列的存储地址;

26、所述head寄存器用于存储所述发送描述符的head值;

27、所述tail寄存器用于存储所述接收描述符的tail值;

28、所述中断寄存器用于存储所述中断信息。

29、本发明第二方面提供了一种面向tls应用的存算加速方法,采用第一方面所述的存算系统执行所述存算方法,包括:

30、响应于主存储器存储发送描述符和原始数据;更新寄存器控制模块csr中存储所述发送描述符的head值和存储地址;

31、根据发送描述符的head值和存储地址生成发送描述符的地址代换请求并发送至所述地址代换模块iommu;根据发送描述符的地址代换请求生成所述发送描述符的物理地址和数据长度并反馈至所述数据处理引擎;

32、根据所述发送描述符的物理地址和数据长度由主存储器中读取发送描述符,对发送描述符进行解析获得原始数据的存放地址和数据长度并生成原始数据的地址代换请求并发送至所述地址代换模块iommu;

33、根据原始数据的地址代换请求生成原始数据的物理地址和数据长度并反馈至所述数据处理引擎;

34、根据原始数据的物理地址和数据长度由主存储器中读取原始数据,对原始数据压缩或解压处理、加密或解密处理后写入到主存储器;

35、响应于完成原始数据写入主存储器后生成接收描述符和中断信息;将接收描述符存储至主存储器中rx_ring接收队列,将接收描述符的tail值和中断信息登记至寄存器控制模块csr。

36、进一步的,对原始数据压缩或解压处理、加密或解密处理后写入到主存储器,过程包括:

37、对原始数据压缩或解压处理、加密或解密处理后写入到ram寄存器;dma控制器由ram寄存器读取算法ip模块的输出数据并写入到主存储器。

38、进一步的,根据发送描述符的head值和存储地址生成发送描述符的地址代换请求,过程包括:

39、将发送描述符的存储地址加上偏移量128 bits获得发送描述符的真实存储地址,根据发送描述符的head值和真实存储地址生成发送描述符的地址代换请求。

40、与现有技术相比,本发明的有益效果:

41、本发明所述数据处理引擎生成地址代换请求并发送至地址代换模块iommu;所述地址代换模块iommu根据地址代换请求生成物理地址;所述数据处理引擎根据物理地址由主存储器读取发送描述符或原始数据,对原始数据压缩或解压处理、加密或解密处理后写入到主存储器;将数据的地址代换和处理逻辑移至专门的硬件模块,优化了cpu和内存资源的利用,使得系统能够更高效地处理更多的并发连接。

42、本发明数据处理引擎包括读写描述符控制逻辑模块、描述符解析模块、dma控制器和算法ip模块,数据处理引擎能够快速处理大量的描述符和数据,提升了系统处理高速网络流量的能力;由于数据处理过程大部分在硬件层面完成,减少了软件层面的延迟,从而在整体上降低了网络通信的延迟。

- 还没有人留言评论。精彩留言会获得点赞!