一种视频直方图均衡处理电路和芯片的制作方法

本发明涉及芯片设计,尤其涉及一种视频直方图均衡处理电路和芯片。

背景技术:

1、直方图均衡处理是图像处理领域中利用图像直方图对对比度进行调整的方法,通过这种方法,亮度可以更好地在直方图上分布,从而增加图像的全局对比度。

2、普通常规的直方图均衡处理的方法,是针对静态图片,用软件分析的处理方法,将原始图片进行分析并写出处理后静态图片的方式。针对动态视频,常规的直方图均衡处理的方法需要将视频转换为若干帧图像,再对图像进行处理,处理过程较复杂。

技术实现思路

1、本发明提供了一种视频直方图均衡处理电路和芯片,以解决现有技术中针对静态图片用软件分析的处理方式导致处理过程较复杂的问题。

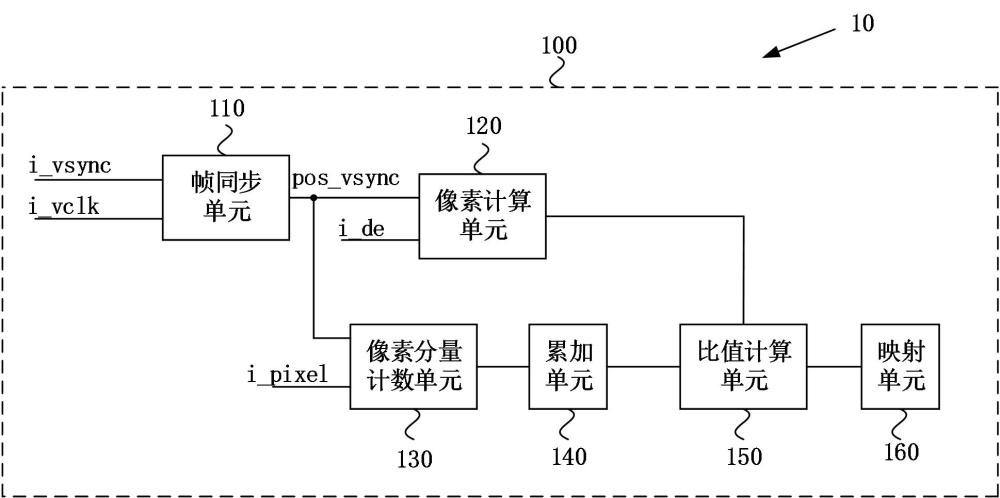

2、根据本发明的一方面,提供了一种视频直方图均衡处理电路,所述视频直方图均衡处理电路包括核心处理电路,所述核心处理电路包括帧同步单元、像素计算单元、像素分量计数单元、累加单元、比值计算单元和映射单元;

3、所述帧同步单元接入同步信号和时钟信号,所述帧同步单元用于根据所述同步信号和时钟信号输出帧同步信号;

4、所述像素计算单元连接所述帧同步单元,所述像素计算单元用于根据输入的数据使能信号和所述帧同步信号计算本帧总像素个数;

5、所述像素分量计数单元连接帧同步单元,所述像素分量计数单元用于对接入的当前像素值进行计数;

6、所述累加单元连接所述像素分量计数单元,所述累加单元用于根据所述像素分量计数单元输出的数据进行累加;

7、所述比值计算单元连接所述累加单元和所述像素计算单元,所述比值计算单元用于计算所述累加单元输出的数据与所述像素计算单元输出的数据的比值;

8、所述映射单元连接所述比值计算单元,所述映射单元用于根据所述比值计算单元输出的上一帧数据将输入的像素值映射为预设值。

9、可选的,所述帧同步单元包括第一触发器、非门电路和第一与门电路,所述第一触发器的输入端接入所述同步信号,所述第一触发器的时钟端接入所述时钟信号,所述第一触发器的输出端连接所述非门电路的输入端,所述第一与门电路的第一输入端连接所述非门电路的输出端,所述第一与门电路的第二输入端连接所述第一触发器的输入端,所述第一与门电路的输出端输出所述帧同步信号。

10、可选的,所述像素计算单元包括第一或门电路、第一加法器、第一数据选择器、第二触发器和第三触发器,所述第一或门电路的第一输入端连接所述第一与门电路的输出端和所述第一数据选择器的控制端,所述第一或门电路的第二输入端接入所述数据使能信号,所述第二触发器的时钟端和所述第三触发器的时钟端接入所述时钟信号,所述第二触发器的使能端和所述第三触发器的使能端连接所述第一或门电路的输出端,所述第二触发器的输入端连接所述第一数据选择器的输出端,所述第二触发器的输出端连接所述第三触发器的输入端和所述第一加法器的第一输入端,所述第三触发器的输出端连接所述像素计算单元的输出端,所述第一加法器的第二输入端输入逻辑1,所述第一数据选择器的第一输入端连接所述第一加法器的输出端,所述第一数据选择器的第二输入端输入逻辑0。

11、可选地,所述像素分量计数单元包括第一判断模块、第二与门电路、第二或门电路、第二数据选择器、第二加法器、第四触发器和第五触发器,所述第一判断模块的第一输入端连接所述像素分量计数单元的输入端,所述第一判断模块的第二输入端输入像素值变量,所述第一判断模块的输出端连接所述第二与门电路的第一输入端,所述第二与门电路的第二输入端接入所述数据使能信号,所述第二与门电路的输出端连接所述第二或门电路的第一输入端,所述第二或门电路的第二输入端、所述第二数据选择器的控制端和所述第五触发器的使能端连接所述帧同步单元的输出端,所述第二数据选择器的第一输入端连接所述第二加法器的输出端,所述第二数据选择器的第二输入端输入逻辑0,所述第二数据选择器的输出端连接所述第四触发器的输入端,所述第二或门电路的输出端连接所述第四触发器的使能端,所述第四触发器的输出端连接所述第五触发器的输入端和所述第二加法器的第一输入端,所述第二加法器的第二输入端输入逻辑1,所述第四触发器的时钟端和所述第五触发器的时钟端接入所述时钟信号,所述第五触发器的输出端连接所述像素分量计数单元的输出端。

12、可选的,所述累加单元包括第二判断模块、第三数据选择器和第三加法器,所述第二判断模块的第一端输入所述像素值变量,所述第二判断模块的第二端输入逻辑0,所述第二判断模块的输出端连接所述第三数据选择器的控制端,所述第三数据选择器的第一输入端连接所述第三加法器的输出端,所述第三数据选择器的第二输入端输入逻辑0,所述第三数据选择器的输出端连接所述第三加法器的第一输入端,所述第三加法器的第二输入端连接所述像素分量计数单元,所述第三加法器的输出端连接所述累加单元的输出端。

13、可选的,所述比值计算单元包括左移模块、减法器、第四数据选择器、第五数据选择器、第六触发器、第七触发器、第三或门电路、第四或门电路、第三判断模块、第四判断模块和第四加法器,所述左移模块的输入端连接所述第三加法器的输出端,所述左移模块的输出端连接所述第四数据选择器的第一输入端,所述第四数据选择器的第二输入端连接所述减法器的输出端,所述第四数据选择器的输出端连接所述第六触发器的输入端,所述第六触发器的输出端连接所述减法器的第一输入端,所述减法器的第二输入端连接所述像素计算单元的输出端,所述第三或门电路的第一输入端连接所述第四数据选择器的控制端和所述像素计算单元的输入端,所述第三或门电路的第二输入端连接所述第三判断模块的输出端,所述第三判断模块的第一输入端连接所述第六触发器的输出端,所述第三判断模块的第二输入端连接所述像素计算单元的输出端,所述第三或门电路的输出端连接所述第六触发器的使能端,所述第六触发器的时钟端接入所述时钟信号;所述第四判断模块的第一输入端连接所述第六触发器的输出端,所述第四判断模块的第二输入端连接所述像素计算单元的输出端,所述第四判断模块的输出端连接所述第四或门电路的第一输入端,所述第四或门电路的第二输入端连接所述像素计算单元的输入端和所述第五数据选择器的控制端,所述第四或门电路的输出端连接所述第七触发器的使能端,所述第七触发器的输出端连接所述比值计算单元的输出端和所述第四加法器的第一输入端,所述第四加法器的第二输入端输入逻辑1,所述第四加法器的输出端连接所述第五数据选择器的第一输入端,所述第五数据选择器的第二输入端输入逻辑0,所述第五数据选择器的输出端连接所述第七触发器的输入端,所述第七触发器的时钟端接入所述时钟信号。

14、可选的,所述映射单元包括第五判断模块、第六数据选择器、第七数据选择器、第一右移模块、第八触发器和第五加法器,所述第五判断模块的第一输入端输入所述像素值变量,所述第五判断模块的第二输入端输入逻辑0,所述第五判断模块的输出端连接所述第六数据选择器的控制端,所述第六数据选择器的第一输入端连接所述比值计算单元的输出端,所述第六数据选择器的第二输入端输入逻辑0,所述第六数据选择器的输出端连接所述第八触发器的输入端,所述第八触发器的使能端连接所述像素分量计数单元,所述第八触发器的时钟端接入所述时钟信号,所述第八触发器的输出端连接所述第一右移模块的输入端和所述第五加法器的第一输入端,所述第一右移模块的输出端连接所述第五加法器的第二输入端,所述第五加法器的输出端连接所述第七数据选择器的第一输入端和所述第七数据选择器的控制端,所述第七数据选择器的第二输入端输入255,所述第七数据选择器的输出端连接所述映射单元的输出端。

15、可选的,所述核心处理电路还包括对比度判断单元、第八数据选择器和第九触发器,所述对比度判断单元连接所述像素分量计数单元和所述像素计算单元,所述对比度判断单元用于根据所述像素分量计数单元输出的数据和所述像素计算单元输出的数据判断图像对比度;所述第八数据选择器的控制端连接所述对比度判断单元的输出端,所述第八数据选择器的第一输入端连接所述比值计算单元的输出端,所述第八数据选择器的第二输入端连接所述第九触发器的输出端,所述第九触发器的输入端连接所述像素分量计数单元的输入端,所述第九触发器的时钟端接入所述时钟信号,所述第八数据选择器用于根据所述对比度判断单元输出的信号选择导通路径。

16、可选的,所述视频直方图均衡处理电路还包括第一颜色空间转换单元、第二颜色空间转换单元、第九数据选择器、第十数据选择器、第十触发器和第十一触发器,所述第九数据选择器的控制端接入模式选择信号,所述第九数据选择器的第一输入端连接所述第一颜色空间转换单元的输入端,所述第九数据选择器的第二输入端连接所述第一颜色空间转换单元的输出端,所述第九数据选择器的输出端连接所述核心处理电路的输入端,所述第九数据选择器用于根据所述模式选择信号选择导通路径;所述第一颜色空间转换单元输入端接入视频流信号,所述第一颜色空间转换单元用于将rgb色彩空间转换为yuv色彩空间,所述第一颜色空间转换单元输出端连接所述第十触发器的输入端和所述第十一触发器的输入端,所述第十触发器的输出端、所述第十一触发器的输出端和所述核心处理电路的输出端连接所述第二颜色空间转换单元的输入端,所述第二颜色空间转换单元用于将所述yuv色彩空间转换为所述rgb色彩空间,所述第十触发器的时钟端和所述第十一触发器的时钟端接入所述时钟信号;所述第十数据选择器的第一输入端连接所述核心处理电路的输出端,所述第十数据选择器的第二输入端连接所述第二颜色空间转换单元的输出端,所述第十数据选择器的控制端接入所述模式选择信号,所述第十数据选择器用于根据所述模式选择信号选择导通路径。

17、根据本发明的另一方面,提供了一种芯片,包括所述视频直方图均衡处理电路。

18、本发明实施例的技术方案,提供了一种视频直方图均衡处理电路,其核心处理电路包括帧同步单元、像素计算单元、像素分量计数单元、累加单元、比值计算单元和映射单元;帧同步单元根据同步信号和时钟信号输出帧同步信号,像素计算单元根据数据使能信号和帧同步信号计算本帧总像素个数,像素分量计数单元对当前像素值进行计数,累加单元根据像素分量计数单元输出的数据进行累加,比值计算单元计算累加单元输出的数据与像素计算单元输出的数据的比值,映射单元根据比值计算单元输出的上一帧数据将输入的像素值映射为预设值,能够实现实时输出直方图均衡处理后的帧,即对动态视频流进行处理,同时,视频直方图均衡处理电路可综合为网表烧入芯片内,具有处理速度快、效率高的优点,解决了现有技术中针对静态图片用软件分析的处理方式导致处理过程较复杂的问题。

19、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

- 还没有人留言评论。精彩留言会获得点赞!