国密算法系统架构及国密算法封装系统的制作方法

本发明涉及数据安全领域,具体涉及一种国密算法系统架构及国密算法封装系统。

背景技术:

1、随着信息技术的飞速发展,信息安全在金融、医疗和政府单位等关键领域越来越重要。国密算法作为国产的密码算法标准,是实现信息安全的关键技术之一。但是,现有架构在对数据进行解密或者加密运算的过程中,业务运算过程中的上下文通信,均需通过处理器控制软件进行数据传输,从而导致处理器的负载占用率较高,以影响加密运算或解密运算的整体效率。

技术实现思路

1、有鉴于此,本发明提供了一种国密算法系统架构及国密算法封装系统,用于解决由于处理器控制软件进行上下文数据的通信传输导致处理器的负载占用率较高,以影响加密运算或解密运算的整体效率的问题。

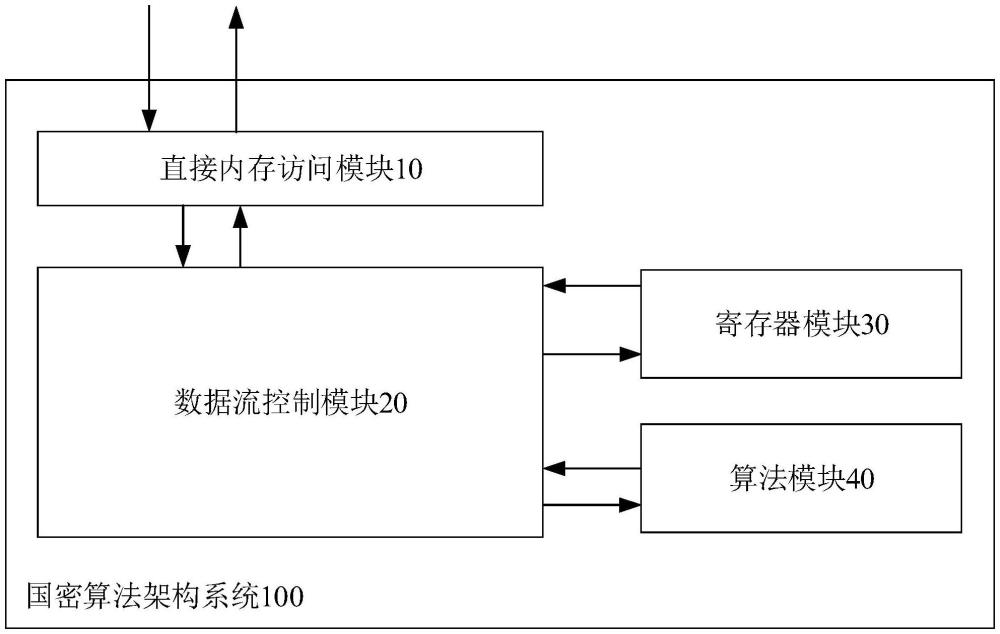

2、第一方面,本发明提供了一种国密算法系统架构,包括直接内存访问模块、数据流控制模块、寄存器模块以及算法模块。直接内存访问模块用于调取内存数据。数据流控制模块与直接内存访问模块通信连接。寄存器模块与数据流控制模块通信连接,寄存器模块用于存储秘钥信息和参数信息。算法模块与数据流控制模块通信连接,算法模块用于对数据流控制模块内的第一预设数据进行加密或者解密运算。其中,数据流控制模块与直接内存访问模块之间通过数据帧的模式进行数据交互通信。

3、有益效果:本发明实施例所提供的国密算法系统架构中,直接内存访问模块能够直接对内存模块进行访问,从而调取内存数据,以将调取的内存数据与数据流控制模块进行交互通信。在数据流控制模块内,数据流控制模块可以通过寄存器模块进行秘钥信息和参数信息的配置,并通过算法模块调取相应的算法以对第一预设数据进行加密运算或者解密运算,从而通过国密算法以对第一预设数据进行加密或者解密操作,以保障信息安全。

4、在此基础上,在直接内存访问模块与数据流控制模块之间进行数据交互通信的过程中,数据流控制模块与直接内存访问模块之间通过数据帧方式进行数据传输。即国密算法的运算过程中,算法所需的参数配置和业务运算的上下文通信,在直接内存访问模块与数据流控制模块之间均能够通过数据帧的方式交互通信,即大量数据的交互通信是通过硬件进行调度传输的,无需软件的参与。此方式减少了主机参与,能够解放主控模块等处理器的压力,有利于提升国密系统在运算过程中的整体效率。

5、并且,由于直接内存访问模块自身的硬件特性,以使外设在调取内存模块内数据的过程中,无需主控模块等处理器的干预。从而使得内存模块和直接内存访问模块这一外设之间能够进行高速的数据传输,同样能够进一步解放主控模块等处理器的压力,有利于提升国密系统在运算过程中的整体效率。

6、在一些实施方式中,直接内存访问模块包括数据输入缓存、数据输出缓存、第一状态控制器、下行组帧单元以及上行解帧单元。数据输入缓存用于缓存发送至数据流控制模块的下行数据信息。数据输出缓存用于缓存由数据流控制模块的接收的上行数据信息。第一状态控制器与数据输入缓存和数据输出缓存通信连接,以控制下行数据信息的下发和上行数据信息的回收。下行组帧单元用于将下行数据信息重组为下行数据帧。上行解帧单元用于解析上行数据帧,并将解析获取的上行数据信息缓存至数据输出缓存内。

7、有益效果:通过第一状态控制器能够控制直接内存访问模块的运行状态,如控制下行数据信息的下发以及上行数据信息的回收。示例性的,当第一状态控制器检测到数据输入缓存不为空时,控制下行组帧单元将数据输入缓存内的下行数据信息重组为下行数据帧,用于快速下发至数据流控制模块处。当第一状态控制器检测到上行传输单元不为空时,第一状态控制器控制上行解帧单元接收上行数据帧并将之进行解析,从而解析获取上行数据信息,并将之缓存至数据输出缓存内。如上行数据信息可以是将第一预设数据进行加密运算或者解密运算后数据信息。

8、在一些实施方式中,数据流控制模块包括下行帧缓存,运算数据缓存、第二状态控制器、帧头解析单元、下行校验单元、上行组帧单元以及上行传输单元。下行帧缓存用于接收并缓存下行数据帧。运算数据缓存用于对算法模块运算后的第二预设数据进行接收并缓存。第二状态控制器与下行帧缓存和运算数据缓存通信连接。帧头解析单元用于解析下行数据帧并向第二状态控制器反馈解析信息。下行校验单元用于校验下行数据帧的帧头。上行组帧单元用于将第二预设数据重组为上行数据帧。上行传输单元用于将上行数据帧传输至上行解帧单元。

9、有益效果:即通过第二状态控制器能够直接控制数据流控制模块的运行状态。帧头解析单元通过解析下行数据帧,以获取该下行数据帧传输的业务类型、算法类型、数据长度/参数长度等信息,并将上述信息反馈至第二状态控制器。当算法模块对第一预设数据进行加密或解密运算后,以将加密或者解密运算后的第二预设数据缓存至运算数据缓存内,以使上行组帧单元将第二预设数据重组为上行数据帧,以便于上行传输单元能够将上行数据帧快速传输至直接内存访问模块的上行解帧单元处进行解帧。

10、基于此,在本发明实施例中,通过在直接内存访问模块与数据流控制模块之间配置数据帧的交互通信结构,以使内存访问模块与数据流控制模块之间通过数据帧的方式进行大量数据交互的过程中只需硬件结构调度配置即可,无需软件参与。从而减少了主机参与,能够解放主控模块等处理器的压力,有利于提升国密系统在运算过程中的整体效率。

11、在一些实施方式中,下行数据帧包括管理帧以及业务帧。管理帧包括管理帧头和管理信息,管理信息用于配置秘钥信息和参数信息。业务帧包括业务帧头和第一预设数据。

12、有益效果:通过管理帧的设置,便于数据流控制模块内进行初始化或者更新配置秘钥。通过业务帧的设置,在加密或者解密运算的过程中,业务帧头能够用于指示执行那种业务,如加/解密、哈希、签名和验签等运算流程,有利于第一预设数据的快速稳定传输。

13、在一些实施方式中,直接内存访问模块还包括管理寄存器、描述符缓存以及描述符处理单元。管理寄存器与第一状态控制器通信连接。描述符缓存与第一状态控制器通信连接,管理寄存器控制读取描述符链表并缓存至描述符缓存内。描述符处理单元与描述符缓存和第一状态控制器通信连接。第一状态控制器被配置为:

14、当描述符缓存非空时,第一状态控制器启动描述符处理单元由描述符缓存读取描述符链表,以至少获取内存首地址信息和业务类型信息。

15、有益效果:由于内存模块内缓存的数据、参数等信息在物理层面上并非一定处于连续区域,通过描述符缓存以及描述符处理单元的设置,以使直接内存访问模块为链式结构,以便于直接内存访问模块通过符链表对内存模块内不连续区域的数据进行读取传输。

16、即通过上述结构,允许第一预设数据分散存储在多个非连续的内存模块的区域中,并通过描述符链表进行组织,因此它可以减少数据传输过程中的中断次数,从而提高了传输效率。而普通dma在传输完一块物理连续的数据后通常需要发起一次中断,然后由主机进行下一块数据的传输,这种方式会引入额外的开销。

17、由于在由内存模块中读取数据的传输过程中减少了中断次数,主机(或处理器)能够更专注于执行其他任务,而无需频繁地介入数据传输过程。这有助于减轻主机(或处理器)的负担,以提高国密运算封装系统的整体性能。

18、在一些实施方式中,寄存器模块包括寄存接口单元、第一标识符存储单元、秘钥存储单元、第二标识符存储单元以及参数存储单元。寄存器模块与数据流控制模块之间通过寄存接口单元通信连接。第一标识符存储单元用于存储秘钥信息的秘钥序号,以及秘钥序号对应的秘钥信息的存储地址。秘钥存储单元用于存储多种秘钥信息,一种秘钥信息与至少一个秘钥序号对应设置。第二标识符存储单元用于存储参数信息的参数序号,以及参数序号对应的参数信息的存储地址。以及参数存储单元用于存储多种参数信息,一种参数信息与至少一个参数序号对应设置。

19、有益效果:通过在寄存器模块中配置第一标识符存储单元和第二标识符存储单元,以便于索引和识别特定的秘钥和参数。在便于快速访问和管理秘钥即参数信息的同时,可以避免秘钥存储单元和参数存储单元中信息的直接泄漏,以对算法所需的密钥、参数的进行初步防护。有利于增加整个系统密码业务的安全性、可靠性和保密性。

20、在一些实施方式中,寄存接口单元被配置为:控制秘钥存储单元和参数存储单元仅通过硬件传输的方式通信连接。

21、有益效果:通过对寄存接口单元的配置,以使秘钥存储单元和参数存储单元中的秘钥和参数等数据仅能通过硬件进行读取和写入,不能通过软件模式进行读取。结合上述方案,可以避免秘钥存储单元和参数存储单元中信息的通过软件渠道泄漏,以对算法所需的密钥、参数的进行二级防护。有利于进一步增加整个系统密码业务的安全性、可靠性和保密性。

22、在一些实施方式中,算法模块包括算法接口单元以及多个数据运算单元。算法接口单元与数据流控制模块通信连接,以使数据流控制模块用于调取数据运算单元对第一预设数据进行加密运算或者解密运算。多个数据运算单元至少包括sm2、sm3和sm4算法,用于执行sm4算法的数据运算单元被配置为多线程结构。

23、有益效果:算法模块作为本发明内部模块主要与数据流控制模块进行数据交互。算法接口单元用于适配数据流控制模块的通信握手协议。算法模块集成了多个数据运算单元,多个数据运算单元至少包括国密sm2/sm3/sm4等算法。如一个数据运算单元通过sm2算法(sm2 cryptograohic algorithm,即sm2公钥密码算法)用于实现密钥交换、数据加密、解密、数字签名与验签功能。一个数据运算单元通过sm3算法(security message digestalgorithm,即安全消息摘要算法)能够将任意长度的第一预设数据通过算法运算,生成固定长度的散列值(哈希值),该散列值通常用于验证数据的完整性和真实性。一个数据运算单元通过sm4算法(sm4 block cipher algorithm,即sm4分组密码算法)内部实现多级(如32级)流水线,支持ecb、cbc、cfb、ofb、ctr算法模式,实现不同场景、不同需求的数据加解密业务,具有高安全性和高效率。

24、第二方面,本发明提供了一种国密算法封装系统,包括i/o模块、主控模块、内存模块以及第一方面中的国密算法系统架构。其中,i/o模块、主控模块、内存模块以及国密算法系统架构之间通过系统总线通信连接。

25、有益效果:由于国密算法封装系统包括了第一方面中的国密算法系统架构,使得该国密算法封装系统具备上述国密算法系统架构的所有有益效果,在此不再赘述。

26、在一些实施方式中,主控模块被配置为:

27、将预设数据缓存至内存模块内,并将内存模块中缓存有预设数据的若干个区域的首地址记录为若干个第一内存首地址。预设数据包括第一预设数据、第二预设数据、密钥信息和参数信息。

28、将预设数据的特征信息记录在若干描述符链表内,将描述符链表缓存至内存模块内,并将内存模块中缓存有描述符链表的区域的首地址记录为第二内存首地址。特征信息至少包括预设数据的第一内存首地址、数据类型、数据字节长度和帧类型。

29、主控模块通过第二内存首地址配置直接内存访问模块,以使内存访问模块由内存模块读取并缓存描述符链表,并根据描述符链表解析和获取内存模块中的预设数据。

30、有益效果:即主控模块在内存模块内缓存数据的过程中,通过描述符链表的配置,以使直接内存访问模块能够对内存模块中不连续的数据进行连续的读取。由于在数据传输过程中减少了中断次数,主控模块可以更专注于执行其他任务,而无需频繁地介入数据传输过程。这有助于减轻主控模块的负担,提高系统的整体性能。

- 还没有人留言评论。精彩留言会获得点赞!