基于磁性存储器的内存计算电路的制作方法

[0001]

本发明涉及磁性存储器技术领域,尤其涉及一种基于磁性存储器的内存计算电路。

背景技术:

[0002]

在现有的冯诺依曼体系结构中,处理器与存储器间的存储墙成为影响数据计算的性能瓶颈,而且处理器和存储器之间的数据迁移还会增加功耗。

[0003]

为了提高数据计算速度,有一种做法是:将少量处理单元放在存储器内或存储器附近,实现近内存计算,这样可以对存储器中的原始数据进行预处理,降低了存储器和处理器间的传输带宽需求,可提高性能、降低功耗。

[0004]

但是,在实现本发明的过程中,发明人发现现有技术中至少存在如下技术问题:

[0005]

将处理单元和存储单元集成在同一片芯片上,制造难度大。

技术实现要素:

[0006]

为解决上述问题,本发明提供一种基于磁性存储器的内存计算电路,能够直接在存储器阵列上实现内存计算。

[0007]

本发明提供一种基于磁性存储器的内存计算电路,包括:磁性存储器阵列和多路读取电路,其中,

[0008]

所述磁性存储器阵列包括呈阵列分布的多个存储单元,每一行的多个存储单元共用一条字线,每一列的多个存储单元共用一条源线,每一列或者每一行的多个存储单元共用一对互补位线,每个存储单元包括:一个mos管和两个mtj,所述mos管用于控制两个所述mtj的读写,所述mos管的栅极与对应的字线连接,所述mos管的源极与对应的源线连接,所述mos管的漏极与两个所述mtj连接,两个所述mtj的存储状态相反且两个所述mtj为一组,用于记录一位数据,两个所述mtj分别连接对应的互补位线中的其中一条位线;

[0009]

所述读取电路,用于读取共用一对互补位线的一列或者一行的其中一个或者多个存储单元的状态,以实现按位逻辑操作。

[0010]

可选地,每个存储单元中,所述mtj为基于自旋转移矩写入的mtj,其中一个mtj的参考层与mos管漏极连接,自由层与位线连接;另一个mtj的自由层与mos管漏极连接,参考层与互补位线连接。

[0011]

可选地,每个存储单元中,所述mtj为基于自旋轨道矩写入的mtj,所述磁性存储器阵列的每一行或者每一列共用一条写位线,所述mtj的自由层下方有一条自旋轨道矩提供线,两个所述mtj的自旋轨道矩提供线串连,且其中一个mtj的自旋轨道矩提供线与mos管漏极连接,另一个mtj的自旋轨道矩提供线与写位线连接。

[0012]

可选地,所述读取电路包括:灵敏放大器、反相器和多路选择器,所述灵敏放大器的输入端与一对互补位线连接,所述灵敏放大器的输出端输出一个比较结果信号,所述比较结果信号分为两路,其中一路直接输入所述多路选择器,另一路经所述反相器输入所述

多路选择器,所述多路选择器用于从两路输入信号中选择其中一路进行输出。

[0013]

可选地,所述灵敏放大器为电流型灵敏放大器或者电压型灵敏放大器。

[0014]

可选地,共用一对互补位线的一列或者一行中的三个存储单元用于实现按位“与”、“与非”、“或”和“或非”操作中的一种,其中一个存储单元的mtj存储状态为操作码,另外两个存储单元的mtj存储状态为操作数。

[0015]

可选地,作为操作码的存储单元位于所述磁性存储器阵列的第一行或者第一列,作为操作数的存储单元位于所述磁性存储器阵列的不同于所述作为操作码的存储单元的任意两行或者任意两列。

[0016]

本发明的基于磁性存储器的内存计算电路,包括一磁性存储器阵列和多路读取电路,通过读取操作能够直接在存储器阵列上实现内存计算,克服了存储器和处理器制造整合的难题,而且,本发明的内存计算电路,计算速度与存储器的读操作在同一个数量级,计算速度快。计算操作是非破坏性的,对存储数据无影响,计算结果可以直接本地保存在非易失的mram阵列中。

附图说明

[0017]

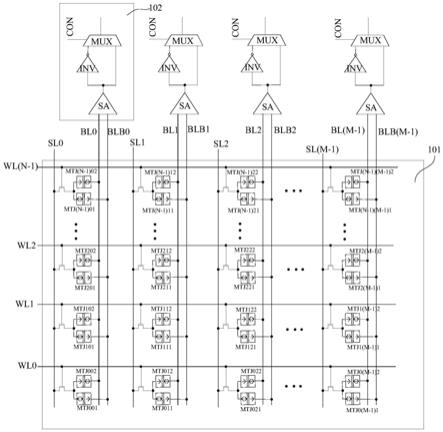

图1为本发明一实施例的基于磁性存储器的内存计算电路的结构示意图;

[0018]

图2为本发明另一实施例的基于磁性存储器的内存计算电路的结构示意图;

[0019]

图3为本发明又一实施例的基于磁性存储器的内存计算电路的结构示意图;

[0020]

图4为本发明又一实施例的基于磁性存储器的内存计算电路的结构示意图。

具体实施方式

[0021]

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0022]

本发明一实施例提供一种基于磁性存储器的内存计算电路,如图1所示,包括:磁性存储器阵列101和多路读取电路102,其中,

[0023]

所述磁性存储器阵列101包括呈阵列分布的多个存储单元,本实施例中,存储器阵列101包括n行m列的多个存储单元,每一行的多个存储单元共用一条字线wl,分别记为wl0~wl(n-1),每一列的多个存储单元共用一条源线sl,分别记为sl0~sl(m-1),每一列的多个存储单元共用一对互补位线bl和blb,分别记为bl0~bl(m-1)和blb0~blb(m-1),每个存储单元包括:一个mos管和两个mtj,所述mos管用于控制两个所述mtj的读写,所述mos管的栅极与所在行的字线连接,所述mos管的源极与所在列的源线连接,所述mos管的漏极与两个所述mtj连接,两个所述mtj的存储状态相反且两个所述mtj为一组,用于记录一位数据,两个所述mtj分别连接所在列的互补位线中的其中一条位线;

[0024]

所述读取电路102,用于读取共用一对互补位线的一列的其中一个或者多个存储单元的状态,以实现按位逻辑操作。

[0025]

可选地,本实施例中,如图1所示,mtj为基于自旋转移矩(spin transfer torque,stt)写入的mtj,每个存储单元的两个mtj为并联关系,具体的,其中一个mtj的参考层与mos

管漏极连接,自由层与位线bl连接;另一个mtj的自由层与mos管漏极连接,参考层与互补位线blb连接。读取电路102包括:灵敏放大器sa、反相器inv和多路选择器mux,所述灵敏放大器sa的输入端与一对互补位线连接,所述灵敏放大器sa的输出端输出一个比较结果信号,所述比较结果信号分为两路,其中一路直接输入所述多路选择器mux,另一路经所述反相器inv输入所述多路选择器mux,所述多路选择器mux用于从两路输入信号中选择其中一路进行输出。所述灵敏放大器sa可以采用电流型灵敏放大器,也可以采用电压型灵敏放大器,如果采用电流型sa,对读操作的存储单元施加相同的电压,比较sa输入的两个电流;如果采用电压型sa,对读操作的存储单元施加相同的电流,比较sa输入的两个电压。本实施例中,灵敏放大器sa为电流型灵敏放大器。

[0026]

本发明实施例的基于磁性存储器的内存计算电路,通过读取操作即可实现按位逻辑计算,计算速度快,计算操作是非破坏性的,对存储数据无影响,而且,计算结果可以直接保存在非易失的stt-mram中。sa的读取过程即为按位逻辑操作过程,可实现的逻辑操作包括“与”、“与非”、“或”、“或非”、“非”和“异或”。同时,每个存储单元中的两个mtj可同时读写,降低功耗,提高了数据存储和逻辑计算的速度,由于两个mtj要求状态相反,同时写入数据还提高了数据的可靠性。

[0027]

基于图1,先对磁性存储器阵列的存储单元进行写操作,以连接于字线wl0和源线sl0的存储单元为例,对存储单元执行写操作时,wl0接入高电平使mos管导通,sl0接地,bl0接入写电压va,blb0接入写电压vb,或者,bl0接入写电压-va,blb0接入写电压-vb,写入操作后,mtj001和mtj002的存储状态相反。

[0028]

将每个存储单元的连接至位线blb的mtj记为第一mtj,将每个存储单元的连接至bl的mtj记为第二mtj,存储阵列中mtj的标号可以按如下规则:i行j列(0≤i≤n-1,0≤j≤m-1)的存储单元中的两个mtj记为mtj(ij1)和mtj(ij2)。每个存储单元的数据以(第一mtj的状态,第二mtj的状态)来表示,并且,将(p,ap)记为存储单元的数据为0,将(ap,p)记为存储单元的数据为1。例如,包括mtj001和mtj002的存储单元,mtj001和mtj002状态为(p,ap)时,存储单元的数据为0;mtj001和mtj002状态为(ap,p)时,存储单元的数据为1。

[0029]

实现“与”、“与非”、“或”、“或非”的逻辑操作时,需要同时读取共用一对互补位线的一列中的三个存储单元的数据,其中一个存储单元的mtj的存储状态为操作码,能够决定按位逻辑操作的类型,另外两个存储单元的mtj的存储状态为操作数。一般的,为了设计简单,作为操作码的存储单元位置是固定的,一般取共用一对互补位线的一列的位于第一行的存储单元,作为操作数的存储单元位置是任意的,可以是共用一对互补位线的一列的其他任意两行的存储单元。

[0030]

以与sl0和wl0、wl1和wl2相连的三个存储单元为例,详细介绍各逻辑操作的工作原理。三个存储单元中,每个存储单元都包括两个mtj,两个mtj为一组,记录一位(1bit)数据。与wl0相连的存储单元的两个mtj(mtj001、mtj002)的存储状态作为操作码,决定按位逻辑操作的类型,与wl1相连的存储单元的两个mtj(mtj101、mtj102)以及与wl2相连的存储单元的两个mtj(mtj201、mtj202)的存储状态作为操作数。

[0031]

1、“与”操作

[0032]

表示操作码的存储单元的数据为0,即mtj001、mtj002状态为(p,ap),且多路选择器mux的控制信号con选择输出sa的输出信号时,mux的输出结果为两个操作数的“与”操作。

[0033]

具体分析如下:

[0034]

表示操作数的存储单元的数据为00时,即mtj101、mtj102状态为(p,ap),mtj201、mtj202状态为(p,ap),blb连接的三个mtj状态均为p,bl连接的三个mtj状态均为ap,因此,sa同时读取三个存储单元的数据,blb上的电流要大于bl上的电流,sa输出0,mux输出0;

[0035]

表示操作数的存储单元的数据为01时,即mtj101、mtj102状态为(p,ap),mtj201、mtj202状态为(ap,p),blb连接的三个mtj,两个为p,一个为ap,bl连接的三个mtj,两个为ap,一个为p,因此,sa同时读取三个存储单元的数据,blb上的电流要大于bl上的电流,sa输出0,mux输出0;

[0036]

表示操作数的存储单元的数据为10时,即mtj101、mtj102状态为(ap,p),mtj201、mtj202状态为(p,ap),blb连接的三个mtj,两个为p,一个为ap,bl连接的三个mtj,两个为ap,一个为p,因此,sa同时读取三个存储单元的数据,blb上的电流要大于bl上的电流,sa输出0,mux输出0;

[0037]

表示操作数的存储单元的数据为11时,即mtj101、mtj102状态为(ap,p),mtj201、mtj202状态为(ap,p),blb连接的三个mtj,两个为ap,一个为p,bl连接的三个mtj,两个为p,一个为ap,因此,sa同时读取三个存储单元的数据,blb上的电流要小于bl上的电流,sa输出1,mux输出1。

[0038]

综上所述,“与”操作的真值表如表1所示:

[0039]

表1

[0040][0041]

2、“与非”操作

[0042]

表示操作码的存储单元的数据为0,即mtj001、mtj002状态为(p,ap),且多路选择器mux的控制信号con选择输出反相器inv的输出信号时,mux的输出结果为两个操作数的“与非”操作。

[0043]

具体分析如下:

[0044]

表示操作数的存储单元的数据为00时,即mtj101、mtj102状态为(p,ap),mtj201、mtj202状态为(p,ap),blb连接的三个mtj状态均为p,bl连接的三个mtj状态均为ap,因此,sa同时读取三个存储单元的数据,blb上的电流要大于bl上的电流,sa输出0,mux输出1;

[0045]

表示操作数的存储单元的数据为01时,即mtj101、mtj102状态为(p,ap),mtj201、mtj202状态为(ap,p),blb连接的三个mtj,两个为p,一个为ap,bl连接的三个mtj,两个为ap,一个为p,因此,sa同时读取三个存储单元的数据,blb上的电流要大于bl上的电流,sa输出0,mux输出1;

[0046]

表示操作数的存储单元的数据为10时,即mtj101、mtj102状态为(ap,p),mtj201、mtj202状态为(p,ap),blb连接的三个mtj,两个为p,一个为ap,bl连接的三个mtj,两个为ap,一个为p,因此,sa同时读取三个存储单元的数据,blb上的电流要大于bl上的电流,sa输出0,mux输出1;

[0047]

表示操作数的存储单元的数据为11时,即mtj101、mtj102状态为(ap,p),mtj201、mtj202状态为(ap,p),blb连接的三个mtj,两个为ap,一个为p,bl连接的三个mtj,两个为p,一个为ap,因此,sa同时读取三个存储单元的数据,blb上的电流要小于bl上的电流,sa输出1,mux输出0。

[0048]

综上所述,“与非”操作的真值表如表2所示:

[0049]

表2

[0050][0051]

3、“或”操作

[0052]

表示操作码的存储单元的数据为1,即mtj001、mtj002状态为(ap,p),且多路选择器mux的控制信号con选择输出sa的输出信号时,mux的输出结果为两个操作数的“或”操作。

[0053]

具体分析如下:

[0054]

表示操作数的存储单元的数据为00时,即mtj101、mtj102状态为(p,ap),mtj201、mtj202状态为(p,ap),blb连接的三个mtj,两个为p,一个为ap,bl连接的三个mtj,两个为ap,一个为p,因此,sa同时读取三个存储单元的数据,blb上的电流要大于bl上的电流,sa输出0,mux输出0;

[0055]

表示操作数的存储单元的数据为01时,即mtj101、mtj102状态为(p,ap),mtj201、mtj202状态为(ap,p),blb连接的三个mtj,两个为ap,一个为p,bl连接的三个mtj,两个为p,一个为ap,因此,sa同时读取三个存储单元的数据,blb上的电流要小于bl上的电流,sa输出1,mux输出1;

[0056]

表示操作数的存储单元的数据为10时,即mtj101、mtj102状态为(ap,p),mtj201、mtj202状态为(p,ap),blb连接的三个mtj,两个为ap,一个为p,bl连接的三个mtj,两个为p,一个为ap,因此,sa同时读取三个存储单元的数据,blb上的电流要小于bl上的电流,sa输出1,mux输出1;

[0057]

表示操作数的存储单元的数据为11时,即mtj101、mtj102状态为(ap,p),mtj201、mtj202状态为(ap,p),blb连接的三个mtj状态均为ap,bl连接的三个mtj状态均为p,因此,sa同时读取三个存储单元的数据,blb上的电流要小于bl上的电流,sa输出1,mux输出1。

[0058]

综上所述,“或”操作的真值表如表3所示:

[0059]

表3

[0060][0061]

4、“或非”操作

[0062]

表示操作码的存储单元的数据为1,即mtj001、mtj002状态为(ap,p),且多路选择器mux的控制信号con选择输出反相器inv的输出信号时,mux的输出结果为两个操作数的“或非”操作。

[0063]

具体分析如下:

[0064]

表示操作数的存储单元的数据为00时,即mtj101、mtj102状态为(p,ap),mtj201、mtj202状态为(p,ap),blb连接的三个mtj,两个为p,一个为ap,bl连接的三个mtj,两个为ap,一个为p,因此,sa同时读取三个存储单元的数据,blb上的电流要大于bl上的电流,sa输出0,mux输出1;

[0065]

表示操作数的存储单元的数据为01时,即mtj101、mtj102状态为(p,ap),mtj201、mtj202状态为(ap,p),blb连接的三个mtj,两个为ap,一个为p,bl连接的三个mtj,两个为p,一个为ap,因此,sa同时读取三个存储单元的数据,blb上的电流要小于bl上的电流,sa输出1,mux输出0;

[0066]

表示操作数的存储单元的数据为10时,即mtj101、mtj102状态为(ap,p),mtj201、mtj202状态为(p,ap),blb连接的三个mtj,两个为ap,一个为p,bl连接的三个mtj,两个为p,一个为ap,因此,sa同时读取三个存储单元的数据,blb上的电流要小于bl上的电流,sa输出1,mux输出0;

[0067]

表示操作数的存储单元的数据为11时,即mtj101、mtj102状态为(ap,p),mtj201、mtj202状态为(ap,p),blb连接的三个mtj状态均为ap,bl连接的三个mtj状态均为p,因此,sa同时读取三个存储单元的数据,blb上的电流要小于bl上的电流,sa输出1,mux输出0。

[0068]

综上所述,“或非”操作的真值表如表4所示:

[0069]

表4

[0070][0071][0072]

5、“异或”操作

[0073]“异或”操作是对两个操作数的“与”操作的结果以及“或非”操作的结果,二者再进行“或非”操作得到。

[0074]

6、“非”操作

[0075]

对一个存储单元执行读操作时,wl0接入高电平使mos管导通,sl0接入读电压vr,bl0和blb0接地,且多路选择器mux的控制信号con选择输出sa的输出信号时,mux的输出结果为正常读出的mtj001和mtj002的数据;如果多路选择器mux的控制信号con选择输出反相器inv的输出信号时,mux的输出结果相当于执行了“非”操作。

[0076]

本发明另一实施例提供一种基于磁性存储器的内存计算电路,如图2所示,包括:磁性存储器阵列201和多路读取电路202,其中,

[0077]

所述磁性存储器阵列201包括呈阵列分布的多个存储单元,本实施例中,存储器阵列201包括n行m列的多个存储单元,每一行的多个存储单元共用一条字线wl,分别记为wl0~wl(n-1),每一列的多个存储单元共用一条源线sl,分别记为sl0~sl(m-1),每一列的多个存储单元共用一对互补位线bl和blb,分别记为bl0~bl(m-1)和blb0~blb(m-1),每个存储单元包括:一个mos管和两个mtj,所述mos管用于控制两个所述mtj的读写,所述mos管的栅极与所在行的字线连接,所述mos管的源极与所在列的源线连接,所述mos管的漏极与两个所述mtj连接,两个所述mtj的存储状态相反且两个所述mtj为一组,用于记录一位数据,两个所述mtj分别连接所在列的互补位线中的其中一条位线;

[0078]

所述读取电路202,用于读取共用一对互补位线的一列的其中一个或者多个存储单元的状态,以实现按位逻辑操作。

[0079]

可选地,本实施例中,如图2所示,mtj为基于自旋轨道矩(spin orbit torque,sot)写入的mtj,磁性存储器阵列中每一行的多个存储单元共用一条写位线blw,记为blw0~blw(n-1),具体地,所述mtj的自由层下方有一条自旋轨道矩提供线,两个所述mtj的自旋轨道矩提供线串连,且其中一个mtj的自旋轨道矩提供线与mos管漏极连接,另一个mtj的自旋轨道矩提供线与写位线连接。读取电路202的结构和图1所示实施例相同,和图1所示实施例相比,区别只在于mtj的读写原理略有不同,但是关于逻辑操作的原理是一样的,关于“与”、“与非”、“或”、“或非”、“异或”和“非”的逻辑操作不再展开叙述。

[0080]

本发明实施例的基于磁性存储器的内存计算电路,通过读取操作即可实现按位逻辑计算,计算速度快,计算操作是非破坏性的,对存储数据无影响,而且,计算结果可以直接保存在非易失的sot-mram中。sa的读取过程即为按位逻辑操作过程,可实现的逻辑操作包括“与”、“与非”、“或”、“或非”、“非”和“异或”。同时,每个存储单元中的两个mtj可同时读写,降低功耗,提高了数据存储和逻辑计算的速度,由于两个mtj要求状态相反,同时写入数据还提高了数据的可靠性。

[0081]

另外,需要说明的是,磁性存储器阵列还存在另一种情况,每一行的多个存储单元共用一对互补位线,通过读取电路读取共用一对互补位线的一行的其中一个或者多个存储单元的状态,以实现按位逻辑操作。图3示出了存储单元中的mtj为基于自旋转移矩stt写入的mtj,且每一行的多个存储单元共用一对互补位线的情形,图4示出了存储单元中的mtj为基于自旋轨道矩sot写入的mtj,且每一行的多个存储单元共用一对互补位线的情形。两种情形下,逻辑操作的原理相同,只是将逻辑操作的对象从一列中的一个或者三个存储单元变成了一行中的一个或者三个存储单元,逻辑操作的原理及真值表可以参考前述的实施例,在此不再赘述。

[0082]

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1