降低浅沟槽隔离的高度差的制作方法与流程

1.本发明涉及一种降低浅沟槽隔离的高度差的方法,特别是涉及降低核心电路区和周边电路区内浅沟槽隔离所造成的高度差的方法。

背景技术:

2.元件隔离区是用以防止载流子通过基底而在相邻的元件间移动之用。典型的元件隔离区是形成于稠密的半导体电路,比如是动态随机存取存储器中相邻的场效晶体管之间,用于减少由场效晶体管产生的漏电流现象。从前的元件隔离区的方法是采用局部区域氧化技术。由于局部区域氧化技术的日趋成熟,因此可由此技术,以较低的成本获得信赖度高且有效的元件隔离结构。然而,采用局部区域氧化的方式具有应力产生的问题与场隔离结构周围鸟嘴区的形成等缺点。其中,特别是鸟嘴区的形成,使得在小型的元件上的场隔离结构并不能做有效地隔离,所以在目前高密度元件中,必须以较易于调整大小的浅沟槽隔离方式所形成的元件隔离结构来取代。

3.然而在半导体制作工艺中会发生浅沟槽隔离的上表面和基底之间有高度差或是在不同区域内的浅沟槽隔离之间具有高度差,此高度差将会造成后续元件制作上的误差。

技术实现要素:

4.有鉴于此,本发明提供一种降低浅沟槽隔离的高度差的方法,以避免半导体元件受到高度差的影响导致制作工艺误差。

5.根据本发明的一优选实施例,一种降低浅沟槽隔离的高度差的方法包含提供一基底,基底包含一核心电路区和一周边电路区,周边电路区包含一p型晶体管区和一n型晶体管区,一垫氧化硅层覆盖基底,然后形成一第一浅沟槽隔离、一第二浅沟槽隔离和一第三浅沟槽隔离分别位于周边电路区的n型晶体管区、核心电路区和周边电路区的p型晶体管区,其中第一浅沟槽隔离、第二浅沟槽隔离和第三浅沟槽隔离埋入于垫氧化硅层和基底中,第一浅沟槽隔离的上表面凸出于基底的上表面一高度的距离、第二浅沟槽隔离的上表面凸出于基底的上表面前述高度的距离、第三浅沟槽隔离的上表面凸出于基底的上表面前述高度的距离,然后形成一第一掩模覆盖核心电路区和n型晶体管区并且曝露出第三浅沟槽隔离以及在周边电路区内的p型晶体管区,之后以第一掩模为掩模,在曝露的p型晶体管区注入n型掺质以形成一n型阱区并且以第一掩模为掩模移除部分第三浅沟槽隔离使得部分的第三浅沟槽隔离凸出于基底的上表面的距离小于前述高度,接续移除第一掩模,然后形成一第二掩模覆盖核心电路区和p型晶体管区并且曝露出第一浅沟槽隔离以及周边电路区内的n型晶体管区,接着以第二掩模为掩模,在周边电路区内的n型晶体管区注入p型掺质以形成一p型阱区并且以第二掩模为掩模移除部分的第一浅沟槽隔离使得部分的第一浅沟槽隔离凸出于基底的上表面的距离小于前述高度,然后移除第二掩模接续形成一第一氧化硅层取代垫氧化硅层,之后形成第一氧化硅层后,形成一第三掩模覆盖周边电路区并且曝露出第二浅沟槽隔离与位于核心电路区内的第一氧化硅层,接着以第三掩模为掩模移除部分的第

二浅沟槽隔离并且完全移除核心电路区内的第一氧化硅层,其中移除部分的第二浅沟槽隔离后使得部分第二浅沟槽隔离凸出于基底的上表面的距离小于前述高度,最后移除第三掩模。

6.为让本发明的上述目的、特征及优点能更明显易懂,下文特举优选实施方式,并配合所附的附图,作详细说明如下。然而如下的优选实施方式与附图仅供参考与说明用,并非用来对本发明加以限制者。

附图说明

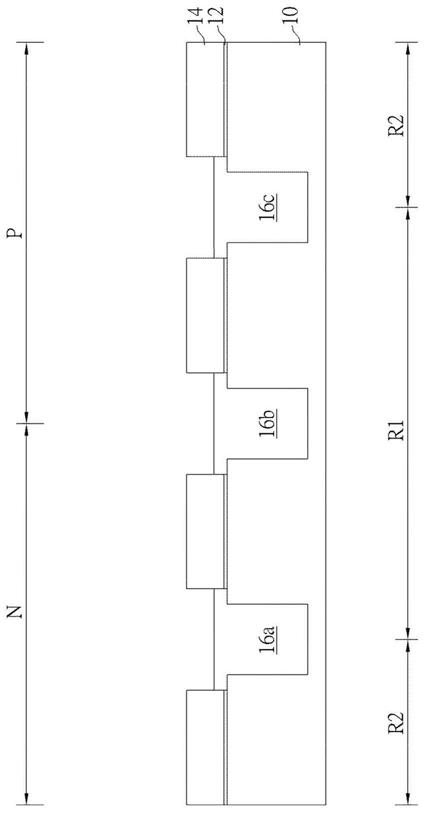

7.图1至图10为本发明的一优选实施例所绘示的一种降低浅沟槽隔离的高度差的方法的示意图;

8.图11为本发明的一示范例所绘示的半导体结构的制作方法的示意图。

9.主要元件符号说明

10.10:基底

11.12:垫氧化硅层

12.14:垫氮化硅层

13.16a:第一浅沟槽隔离

14.16b:第二浅沟槽隔离

15.16c:第三浅沟槽隔离

16.18:掺杂阱区

17.20:第一掩模

18.22:n型阱区

19.24:第二掩模

20.26:p型阱区

21.28:第一氧化硅层

22.30:第三掩模

23.32:第二氧化硅层

24.34:第一栅极

25.36:第二栅极

26.38:源极/漏极掺杂区

27.40:蚀刻停止层

28.42:介电层

29.44:金属栅极

30.100:半导体结构

31.n:n型晶体管区

32.p:p型晶体管区

33.r1:核心电路区

34.r2:周边电路区

具体实施方式

35.图1至图10为根据本发明的一优选实施例所绘示的一种降低浅沟槽隔离的高度差的方法。如图1所示,首先提供一基底10,基底10可以为硅基底、一锗基底、一砷化镓基底、一硅锗基底、一磷化铟基底、一氮化镓基底、一碳化硅基底或是一硅覆绝缘基底,基底10包含一核心电路区r1和一周边电路区r2,周边电路区r2包含一p型晶体管区p和一n型晶体管区n,核心电路区r1也包含p型晶体管区p和n型晶体管区n,然后依序形成一垫氧化硅层12和一垫氮化硅层14覆盖基底10,接着图案化垫氧化硅层12和垫氮化硅层14以在垫氧化硅层12和垫氮化硅层14上形成数个浅沟槽隔离的预定位置,接着以图案化后的垫氧化硅层12和垫氮化硅层14作为掩模,蚀刻基底10以在基底10中形成多个沟槽,之后在沟槽内填入氧化硅层作为浅沟槽隔离。详细来说,多个浅沟槽隔离可以包含一第一浅沟槽隔离16a、一第二浅沟槽隔离16b和一第三浅沟槽隔离16c都埋入于垫氮化硅层14、垫氧化硅层12和基底10中,详细来说第一浅沟槽隔离16a部分位周边电路区r2,部分位于核心电路区r1内并且第一浅沟槽隔离16a完全都在n型晶体管区n的范围内,而第二浅沟槽隔离16b完全位于核心电路区r1内并且部分在n型晶体管区n内部分在p型晶体管区p内,第三浅沟槽隔离16c部分位于周边电路区r2部分位于核心电路区r1内并且第三浅沟槽隔离16c全部都在p型晶体管区p的范围内。

36.然而根据不同的产品设计同一个浅沟槽隔离不一定要同时位于周边电路区r2和核心电路区r1,也可以同一个浅沟槽隔离完全都在周边电路区r2或核心电路区r1,浅沟槽隔离所在的位置可视不同需要而改变,只要在周边电路区r2的p型晶体管区p、周边电路区的n型晶体管区n和核心电路区r1都有浅沟槽隔离时即可使用本发明提供的方法。

37.接续回蚀刻第一浅沟槽隔离16a、第二浅沟槽隔离16b和第三浅沟槽隔离16c使得第一浅沟槽隔离16a、第二浅沟槽隔离16b和第三浅沟槽隔离16c的上表面略低于垫氮化硅层14的上表面但高于垫氧化硅层12的上表面。

38.如图2所示,移除垫氮化硅层14并且保留垫氧化硅层12,此时第一浅沟槽隔离16a的上表面凸出于基底10的上表面一高度h的距离、第二浅沟槽隔离16b的上表面凸出于基底10的上表面高度h的距离、第三浅沟槽隔离16c的上表面凸出于基底10的上表面高度h的距离。之后,在核心电路区r1内的基底10中形成掺杂阱区18。根据本发明的优选实施例,高度h介于100至600埃之间。

39.如图3所示,形成一第一掩模20覆盖全部的核心电路区r1和n型晶体管区n并且曝露出至少部分的第三浅沟槽隔离16c以及p型晶体管区p,详细来说是曝露出在周边电路区r2内的第三浅沟槽隔离16c和周边电路区r2内的p型晶体管区p,然后以第一掩模20为掩模在p型晶体管区p的基底10中注入n型掺质以形成一n型阱区22。在n型阱区22完成之后,以第一掩模20为掩模移除曝露出的第三浅沟槽隔离16c使得在周边电路区r2内的第三浅沟槽隔离16c凸出于基底10的上表面的距离小于高度h(高度的位置请参阅图2),移除第三浅沟槽隔离16c的方式较佳使用干蚀刻,由于第三浅沟槽隔离16c的氧化硅和垫氧化层12的氧化硅的致密度不同,因此可以在保留垫氧化层12的情况下部分移除第三浅沟槽隔离16c。此时在周边电路区r2内的第三浅沟槽隔离16c凸出于基底10的上表面的距离较佳介于50至500埃之间。根据本发明的优选实施例,在周边电路区r2内的第三浅沟槽隔离16c的上表面和垫氧化硅层12的上表面切齐。

40.如图4所示,移除第一掩模20后形成一第二掩模24覆盖全部的核心电路区r1和全部的p型晶体管区p并且曝露出在周边电路区内r2的第一浅沟槽隔离16a以及在周边电路区r2内n型晶体管区n,然后以第二掩模24为掩模,在曝露的n型晶体管区n的基底10中注入p型掺质以形成一p型阱区26。接着在形成p型阱区26之后,以第二掩模24为掩模移除至少部分第一浅沟槽隔离16a使得在周边电路区r2内的第一浅沟槽隔离16a凸出于基底10的上表面的距离小于高度h(高度的位置请参阅图2),移除第一浅沟槽隔离16a的方式较佳使用干蚀刻,此时在周边电路区r2内的第一浅沟槽隔离16a凸出于基底10的上表面的距离较佳介于50至500埃之间。根据本发明的优选实施例,此时在周边电路区r2内的第一浅沟槽隔离16a的上表面和垫氧化硅层12的上表面切齐。

41.值得注意的是:图3和图4中的制作工艺顺序可以对调,也就是说可以先进行图4中的制作工艺步骤包含形成p型阱区26后移除部分在周边电路区r2内的第一浅沟槽隔离16a,之后再进行图3中的制作工艺步骤包含形成n型阱区22后移除部分在周边电路区r2内的第三浅沟槽隔离16c。

42.本发明利用在周边电路区r2内形成p型阱区26或n型阱区22的掩模,去除周边电路区r2内部分的浅沟槽隔离,使得在周边电路区r2内的浅沟槽隔离的高度降低,如此将缩小后续基底10和在周边电路区r2内的浅沟槽隔离之间的高度差。因为形成p型阱区26和移除在周边电路区r2内并且在n型晶体管区n中的浅沟槽隔离16a是使用同一掩模,因此不需再额外制作光掩模专门用来移除浅沟槽隔离16a。同样地,因为形成n型阱区22和移除在周边电路区r2内并且在p型晶体管区p中的浅沟槽隔离16c是使用同一掩模,因此不需再额外制作光掩模专门用来移除浅沟槽隔离16c,如此不仅能减少制作工艺步骤,还可以减少光掩模数量。

43.接着如图5所示,移除第二掩模24之后完全去除垫氧化硅层12,垫氧化硅层12的去除方式较佳使用湿蚀刻或是其它可以移除氧化硅的方式。如图6所示,形成一第一氧化硅层28取代原本垫氧化硅层12的位置,此时第一氧化硅层28的厚度较佳介于10至100埃之间。根据本发明的一较佳实施例,在周边电路区r2的第一浅沟槽隔离16a的上表面和第一氧化硅层28的上表面切齐,在周边电路区r2的第三浅沟槽隔离16c的上表面和第一氧化硅层的28上表面切齐。第一氧化硅层28较佳使用加热氧化基底10表面的方式形成。

44.如图7所示,形成一第三掩模30覆盖全部的周边电路区r2并且曝露核心电路区r1,详细来说,在核心电路区r1内的第一浅沟槽隔离16a、第二浅沟槽隔离16b、在核心电路区r2内第三浅沟槽隔离16c与位于核心电路区r1内的第一氧化硅层28都由第三掩模30曝露出来。然后完全移除曝露的第一氧化硅层28并且同时移除部分在核心电路区r1内的第一浅沟槽隔离16a、部分的第二浅沟槽隔离16b以及部分在核心电路区r1内的第三浅沟槽隔离16c,使得在核心电路区r1内的第一浅沟槽隔离16a凸出于基底10的上表面的距离小于高度h(高度h的位置请参阅图2),第二浅沟槽隔离16b凸出于基底10的上表面的距离小于高度h并且核心电路区r1内的第三浅沟槽隔离16c凸出于基底10的上表面的距离小于高度h,根据本发明的较佳实施例,在移除步骤完成后,在核心电路区r1内的第一浅沟槽隔离16a的上表面和基底10的上表面之间的距离介于0至50埃之间、第二浅沟槽隔离16b的上表面和基底10的上表面之间的距离介于0至50埃之间以及在核心电路区r1内的第三浅沟槽隔离16c的上表面和基底10的上表面之间的距离介于0至50埃之间。

45.如图8所示,移除第三掩模30后,形成一第二氧化硅层32于核心电路区r1取代原来第一氧化硅层28的位置,第二氧化硅层32的厚度较佳介于5至100埃之间。根据本发明的优选实施例,此时第一浅沟槽隔离16a的上表面、第二浅沟槽隔离16b的上表面、第三浅沟槽隔离16c的上表面、第二氧化硅层32的上表面和第一氧化硅层28的上表面切齐。

46.如图9所示形成多个第一栅极34分别设置在第一浅沟槽隔离16a、第三浅沟槽隔离16c和基底10的核心电路区r1上以及形成多个第二栅极36分别位于p型阱区26上和n型阱区22上,第一栅极34和第二栅极36的形成方式包含形成一多晶硅层全面覆盖基底10,之后图案化多晶硅层形成第一栅极34和第二栅极36。

47.接着形成多个源极/漏极掺杂区38各自位于各个第一栅极34和各个第二栅极36两侧的基底10中,在p型晶体管区p的源极/漏极掺杂区38具有p型导电型态,在n型晶体管区n的源极/漏极掺杂区38具有n型导电型态。之后形成一蚀刻停止层40和一介电层42覆盖基底10、第一栅极34和第二栅极36。

48.如图10所示,移除覆盖第一栅极34的蚀刻停止层40和介电层42曝露出第一栅极34和第二栅极36,然后移除所有的第一栅极34和第二栅极36,之后形成多个金属栅极44分别取代被移除的第一栅极34和第二栅极36的位置,金属栅极44较佳包含一金属层和一缓冲层,至此本发明的一半导体结构100业已完成。在第一浅沟槽隔离16a和第三浅沟槽隔离16c上的金属栅极44是作为虚置栅极。

49.值得注意的是:在图8的步骤完成后,由于第一浅沟槽隔离16a的上表面、第三浅沟槽隔离16c的上表面、第一氧化硅层28和第二氧化硅层32的上表面切齐或是相差在一定的范围内,所以第一栅极34和第二栅极36的上表面大致切齐,因此可以将所有第一栅极34和所有的第二栅极36在同一步骤中都完全移除。

50.图11为根据本发明的一示范例所绘示的半导体结构的制作方法,其中具有相同功能的元件将使用图10中的标号。如图11所示,若是没有进行图3和图4中第一浅沟槽隔离16a和第三浅沟槽隔离16c的移除步骤时,就会造成在周边电路区域r2内第一浅沟槽隔离16a以及第三浅沟槽隔离16c上的第一栅极34的上表面比核心电路区r1的第一栅极34的上表面以及在周边电路区域r2的第二栅极36的上表面高出许多,因此在移除第一栅极34和第二栅极36时,上表面较低的第一栅极34和第二栅极36只能被部分移除。

51.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1