主动元件基板的制作方法

1.本发明涉及一种主动元件基板。

背景技术:

2.一般而言,电子装置中都包含有许多的半导体元件。举例来说,显示装置中常包含有许多薄膜晶体管,这些薄膜晶体管利用在基板上沉积各种不同的薄膜(例如半导体、金属、介电层等)来形成。在显示装置中,薄膜晶体管可以设置于像素结构中,也可设置于驱动电路中。

3.随着科技的进步,各种制作工艺技术的临界尺寸(critical size)逐渐缩小。为了制作出更小的薄膜晶体管,薄膜晶体管的不同电极之间的距离也逐渐缩小,这增加了不同电极之间的电场对薄膜晶体管的品质产生的负面影响。

技术实现要素:

4.本发明提供一种主动(有源)元件基板,能改善主动元件出现热载流子效应的问题。

5.本发明的至少一实施例提供一种主动元件基板。主动元件基板包括基板、第一半导体层、栅极绝缘层、第一栅极、第一源极、第一漏极以及遮蔽电极。第一半导体层位于基板上,且包括依序连接的第一重掺杂区、第一轻掺杂区、沟道区、第二轻掺杂区以及第二重掺杂区。栅极绝缘层位于第一半导体层上。第一栅极位于栅极绝缘层上,且在基板的一法线方向上重叠于第一半导体层的沟道区。第一源极电连接至第一半导体层的第一重掺杂区。第一漏极电连接至第一半导体层的第二重掺杂区。第一主动元件包括第一半导体层、第一栅极、第一源极以及第一漏极。遮蔽电极在基板的法线方向上重叠于第一半导体层的第二轻掺杂区,其中遮蔽电极为浮置电极。

6.本发明的至少一实施例提供一种主动元件基板。主动元件基板包括基板、半导体图案、栅极绝缘层、第一导电层、第一介电层、遮蔽电极、第二介电层以及第二导电层。半导体图案位于基板上,且包括第一半导体层。第一半导体层包括依序连接的第一重掺杂区、第一轻掺杂区、沟道区、第二轻掺杂区以及第二重掺杂区。栅极绝缘层形成于半导体图案上。第一导电层形成于栅极绝缘层上,且包括第一栅极。第一栅极在基板的法线方向上重叠于第一半导体层的沟道区。第一介电层形成于第一导电层以及栅极绝缘层上。遮蔽电极形成于第一介电层上,且在基板的法线方向上重叠于第一半导体层的第二轻掺杂区。第二介电层形成于第一介电层以及遮蔽电极上。第二导电层形成于第二介电层上,且包括第一源极以及第一漏极。第一源极电连接至第一半导体层的第一重掺杂区。第一漏极电连接至第一半导体层的第二重掺杂区。

7.基于上述,通过遮蔽电极的设置,第二重掺杂区与第一栅极之间的电场可以被遮蔽电极分散,由此能改善主动元件出现热载流子效应的问题。

附图说明

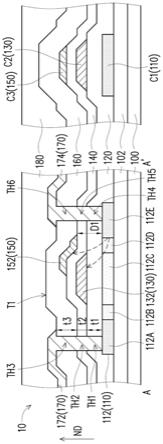

8.图1a是本发明的一实施例的一种主动元件基板的上视示意图;

9.图1b是图1a的线a-a’的剖面示意图;

10.图2a是本发明的一实施例的一种主动元件基板的上视示意图;

11.图2b是图2a的线b-b’的剖面示意图;

12.图2c是图2a的线c-c’的剖面示意图;

13.图3a是本发明的一实施例的一种主动元件基板的上视示意图;

14.图3b是图3a的线d-d’的剖面示意图;

15.图4a是本发明的一实施例的一种主动元件基板的上视示意图;

16.图4b是图4a的线e-e’的剖面示意图;

17.图5a是本发明的一实施例的一种主动元件基板的上视示意图;

18.图5b是图5a的线f-f’的剖面示意图;

19.图6a是本发明的一实施例的一种主动元件基板的上视示意图;

20.图6b是图6a的线g-g’的剖面示意图;

21.图7a是本发明的一实施例的一种主动元件基板的上视示意图;

22.图7b是图7a的线h-h’的剖面示意图;

23.图8a是本发明的一实施例的一种主动元件基板的上视示意图;

24.图8b是图8a的线i-i’的剖面示意图。

25.符号说明

26.10、20、30、40、50、60、70、80:主动(有源)元件基板

27.100:基板

28.102:缓冲层

29.110:半导体图案

30.112、114:第一半导体层

31.112a、114a:第一重掺杂区

32.112b、114b:第一轻掺杂区

33.112c、114c:沟道区

34.112d、114d:第二轻掺杂区

35.112e、114e:第二重掺杂区

36.120:栅极绝缘层

37.130:第一导电层

38.132:第一栅极

39.134:第二栅极

40.140:第一介电层

41.150:辅助导电层

42.152、173:遮蔽电极

43.160:第二介电层

44.170:第二导电层

45.172:第一源极

46.172e:延伸部

47.174:第一漏极

48.176:第二源极

49.178:第二漏极

50.180:钝化层

51.a-a’、b-b’、c-c’、d-d’、e-e’、f-f’、g-g’、h-h’、i-i’:线

52.c1:第一电容电极

53.c2:第二电容电极

54.c3:第三电容电极

55.d1、d1’:垂直距离

56.dl:数据线

57.hd1:水平间距

58.hd2:水平间距

59.nd:法线方向

60.o:开口

61.pe:电极

62.sl:扫描线

63.t1、t2、t3:厚度

64.t1:第一主动元件

65.t2:第二主动元件

66.vl:信号线

67.th1、th2、th3、th4、th5、th6、th7、th8、th9、th10、th11、th12、th13、th14、th15:通孔

具体实施方式

68.图1a是依照本发明的一实施例的一种主动元件基板的上视示意图。图1b是图1a的线a-a’的剖面示意图。

69.请参考图1a与图1b,主动元件基板10包括基板100、半导体图案110、栅极绝缘层120、第一导电层130、第一介电层140、辅助导电层150、第二介电层160以及第二导电层170。在本实施例中,第一主动元件t1位于基板100上,且包括第一半导体层112、第一栅极132、第一源极172以及第一漏极174。

70.基板100的材料包括玻璃、石英、有机聚合物、或是不透光/反射材料(例如:导电材料、金属、晶片、陶瓷或其他可适用的材料)或是其他可适用的材料。缓冲层102形成于基板100上。缓冲层102例如包括单层或多层绝缘层。

71.半导体图案110包括第一半导体层112。在本实施例中,半导体图案110还包括第一电容电极c1。半导体图案110位于基板100上。在一些实施例中,半导体图案110形成于缓冲层102上。举例来说,第一半导体层112以及第一电容电极c1直接沉积于缓冲层102上。在一些实施例中,半导体图案110的材料包括非晶硅、多晶硅、微晶硅、单晶硅、有机半导体材料、氧化物半导体材料(例如:铟锌氧化物、铟镓锌氧化物或是其他合适的材料、或上述的组

合)、三五族化合物半导体或其他合适的材料或上述材料的组合。

72.第一半导体层112为经掺杂的半导体层,且包括依序连接的第一重掺杂区112a、第一轻掺杂区112b、沟道区112c、第二轻掺杂区112d以及第二重掺杂区112e。沟道区112c位于第一轻掺杂区112b以及第二轻掺杂区112d之间,第一轻掺杂区112b位于第一重掺杂区112a以及沟道区112c之间,且第二轻掺杂区112d位于第二重掺杂区112e以及沟道区112c之间。第一重掺杂区112a以及第二重掺杂区112e的掺杂浓度大于第一轻掺杂区112b以及第二轻掺杂区112d的掺杂浓度,且第一轻掺杂区112b以及第二轻掺杂区112d的掺杂浓度大于沟道区112c的掺杂浓度。第一半导体层112为p型半导体或n型半导体。

73.第一电容电极c1为经掺杂的半导体,且第一电容电极c1的掺杂浓度例如约等于第一重掺杂区112a以及第二重掺杂区112e的掺杂浓度。

74.栅极绝缘层120形成于半导体图案110上。在本实施例中,栅极绝缘层120形成于第一半导体层112、第一电容电极c1以及缓冲层102上。举例来说,栅极绝缘层120直接沉积于第一半导体层112以及缓冲层102上。栅极绝缘层120的材料例如包括无机材料(例如:氧化硅、氮化硅、氮氧化硅、氧化铪、氧化铝、其他合适的材料、或上述至少二种材料的堆叠层)、有机材料或其他合适的材料或上述的组合。在本实施例中,栅极绝缘层120的厚度t1为50纳米至150纳米。

75.第一导电层130包括第一栅极132。在本实施例中,第一导电层130还包括第二电容电极c2。第一导电层130形成于栅极绝缘层120上。举例来说,第一栅极132与第二电容电极c2直接沉积于栅极绝缘层120上,且直接接触栅极绝缘层120的上表面。第一导电层130的材料包括铬、金、银、铜、锡、铅、铪、钨、钼、钕、钛、钽、铝、锌、前述金属的合金或前述金属的堆叠层或其他导电材料。第一栅极132在基板100的法线方向nd上重叠于第一半导体层112的沟道区112c。在一些实施例中,第一半导体层112的第一轻掺杂区112b以及第二轻掺杂区112d的形成方法包括以第一栅极132为掩模而进行离子注入制作工艺,因此,第一栅极132在法线方向nd上对齐第一半导体层112的沟道区112c。另外,图1a省略绘示了连接至第一栅极132的信号线。在一些实施例中,连接至第一栅极132的信号线(未示出)与第一栅极132都属于第一导电层130,且两者连成一体,但本发明不以此为限。在其他实施例中,连接至第一栅极132的信号线(未示出)与第一栅极132属于不同导电层,且通过贯穿一层以上的绝缘层的通孔而彼此相连。

76.第二电容电极c2在基板100的法线方向nd上重叠于第一电容电极c1。

77.在一些实施例中,第一导电层130除了第一栅极132以及电容电极c2之外还包括其他导电结构,例如信号线或其他电极。

78.第一介电层140形成于第一导电层130以及栅极绝缘层120上。在一些实施例中,第一介电层140直接沉积于第一导电层130以及栅极绝缘层120上,且直接接触第一栅极132的上表面以及栅极绝缘层120的上表面。第一介电层140的材料例如包括无机材料(例如:氧化硅、氮化硅、氮氧化硅、氧化铪、氧化铝、其他合适的材料、或上述至少二种材料的堆叠层)、有机材料或其他合适的材料或上述的组合。在本实施例中,第一介电层140的厚度t2为50纳米至300纳米。

79.辅助导电层150包括遮蔽电极152。在本实施例中,辅助导电层150还包括第三电容电极c3。辅助导电层150形成于第一介电层140上。举例来说,遮蔽电极152以及第三电容电

极c3直接沉积于第一介电层140上,并直接接触第一介电层140的上表面。遮蔽电极152在基板100的法线方向nd上重叠于第一半导体层112的第二轻掺杂区112d。在一些实施例中,遮蔽电极152在基板100的法线方向nd上完全覆盖第二轻掺杂区112d。在本实施例中,遮蔽电极152与第一半导体层112的第二轻掺杂区112d之间的垂直距离d1为100纳米至450纳米。辅助导电层150的材料与第一导电层130的材料相同或不同。在本实施例中,辅助导电层150的材料与第一导电层130的材料相同,且包括铬、金、银、铜、锡、铅、铪、钨、钼、钕、钛、钽、铝、锌、前述金属的合金或前述金属的堆叠层或其他导电材料。

80.在本实施例中,遮蔽电极152为浮置电极。换句话说,在本实施例中,遮蔽电极152未连接至信号线,且未直接施加任何电压至遮蔽电极152。

81.第三电容电极c3在基板100的法线方向nd上重叠于第一电容电极c1以及第二电容电极c2。

82.在一些实施例中,辅助导电层150除了遮蔽电极152以及第三电容电极c3之外还包括其他导电结构,例如信号线或其他电极。

83.在本实施例中,由于遮蔽电极152与第三电容电极c3形成于相同导电层,由此能节省制作工艺所需的光掩模数量。

84.在本实施例中,第二介电层160形成于第一介电层140以及辅助导电层150上。举例来说,第二介电层160直接沉积于第一介电层140、遮蔽电极152以及第三电容电极c3上,并直接接触第一介电层140的上表面、遮蔽电极152的上表面以及第三电容电极c3的上表面。第二介电层160的材料例如包括无机材料(例如:氧化硅、氮化硅、氮氧化硅、氧化铪、氧化铝、其他合适的材料、或上述至少二种材料的堆叠层)、有机材料或其他合适的材料或上述的组合。在本实施例中,第二介电层160的厚度t3为50纳米至600纳米。

85.第二导电层170包括第一源极172以及第一漏极174。第二导电层170形成于第二介电层160上。举例来说,第一源极172以及第一漏极174直接沉积于第二介电层160上,并直接接触第二介电层160的上表面。第二导电层170与辅助导电层150的材料相同或不同。在本实施例中,第二导电层170与辅助导电层150的材料不同,且第二导电层170包括铬、金、银、铜、锡、铅、铪、钨、钼、钕、钛、钽、铝、锌、前述金属的合金或前述金属的堆叠层或其他导电材料。

86.第一源极172电连接至第一半导体层112的第一重掺杂区112a。在本实施例中,第一源极172通过栅极绝缘层120的通孔th1、第一介电层140的通孔th2以及第二介电层160的通孔th3而电连接至第一重掺杂区112a。在本实施例中,通孔th1、通孔th2以及通孔th3彼此完全重叠,但本发明不以此为限。在其他实施例中,通孔th1、通孔th2以及通孔th3可以彼此部分重叠。

87.第一漏极174电连接至第一半导体层112的第二重掺杂区112e。在本实施例中,第一漏极174通过栅极绝缘层120的通孔th4、第一介电层140的通孔th5以及第二介电层160的通孔th6而电连接至第一重掺杂区112e。在本实施例中,通孔th4、通孔th5以及通孔th6彼此完全重叠,但本发明不以此为限。在其他实施例中,通孔th4、通孔th5以及通孔th6可以彼此部分重叠。

88.在本实施例中,在对第一栅极132以及第一漏极174施加电压时,第一重掺杂区112e与第一栅极132之间会形成电场(如附图中虚线箭头所示)。在本实施例中,遮蔽电极152可用于分散第一重掺杂区112e与第一栅极132之间的电场,使第一重掺杂区112e与第一

栅极132之间的电场减小,由此改善热载流子效应(hot carrier effect)对第一主动元件t1造成的影响,避免第一主动元件t1因为热载流子效应而劣化。在一些实施例中,无论第一主动元件t1为p型薄膜晶体管或n型薄膜晶体管,遮蔽电极152都可用于分散半导体层与栅极之间的电场,由此改善热载流子效应对第一主动元件t1造成的影响。

89.钝化层180形成于第二导电层170上,且覆盖第一主动元件t1。

90.基于上述,通过遮蔽电极152的设置,第一主动元件t1的热载流子效应可以被减轻,由此改善了第一主动元件t1的劣化问题。此外,通过使遮蔽电极152与第三电容电极c3形成于相同导电层,可以节省装置的制造成本。

91.图2a是依照本发明的一实施例的一种主动元件基板的上视示意图。图2b是图2a的线b-b’的剖面示意图。图2c是图2a的线c-c’的剖面示意图。

92.在此必须说明的是,图2a至图2c的实施例沿用图1a和图1b的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

93.请参考图2a至图2c,在本实施例中,主动元件基板20包括基板100、半导体图案110、栅极绝缘层120、第一导电层130、第一介电层140、辅助导电层150、第二介电层160以及第二导电层170。在本实施例中,第一主动元件t1以及第二主动元件t2位于基板100上。第一主动元件t1包括第一半导体层112、第一栅极132、第一源极172以及第一漏极174。第二主动元件t2包括第二半导体层114、第二栅极134、第二源极176以及第二漏极178。

94.在本实施例中,半导体图案110包括第一半导体层112以及第二半导体层114。

95.第二半导体层114为经掺杂的半导体层,且包括依序连接的第一重掺杂区114a、第一轻掺杂区114b、沟道区114c、第二轻掺杂区114d以及第二重掺杂区114e。沟道区114c位于第一轻掺杂区114b以及第二轻掺杂区114d之间,第一轻掺杂区114b位于第一重掺杂区114a以及沟道区114c之间,且第二轻掺杂区114d位于第二重掺杂区114e以及沟道区114c之间。第一重掺杂区114a以及第二重掺杂区114e的掺杂浓度大于第一轻掺杂区114b以及第二轻掺杂区114d的掺杂浓度,且第一轻掺杂区114b以及第二轻掺杂区114d的掺杂浓度大于沟道区114c的掺杂浓度。第一半导体层114为p型半导体或n型半导体。

96.虽然在本实施例中,第一半导体层112以及第二半导体层114属于相同膜层(都属于半导体图案110),且为同时形成,但本发明不以此为限。在其他实施例中,第一半导体层112以及第二半导体层114包括不同材料,且第一半导体层112以及第二半导体层114属于不同膜层(即半导体图案110包括第一半导体层112,但半导体图案110不包括第二半导体层114,换句话说,第一半导体层112与第二半导体层114可通过不同图案化制作工艺所形成)。

97.第一导电层130包括第一栅极132以及第二栅极134。第二栅极134在基板100的法线方向nd上重叠于第二半导体层114。在一些实施例中,第二半导体层114的第一轻掺杂区114b以及第二轻掺杂区114d的形成方法包括以第二栅极134为掩模而进行离子注入制作工艺,因此,第二栅极134在法线方向nd上对齐第二半导体层114的沟道区114c。

98.在本实施例中,第一导电层130还包括扫描线sl。扫描线sl连接第二栅极134。

99.第二导电层170包括第一源极172、第一漏极174、第二源极176以及第二漏极178。

100.第二源极176电连接至第二半导体层114的第一重掺杂区114a。在本实施例中,第二源极176通过栅极绝缘层120的通孔th7、第一介电层140的通孔th8以及第二介电层160的

通孔th9而电连接至第一重掺杂区114a。在本实施例中,通孔th7、通孔th8以及通孔th9彼此完全重叠,但本发明不以此为限。在其他实施例中,通孔th7、通孔th8以及通孔th9可以彼此部分重叠。

101.第二漏极178电连接至第二半导体层114的第二重掺杂区114e。在本实施例中,第二漏极178通过栅极绝缘层120的通孔th10、第一介电层140的通孔th11以及第二介电层160的通孔th12而电连接至第一重掺杂区114e。在本实施例中,通孔th10、通孔th11以及通孔th12彼此完全重叠,但本发明不以此为限。在其他实施例中,通孔th10、通孔th11以及通孔th12可以彼此部分重叠。

102.第二漏极178电连接至第一栅极132。举例来说,第二通过位于第一介电层140的通孔th13以及第二介电层160的通孔th14而电连接至第一栅极132。在本实施例中,通孔th13以及通孔th14彼此完全重叠,但本发明不以此为限。在其他实施例中,通孔th13以及通孔th14可以彼此部分重叠。

103.在本实施例中,第二导电层170还包括数据线dl以及信号线vl。数据线dl连接第二源极176,信号线vl连接第一源极172。

104.钝化层180形成于第二导电层170上,且覆盖第一主动元件t1以及第二主动元件t2。

105.电极pe位于钝化层180上,且通过钝化层180的开口o而电连接至第一主动元件t1的第一漏极174。电极pe例如可用于控制液晶、发光二极管、感光元件或其他电子元件。

106.在本实施例中,遮蔽电极152在基板100的法线方向nd上重叠于第一半导体层112的第二轻掺杂区112d以及第一栅极132。部分第一栅极132位于遮蔽电极152与第一半导体层112之间。因此,遮蔽电极152除了可以改善热载流子效应对第一主动元件t1造成的影响之外,还可以用于增加第一主动元件t1中的电容。

107.图3a是依照本发明的一实施例的一种主动元件基板的上视示意图。图3b是图3a的线d-d’的剖面示意图。

108.在此必须说明的是,图3a和图3b的实施例沿用图1a和图1b的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

109.请参考图3a与图3b,主动元件基板30的遮蔽电极152在基板100的法线方向nd上重叠于第一半导体层112的第一轻掺杂区112b、沟道区112c、第二轻掺杂区112d以及第一栅极132。在本实施例中,遮蔽电极152除了可以改善热载流子效应对第一主动元件t1造成的影响之外,还可以用于增加第一主动元件t1中的电容(遮蔽电极152与第一栅极132之间的电容)。

110.在本实施例中,遮蔽电极152自第二轻掺杂区112d上方延伸至第一轻掺杂区112b上方,由此增加遮蔽电极152与第一栅极132之间的重叠面积。基于此,遮蔽电极152与第一栅极132之间的电容得以提升。

111.图4a是依照本发明的一实施例的一种主动元件基板的上视示意图。图4b是图4a的线e-e’的剖面示意图。

112.在此必须说明的是,图4a和图4b的实施例沿用图4a和图4b的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内

容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

113.请参考图4a与图4b,在主动元件基板40中,第二导电层170包括遮蔽电极173,且第二导电层170形成于第二介电层160上。举例来说,第一源极172、遮蔽电极173以及第一漏极174直接沉积于第二介电层160上,并直接接触第二介电层160的上表面。第二导电层170与第一导电层130的材料相同或不同。第一源极172、遮蔽电极173以及第一漏极174为相同导电层,且同时形成。遮蔽电极173分离于第一源极172以及第一漏极174。遮蔽电极173位于第一源极172与第一漏极174之间。遮蔽电极173与第一源极172之间的水平间距hd1视图案化制作工艺时所使用的工具的曝光极限(或称临界尺寸(critical dimension;cd))而定。举例来说,水平间距hd1大于或等于前述曝光极限与沟道区112c长度的合,且遮蔽电极173与第一漏极174之间的水平间距hd2大于或等于前述曝光极限。

114.遮蔽电极173在基板100的法线方向nd上重叠于第一半导体层112的第二轻掺杂区112d。在一些实施例中,遮蔽电极173在基板100的法线方向nd上完全覆盖第二轻掺杂区112d。在本实施例中,遮蔽电极173与第一半导体层112的第二轻掺杂区112d之间的垂直距离d1’为100纳米至1000纳米。在本实施例中,遮蔽电极173为浮置电极。换句话说,在本实施例中,遮蔽电极173未连接至其他信号线,且未直接施加任何电压至遮蔽电极173。

115.基于上述,通过遮蔽电极173的设置,第一主动元件t1的热载流子效应可以被减轻,由此改善了第一主动元件t1的劣化问题。此外,通过使第一源极172、遮蔽电极173以及第一漏极174形成于相同导电层,能节省制作工艺所需的光掩模数量。

116.图5a是依照本发明的一实施例的一种主动元件基板的上视示意图。图5b是图5a的线f-f’的剖面示意图。

117.在此必须说明的是,图5a和图5b的实施例沿用图1a和图1b的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

118.请参考图5a与图5b,在主动元件基板50中,遮蔽电极152电连接至第一漏极174。

119.第一漏极174通过依序相连的栅极绝缘层120的通孔th4、第一介电层140的通孔th5以及第二介电层160的通孔th6而电连接至第一重掺杂区112e。在本实施例中,通孔th6在基板100的法线方向nd上重叠于通孔th5以及通孔th4,且通孔th6的尺寸大于通孔th5的尺寸以及通孔th4的尺寸。

120.在一些实施例中,部分遮蔽电极152位于第一介电层140与通孔th6之间。在一些实施例中,形成通孔th4、通孔th5以及通孔th6的方法例如是在第二介电层160上形成一掩模层,该掩模层具有尺寸对应于通孔th6的开口,且该开口部分重叠于遮蔽电极152。基于前述开口蚀刻第二介电层160、第一介电层140以及栅极绝缘层120,由于遮蔽电极152可保护位于其下面的第一介电层140以及栅极绝缘层120,蚀刻制作工艺所形成的第二介电层160的通孔th6的尺寸大于第一介电层140的通孔th5的尺寸以及栅极绝缘层120的通孔th4的尺寸。

121.基于上述,通过遮蔽电极152的设置,第一主动元件t1的热载流子效应可以被减轻,由此改善了第一主动元件t1的劣化问题。

122.图6a是依照本发明的一实施例的一种主动元件基板的上视示意图。图6b是图6a的线g-g’的剖面示意图。

123.在此必须说明的是,图6a和图6b的实施例沿用图5a和图5b的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

124.请参考图6a与图6b,主动元件基板60的遮蔽电极152在基板100的法线方向nd上重叠于第一半导体层112的第一轻掺杂区112b、沟道区112c、第二轻掺杂区112d以及第一栅极132。在本实施例中,遮蔽电极152除了可以改善热载流子效应对第一主动元件t1造成的影响之外,还可以用于增加第一主动元件t1中的电容。

125.在本实施例中,遮蔽电极152自第二轻掺杂区112d上方延伸至第一轻掺杂区112b上方,由此增加遮蔽电极152与第一栅极132之间的重叠面积。基于此,遮蔽电极152与第一栅极132之间的电容得以提升。

126.图7a是依照本发明的一实施例的一种主动元件基板的上视示意图。图7b是图7a的线h-h’的剖面示意图。

127.在此必须说明的是,图7a和图7b的实施例沿用图1a和图1b的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

128.请参考图7a与图7b,在主动元件基板70中,遮蔽电极152电连接至第一源极172。

129.栅极绝缘层120中具有通孔th1,第一介电层140中具有通孔th2,第二介电层160中具有通孔th3。第一源极172通过依序相连的栅极绝缘层120的通孔th1、第一介电层140的通孔th2以及第二介电层160的通孔th3而电连接至第一重掺杂区112a。此外,第一源极172通过第二介电层160的通孔th15而电连接至遮蔽电极152。

130.在本实施例中,第一源极172在基板100的法线方向nd上重叠于第一轻掺杂区112b、沟道区112c以及第二轻掺杂区112d。

131.基于上述,通过遮蔽电极152的设置,第一主动元件t1的热载流子效应可以被减轻,由此改善了第一主动元件t1的劣化问题。此外,通过使遮蔽电极152与第三电容电极c3形成于相同导电层,可以节省装置的制造成本。

132.图8a是依照本发明的一实施例的一种主动元件基板的上视示意图。图8b是图8a的线i-i’的剖面示意图。

133.在此必须说明的是,图8a和图8b的实施例沿用图7a和图7b的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

134.请参考图8a与图8b,在主动元件基板80中,遮蔽电极152电连接至第一源极172。

135.在本实施例中,第一源极172具有绕过第一轻掺杂区112b以及沟道区112c的延伸部172e,第一源极172的延伸部172e连接遮蔽电极152,使第一源极172在基板100的法线方向nd上不重叠于第一轻掺杂区112b以及沟道区112c。

136.通过延伸部172e的设计,第一源极172与第一栅极132之间的寄生电容得以减少。

137.基于上述,通过遮蔽电极152的设置,第一主动元件t1的热载流子效应可以被减轻,由此改善了第一主动元件t1的劣化问题。此外,通过使遮蔽电极152与第三电容电极c3形成于相同导电层,可以节省装置的制造成本。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1