一种探针卡板的制作方法

1.本实用新型涉及芯片测试领域,尤其涉及一种探针卡板。

背景技术:

2.探针卡板作为一种高精密电子元件,主要应用在芯片尚未封装前,通过将探针卡板上的探针与芯片上的焊垫或凸块进行接触,从而接收芯片讯号,筛选出不良产品。探针卡板是芯片制造中影响极大的高精密器件,也是确保芯片良品率和成本控制的重要环节。在使用时,通常是通过测试机台发送测试信号,经探针卡板到待测物,再由待测物回送测试结果信号,经探针卡板到测试机台进行分析。由于每一种芯片的构造和所要达到的目的不同,必要的测试方法也有所不同,这就要求同一类型的芯片测试必须配有特定的探针卡板进行测试。

技术实现要素:

3.为了测试半导体芯片型号c108-2500,所以针对这样型号的半导体芯片需要配套的探针卡板对其进行测试,本实用新型采用以下技术方案:

4.本实用新型提供了一种探针卡板,包括pcb板,pcb板上连接有trim测试板、继电器控制单元、第一继电器组、第二继电器组、第三继电器;

5.pcb板上开设有芯片测试槽,芯片测试槽用于放置待检测的型号为c108-2500的半导体芯片u1;trim测试板上设有32个对称的测试触点;

6.第一继电器组包括6个继电器,分别为继电器ks、kcs0、kcs1、km、kim、kcf_cs;第二继电器组包括12个继电器,分别为继电器kt1~kt12;第三继电器组包括2个继电器,分别为继电器kio、k4。

7.继电器控制单元上设有芯片功能模块引脚、第一电流电压控制引脚、第二电流电压控制引脚、输出信号引脚。其中:继电器控制单元为jp接线牛角,jp接线牛角的ur9~ur14引脚为第一电流电压控制引脚;jp接线牛角的ur3~ur8引脚为第二电流电压控制引脚;jp接线牛角的ur1~ur2引脚为第三电流电压控制引脚;jp接线牛角的a2f引脚、a2s引脚、d2f引脚、d2s引脚连接、c4f引脚、c4s引脚为输出信号引脚;jp接线牛角的b2f引脚、b2s引脚、c2f引脚、c2s引脚、a4f引脚、a4s引脚、b4f引脚、b4s引脚、d4f引脚、d4s引脚为芯片功能模块引脚;jp接线牛角的ur引脚外接+5v电压;jp接线牛角的a3gf、a3gs、a4gs、a4gf、a1gf、a1gs、a2gs、a2gf引脚接地;

8.1.第一继电器组连接分别连接第一电流电压控制引脚以及待检测的芯片带有熔丝的引脚,实现熔丝的熔断。具体连接方式如下:

9.ur9引脚分别与继电器kt10和继电器kt12的线圈一端连接;ur10引脚分别与继电器kt9和继电器kt10的线圈一端连接;ur11引脚分别与继电器kt8和继电器kt7的线圈一端连接;ur12引脚分别与继电器kt6和继电器kt5的线圈一端连接;ur13引脚分别与继电器kt4和继电器kt3的线圈一端连接;ur14引脚分别与继电器kt2和继电器kt1的线圈一端连接;

10.继电器kt1~继电器kt12中,每个继电器控制两对常闭触点,继电器kt1的一常闭触点kt1_s1a的一端与trim测试板的47引脚连接,另一端与u1的f4触点连接,另一常闭触点kt1_s1b的一端与trim测试板的46和48引脚连接,另一端与u1的vss3触点连接;继电器kt2的一常闭触点kt2_s1a的一端与trim测试板的45引脚连接,另一端与u1的f3触点连接,另一常闭触点kt2_s1b的一端与trim测试板的43引脚连接,另一端与u1的f2触点连接;继电器kt3的一常闭触点kt3_s1a的一端与trim测试板的42和44引脚连接,另一端与u1的vss1触点连接,另一常闭触点kt3_s1b的一端与trim测试板的41引脚连接,另一端与u1的f1触点连接;继电器kt4的一常闭触点kt4_s1a的一端与trim测试板的39引脚连接,另一端与u1的f5触点连接,另一常闭触点kt4_s1b的一端与trim测试板的40和38引脚连接,另一端与u1的vss5触点连接;继电器kt5的一常闭触点kt5_s1a的一端与trim测试板的35引脚连接,另一端与u1的f6触点连接,另一常闭触点kt5_s1b的一端与trim测试板的37引脚连接,另一端与u1的f7触点连接;继电器kt6的一常闭触点kt6_s1a的一端与trim测试板的36和34引脚连接,另一端与u1的vss7触点连接,另一常闭触点kt6_s1b的一端与trim测试板的33引脚连接,另一端与u1的f8触点连接;继电器kt7的一常闭触点kt7_s1a的一端与trim测试板的15引脚连接,另一端与u1的f14触点连接,另一常闭触点kt7_s1b的一端与trim测试板的16和14引脚连接,另一端与u1的vss14触点连接;继电器kt8的一常闭触点kt8_s1a的一端与trim测试板的13引脚连接,另一端与u1的f15触点连接,另一常闭触点kt8_s1b的一端与trim测试板的11引脚连接,另一端与u1的f11触点连接;继电器kt9的一常闭触点kt9_s1a的一端与trim测试板的10和12引脚连接,另一端与u1的vss11触点连接,另一常闭触点kt9_s1b的一端与trim测试板的9引脚连接.另一端与u1的f16触点连接;继电器kt10的一常闭触点kt10_s1a的一端与trim测试板的7引脚连接,另一端与u1的f12触点连接,另一常闭触点kt10_s1b的一端与trim测试板的8和6引脚连接;另一端与u1的vss9触点连接;继电器kt11的一常闭触点kt11_s1a的一端与trim测试板的5引脚连接,另一端与u1的f9触点连接,另一常闭触点kt11_s1b的一端与trim测试板的3引脚连接;另一端与u1的f10触点连接;继电器kt12的一常闭触点kt12_s1a的一端与trim测试板的2和4引脚连接,另一端与u1的vss10触点连接,另一常闭触点kt12_s1b的一端与trim测试板的1引脚连接,另一端与u1的f13触点连接。

11.2.第二电流电压控制引脚、第二继电器组、待测的芯片的功能模块引脚连接,实现芯片功能的测试。具体连接方式如下:

12.ur3引脚与继电器ks的线圈一端连接,ur4引脚与继电器kcs0的线圈一端连接,ur5引脚与继电器kcs1的线圈一端连接,ur6引脚与继电器km的线圈一端连接;ur7引脚与继电器kim的线圈一端连接,ur8引脚与继电器kcf_cs的线圈一端连接。

13.继电器kcs1的一常闭触点kcs1_s1a的一端与电容c1的一端连接,常闭触点kcs1_s1a的另一端与电阻r1一端连接,电阻r1另一端接地;电容c1的另一端连接与继电器kcf的一常闭触点kcf_cs_s1a的一端连接,继电器kcf的一常闭触点kcf_cs_s1a的另一端与u1的vss2和cf触点连接;

14.jp1接线牛角的a4f以及a4s引脚与继电器kcso的一常闭触点kcso_s1a的一端连接,常闭触点kcso_s1a的另一端分别与u1的cs触点、电容c1的一端、常闭触点kcs1_s1a的一端连接。

15.jp1接线牛角的b4f以及b4s引脚与继电器kim的一常闭触点kim_s1a的一端连接,

常闭触点kim_s1a的另一端分别与u1的vss7、im触点连接;

16.jp1接线牛角的b2f以及b2s引脚与u1的d1触点连接;

17.3.第三电流电压控制引脚、第三继电器组、输出信号引脚连接,实现芯片输出信号测试。具体连接方式如下:

18.ur1引脚与继电器ki0的线圈一端连接,ur2引脚与继电器k4的线圈一端连接。

19.u1的d2触点、d4触点、io触点为芯片熔丝后测试输出端,为了测试的稳定性和准确性,在调试阶段又在pcb板上增加了电容c1、电容c2、电容c3、电阻r1、电阻r2、电阻r3来优化了电路。

20.jp1接线牛角的a2f以及a2s引脚与u1的d2触点连接;

21.jp1接线牛角的c2f以及c2s引脚与电阻r3的一端连接,电阻r3的另一端的分别与电容c3的一端、继电器kio的一常闭触点kio_s1a的一端连接,常闭触点kio_s1a的另一端与u1的io触点连接,电容c3的另一端接地。

22.jp1接线牛角的d2f以及d2s引脚与继电器k4的一常闭触点k4_s1a的一端连接,k4_s1a的另一端与电阻r2的一端连接,电阻r2的另一端分别与u1的d4触点、电容c2的一端连接,电容c2的另一端接地。

23.综上所述,通过继电器给特定的电压或者电流作为芯片的输入端,电流经过芯片,通过继电器以及继电器控制单元熔断芯片内部的熔丝,修改芯片,使得芯片达到测试要求。通过这种探针卡可以准确的测试出每一个芯片c108-2500是否可以达到合格要求,以便筛选出来的合格芯片进入下一生产环节。

附图说明

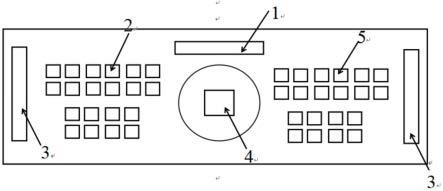

24.图1是一种探针卡板中jp接线牛角;

25.图2是一种探针卡板中芯片连接的电路图;

26.图3是一种探针卡板中对应jp接线牛角的继电器的电路图;

27.图4是一种探针卡板中trim测试板的电路图;

28.图5是一种探针卡板的结构图;

29.附图标记:

30.1trim测试板;2第一继电器组;3jp接线牛角;4测试槽;5第二继电器组。

具体实施方式

31.下面结合图1至图5对本实用新型做进一步说明。

32.为了测试型号为c108-2500的半导体芯片u1,本实用新型提供了一种探针卡板,包括pcb板,pcb板上连接有trim测试板、继电器控制单元、第一继电器组、第二继电器组;

33.pcb板上开设有芯片测试槽,芯片测试槽用于放置待检测的型号为c108-2500的半导体芯片u1;trim测试板上设有32个对称的测试触点;

34.第一继电器组为kt1~kt12继电器;第二继电器组为kio、k4、ks、kcs0、kcs1、km、kim、kcf_cs继电器。

35.继电器控制单元上设有芯片功能模块引脚、第一电流电压控制引脚、第二电流电压控制引脚、输出信号引脚;其中:继电器控制单元为jp接线牛角,jp接线牛角的ur9~ur14

引脚为第一电流电压控制引脚;jp接线牛角的ur1~ur8引脚为第二电流电压控制引脚;jp接线牛角的a2f引脚、a2s引脚、d2f引脚、d2s引脚连接、c4f引脚、c4s引脚为输出信号引脚;jp接线牛角的b2f引脚、b2s引脚、c2f引脚、c2s引脚、a4f引脚、a4s引脚、b4f引脚、b4s引脚、d4f引脚、d4s引脚为芯片功能模块引脚;jp接线牛角的ur引脚外接+5v电压;jp接线牛角的a3gf、a3gs、a4gs、a4gf、a1gf、a1gs、a2gs、a2gf引脚接地。

36.第一继电器组连接分别连接电流电压控制引脚以及待检测的芯片带有熔丝的引脚,实现熔丝的熔断。具体连接方式如下:

37.ur9引脚分别与继电器kt10和继电器kt12的线圈一端连接;ur10引脚分别与继电器kt9和继电器kt10的线圈一端连接;ur11引脚分别与继电器kt8和继电器kt7的线圈一端连接;ur12引脚分别与继电器kt6和继电器kt5的线圈一端连接;ur13引脚分别与继电器kt4和继电器kt3的线圈一端连接;ur14引脚分别与继电器kt2和继电器kt1的线圈一端连接;

38.继电器kt1~继电器kt12中,每个继电器控制两对常闭触点,继电器kt1的一常闭触点kt1_s1a的一端与trim测试板的47引脚连接,另一端与u1的f4触点连接,另一常闭触点kt1_s1b的一端与trim测试板的46和48引脚连接,另一端与u1的vss3触点连接;继电器kt2的一常闭触点kt2_s1a的一端与trim测试板的45引脚连接,另一端与u1的f3触点连接,另一常闭触点kt2_s1b的一端与trim测试板的43引脚连接,另一端与u1的f2触点连接;继电器kt3的一常闭触点kt3_s1a的一端与trim测试板的42和44引脚连接,另一端与u1的vss1触点连接,另一常闭触点kt3_s1b的一端与trim测试板的41引脚连接,另一端与u1的f1触点连接;继电器kt4的一常闭触点kt4_s1a的一端与trim测试板的39引脚连接,另一端与u1的f5触点连接,另一常闭触点kt4_s1b的一端与trim测试板的40和38引脚连接,另一端与u1的vss5触点连接;继电器kt5的一常闭触点kt5_s1a的一端与trim测试板的35引脚连接,另一端与u1的f6触点连接,另一常闭触点kt5_s1b的一端与trim测试板的37引脚连接,另一端与u1的f7触点连接;继电器kt6的一常闭触点kt6_s1a的一端与trim测试板的36和34引脚连接,另一端与u1的vss7触点连接,另一常闭触点kt6_s1b的一端与trim测试板的33引脚连接,另一端与u1的f8触点连接;继电器kt7的一常闭触点kt7_s1a的一端与trim测试板的15引脚连接,另一端与u1的f14触点连接,另一常闭触点kt7_s1b的一端与trim测试板的16和14引脚连接,另一端与u1的vss14触点连接;继电器kt8的一常闭触点kt8_s1a的一端与trim测试板的13引脚连接,另一端与u1的f15触点连接,另一常闭触点kt8_s1b的一端与trim测试板的11引脚连接,另一端与u1的f11触点连接;继电器kt9的一常闭触点kt9_s1a的一端与trim测试板的10和12引脚连接,另一端与u1的vss11触点连接,另一常闭触点kt9_s1b的一端与trim测试板的9引脚连接.另一端与u1的f16触点连接;继电器kt10的一常闭触点kt10_s1a的一端与trim测试板的7引脚连接,另一端与u1的f12触点连接,另一常闭触点kt10_s1b的一端与trim测试板的8和6引脚连接;另一端与u1的vss9触点连接;继电器kt11的一常闭触点kt11_s1a的一端与trim测试板的5引脚连接,另一端与u1的f9触点连接,另一常闭触点kt11_s1b的一端与trim测试板的3引脚连接;另一端与u1的f10触点连接;继电器kt12的一常闭触点kt12_s1a的一端与trim测试板的2和4引脚连接,另一端与u1的vss10触点连接,另一常闭触点kt12_s1b的一端与trim测试板的1引脚连接,另一端与u1的f13触点连接。

39.u1的d2触点、d4触点、io触点为芯片熔丝后测试输出端,为了测试的稳定性和准确性,在调试阶段又在pcb板上增加了电容c1、电容c2、电容c3、电阻r1、电阻r2、电阻r3来优化

了电路。

40.jp1接线牛角的a2f以及a2s引脚与u1的d2触点连接;

41.jp1接线牛角的c2f以及c2s引脚与电阻r3的一端连接,电阻r3的另一端的分别与电容c3的一端、继电器kio的一常闭触点kio_s1a的一端连接,常闭触点kio_s1a的另一端与u1的io触点连接,电容c3的另一端接地。

42.jp1接线牛角的d2f以及d2s引脚与继电器k4的一常闭触点k4_s1a的一端连接,k4_s1a的另一端与电阻r2的一端连接,电阻r2的另一端分别与u1的d4触点、电容c2的一端连接,电容c2的另一端接地。

43.芯片功能模块引脚、第二继电器组、待测的芯片的功能模块引脚连接,实现芯片功能的测试。具体连接方式如下:

44.ur1引脚与继电器ki0的线圈一端连接,ur2引脚与继电器k4的线圈一端连接,ur3引脚与继电器ks的线圈一端连接,ur4引脚与继电器kcs0的线圈一端连接,ur5引脚与继电器kcs1的线圈一端连接,ur6引脚与继电器km的线圈一端连接;ur7引脚与继电器kim的线圈一端连接,ur8引脚与继电器kcf_cs的线圈一端连接。

45.继电器kcs1的一常闭触点kcs1_s1a的一端与电容c1的一端连接,常闭触点kcs1_s1a的另一端与电阻r1一端连接,电阻r1另一端接地;电容c1的另一端连接与继电器kcf的一常闭触点kcf_cs_s1a的一端连接,继电器kcf的一常闭触点kcf_cs_s1a的另一端与u1的vss2和cf触点连接;

46.jp1接线牛角的a4f以及a4s引脚与继电器kcso的一常闭触点kcso_s1a的一端连接,常闭触点kcso_s1a的另一端分别与u1的cs触点、电容c1的一端、常闭触点kcs1_s1a的一端连接。

47.jp1接线牛角的b4f以及b4s引脚与继电器kim的一常闭触点kim_s1a的一端连接,常闭触点kim_s1a的另一端分别与u1的vss7、im触点连接;

48.jp1接线牛角的b2f以及b2s引脚与u1的d1触点连接;

49.通过继电器给特定的电压或者电流作为芯片的输入端,电流经过芯片,通过继电器以及继电器控制单元熔断芯片内部的熔丝,修改芯片,使得芯片达到测试要求。通过这种探针卡可以准确的测试出每一个芯片c108-2500是否可以达到合格要求,以便筛选出来的合格芯片进入下一生产环节。

50.可以理解的是,以上关于本实用新型的具体描述,仅用于说明本实用新型而并非受限于本实用新型实施例所描述的技术方案。本领域的普通技术人员应当理解,仍然可以对本实用新型进行修改或等同替换,以达到相同的技术效果;只要满足使用需要,都在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1