一种基于FPGA的多通道时间数字转换器

本发明涉及时间数字转换器技术和fpga数字电路,具体涉及一种基于fpga的多通道时间数字转换器。

背景技术:

1、时间数字转换器(time-to-digital converter,tdc)是一种将时间量转化为数字量以实现一个事件发生时刻的记录的功能器件;对于两个事件之间的时间间隔的测量,一般可以由两个tdc分别测量两个事件的发生时刻,两个发生时刻的差值就是该两个事件的时间间隔。因此技术特性,tdc在飞行时间(time of flight,tof)测量领域被广泛使用。在激光tof传感器中,入射信号和回波信号携带着传感器捕获的时间信息,通常达到亚纳秒甚至皮秒级别。因此,tdc的分辨率直接决定了tof传感器的性能,而tdc性能的提高将拓展tof传感器的应用前景。

2、tdc有模拟和数字两种实现方法。在早期阶段,数字tdc一般由特定应用集成电路(asic)实现。随着可编程门电路(field programmable gate array,fpga)的发展,fpga由于具有高灵活性和短开发周期的优势而被广泛关注。早期的tdc多为计数型tdc,但应用场景对tdc的分辨率要求正在不断提高,仅使用计数型tdc想要达到亚纳秒甚至皮秒级分辨率十分困难,为此研究人员发明了一系列时间内插方式对tdc的分辨率进行提高,如抽头延迟链测量法、wave union,多相位法、伪插值法(psdl)等方案,这些方案都能使得tdc的分辨率和精度低于一个时钟周期。

3、基于fpga的tdc设计,主要采用抽头延迟链测量法(tdl)的直接计数方式,能够达到皮秒级的时间分辨率。该测量方式通常是“粗测量”与“细测量”结合的测量方法,“粗测量”一般以脉冲计数法实现。“细测量”是通过在脉冲计数法的脉冲周期中内插更小的时间单元进而达到提升分辨率与精度的目的。“细测量”的分辨率与精度直接决定了时间数字转换器的分辨率与精度,“粗测量”与“细测量”结合的测量方案可以较好的兼顾保证tdc的量程与测量精度。

4、另一方面,当今对于多通道应用的需求也与日俱增,比如在自动驾驶中使用的高速激光雷达,高速飞行时间测量等。因此,tdc器件通常难以同时兼顾实现tdc的小型化和多通道设计,并且因多通道tdc容易导致逻辑资源的较大消耗,因此通常最多被限制到10通道左右,难以实现更多通道时间测量的扩充。所以,对于基于fpga的多通道tdc设计来说,对fpga的逻辑资源占用或死区时间问题会面临很大的挑战。

技术实现思路

1、针对上述现有技术的不足,本发明提供了一种基于fpga的多通道时间数字转换器,以在兼顾保证tdc的量程与测量精度的前提下,同时还实现低fpga逻辑资源占用的多通道tdc设计。

2、为了解决上述技术问题,本发明采用了如下的技术方案:

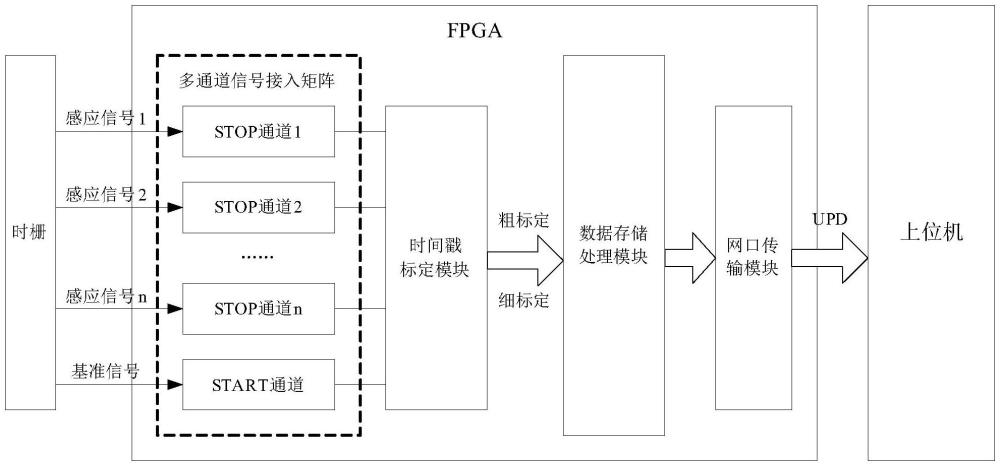

3、一种基于fpga的多通道时间数字转换器,包括多通道信号接入矩阵、时间戳标定模块、数据存储处理模块和网口传输模块;

4、所述多通道信号接入矩阵包括多个时间测量信号通道,所述时间测量信号通道包括时间测量的start信号以及多个不同通道的stop信号的信号通道,用于分别将时间测量的start信号以及各不同通道的stop信号接入至时间戳标定模块;

5、所述时间戳标定模块用于对时间测量的start信号以及各不同通道的stop信号分别标定生成各自对应的时间戳,传输至数据存储处理模块;

6、所述数据存储处理模块用于对时间戳标定模块的时间戳标定结果进行关系对应处理,并分别计算不同时间测量通道的stop信号各自与start信号之间的时间间隔,并加以存储;

7、所述网口传输模块用于从数据存储处理模块中读取不同时间测量通道的stop信号各自与start信号之间的时间间隔数据,上传至用于执行时间测量的上位机。

8、上述基于fpga的多通道时间数字转换器中,作为优选方案,所述时间戳标定模块包括环形振荡器、时间尺构建模块,以及分别对应不同时间测量信号通道的多个时间戳细标定通道;

9、所述环形振荡器用于生成时钟无关的振荡信号,用于作为码密度测试的输入信号;

10、所述时间尺构建模块包括一个循环计数器,所述循环计数器用于执行循环的方波计数,其方波计数信号的上升沿或下降沿用以作为时间戳标定的时间尺有效沿;

11、每个所述时间戳细标定通道对应一个时间测量信号通道,每个时间戳细标定通道均包括信号转换电路、抽头延迟链、触发器阵列、解码电路以及逐位校准电路;

12、所述信号转换电路用于将来自其对应时间测量信号通道的时间测量信号转换为st阶跃信号,以及将系统时钟信号转换为sp阶跃信号,并分别传送至抽头延迟链,且还将产生的sp阶跃信号传输至时间尺构建模块用以触发产生时间测量信号的粗标定时间戳,传输至数据存储处理模块;所述时间测量信号为时间测量的start信号或stop信号;

13、所述抽头延迟链由多个延迟单元组成,且每个延迟单元均设置有抽头,用于根据st阶跃信号对时间测量信号进行延时缓存,并能够通过抽头对外提供数据读取;

14、所述触发器阵列用于在sp阶跃信号的触发下对抽头延迟链中的各抽头状态进行锁存,并通过抽头读取得到带有时间测量信号的延迟信息的温度计码,传送至所述解码电路;

15、所述解码电路用于统计被锁存在抽头延迟链中抽头状态为1的数量,表示为数量二进制码,传送至逐位校准电路;

16、所述逐位校准电路用于采用码密度测试的方式对抽头延迟链中每个延迟单元的延迟时间进行逐位校准,并结合所述数量二进制码所指示的抽头延迟链中抽头状态为1的数量,统计得到时间测量信号的细标定时间戳,传输至数据存储处理模块。

17、上述基于fpga的多通道时间数字转换器中,作为优选方案,所述时间戳标定模块中,信号转换电路包括两个d触发器,分别为第一触发器和第二触发器;所述第一触发器用于将时间测量信号作为敏感信号,在时间测量信号的上升沿时将输出从低电平置为高电平,形成st阶跃信号,传送至抽头延迟链;所述第二触发器用于将系统时钟信号作为敏感信号,在系统时钟信号的上升沿时将输出从低电平置为高电平,形成sp阶跃信号,并分别传送至抽头延迟链和时间尺构建模块。

18、上述基于fpga的多通道时间数字转换器中,作为优选方案,所述时间戳标定模块中,抽头延迟链由fpga中的多个超前进位结构carry4作为延迟单元构成,每个延迟单元包含四个级联的二路复用器,每个二路复用器的输出端均设置有抽头;

19、所述解码电路以抽头延迟链中每个延迟单元的第一个抽头作为观测点,对温度计码中抽头状态的变化边界位置进行观测搜索。

20、上述基于fpga的多通道时间数字转换器中,作为优选方案,所述时间戳标定模块中,解码电路通过加法器对锁存在抽头延迟链中抽头状态进行逐位相加求和的方式,统计被锁存在抽头延迟链中抽头状态为1的数量,并表示为数量二进制码,传送至逐位校准电路。

21、上述基于fpga的多通道时间数字转换器中,作为优选方案,所述时间戳标定模块中,逐位校准电路通过fpga片内随机存储器ram采用码密度测试法分别统计抽头延迟链中每个延迟单元的延迟时间,形成码密度直方图,并从随机存储器ram读出码密度直方图,统计抽头延迟链中每个延迟单元的延迟时间,再计算得到时间测量信号的细标定时间戳;

22、逐位校准电路计算得到时间测量信号的细标定时间戳的方式为:

23、

24、tx为输出的时间测量信号的细标定时间戳,τi表示抽头延迟链中第i个抽头状态为1的延迟单元校准后的延迟时间,i=1,2,…,k,k表示抽头延迟链中抽头状态为1的数量。

25、上述基于fpga的多通道时间数字转换器中,作为优选方案,所述数据存储处理模块包括同步fifo单元、时间戳计算单元、时间间隔计算单元和异步fifo单元;

26、同步fifo单元用于存储时间戳标定模块得到的时间测量信号的粗标定时间戳和细标定时间戳;所述时间测量信号为时间测量的start信号或stop信号;

27、时间戳计算单元用于对时间测量信号的粗标定时间戳和细标定时间戳进行对应关系的整理,得到时间测量信号对应的时间戳数据;

28、时间间隔计算单元用于根据start信号以及各不同通道的stop信号各自对应的时间戳数据,分别计算每个时间测量通道的被测时间间隔;

29、异步fifo单元用于存储处理得到的各个时间测量通道的被测时间间隔。

30、上述基于fpga的多通道时间数字转换器中,作为优选方案,所述数据存储处理模块中,针对start信号的信号通道处理得到的被测时间间隔为start信号的周期间隔;针对任意一个stop信号的信号通道处理得到的被测时间间隔表示为:

31、

32、其中,result表示针对一个stop信号所在的时间测量通道的被测时间间隔;tstop表示该stop信号的时间戳数据,tstart表示该stop信号对应的start信号的时间戳数据;tclk表示系统时钟信号周期,n表示循环计数器的一个循环计数周期包含的系统时钟信号周期个数。

33、上述基于fpga的多通道时间数字转换器中,作为优选方案,所述数据存储处理模块中,针对每个时间测量信号通道分别设置有对应的同步fifo单元异步fifo单元,用于分别存储相应时间测量信号通道对应的时间戳和被测时间间隔,并且在每个异步fifo单元中设置有数据存储提取指示信号,用以指示该异步fifo单元中存储的被测时间间隔的数据量是否达到预设存储阈值。

34、上述基于fpga的多通道时间数字转换器中,作为优选方案,所述网口传输模块的数据读取传输控制方式为:

35、所述网口传输模块会按照预设频率和顺序依次对各个时间测量信号通道对应的异步fifo单元轮流进行传输对接,监测其传输对接的时间测量信号通道的数据存储提取指示信号的指示状态;若数据存储提取指示信号指示达到预设存储阈值,则从该传输对接的时间测量信号通道的异步fifo单元中读取出存储的被测时间间隔,上传至用于执行时间测量的上位机,然后按照预设频率和顺序跳转对接下一个时间测量信号通道;若数据存储提取指示信号指示未达到预设存储阈值,则按照预设频率和顺序直接跳转对接下一个时间测量信号通道。

36、本发明与现有技术相比,具有如下有益效果:

37、1、本发明基于fpga的多通道时间数字转换器,其采用时间戳标定法,由时间戳标定模块记录每个通道中信号有效沿的时间戳,能够准确计算通道间信号的时间间隔和信号周期,其中结合了“粗测量”与“细测量”的方法,粗测量通过脉冲计数法实现,细测量则通过内插更小的时间单元来提高分辨率和精度,实现高精度时间测量;并且,粗标定功能速度快、稳定性好、资源消耗低;而细标定功能精度高、适应性强、校准能力强且扩展性好。

38、2、本发明基于fpga的多通道时间数字转换器中,数据存储处理模块通过两级fifo的存储结构确保了start通道与stop通道的时间戳数据能够准确无误地一一对应,也为测量准确性提供了保证;通过异步fifo的设计,可以在不影响实时测量的同时,对数据进行缓冲和处理,提高了数据处理效率;同时,数据存储处理模块具有纠错功能,能够自检每个stop通道中的信号缺失,保证了整个tdc系统的运行稳定性;并且,由于采用了模块化的设计,可以方便地实现多通道tdc系统的通道灵活扩展。

39、3、本发明基于fpga的多通道时间数字转换器,实现了fpga逻辑资源占用低、处理速度快、且量程与测量精度得以兼顾保证的多通道tdc设计。

- 还没有人留言评论。精彩留言会获得点赞!