芯片核心调压补偿系统的制作方法

1.本发明涉及芯片技术领域,尤其涉及一种芯片核心调压补偿系统。

背景技术:

2.芯片核心通常维持在设定内部工作电压(vdd)下运行,但是当出现较大负载时,会造成芯片核心的内部工作电压下降,且负载越大,下降幅度越明显,当下降到一定程度时,会大大影响芯片核心的性能。由此可知,如何监控芯片核心内部工作电压变化,并及时准确地进行调压补偿,使得芯片核心尽可能维持在内部工作电压下运行,提高芯片核心的性能成为亟待解决的技术问题。

技术实现要素:

3.本发明目的在于,提供一种芯片核心调压补偿系统,能够及时对芯片核心进行调压补偿,提高了芯片核心的性能。

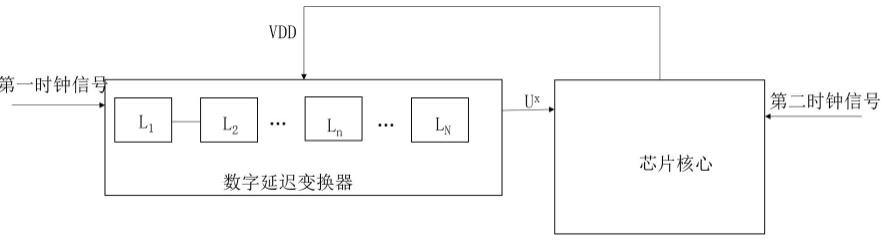

4.本发明提供了一种芯片核心调压补偿系统,包括与芯片核心相连接的数字延迟变换器和预先生成的数字延迟变换器的目标工作曲线;所述数字延迟变换器包括n个依次串联的延迟单元{l1,l2,

…

,ln,

…

,ln},ln为第n个延迟单元,n的取值范围为1到n,n为延迟单元的总数量,所述数字延迟变换器包括第一端口和第二端口,所述第一端口用于输入芯片核心的内部工作电压vdd,为每一ln供电,所述第二端口用于输入第一时钟信号,并按照l1,l2,

…

,ln,

…

,ln的顺序进行传输,ln延迟的时间为tn, tn与vdd的大小成反比;所述数字延迟变换器用于在t

x

时刻采集每一ln对应的时钟信号c

nx

,x=1,2,3

…

,获取c

1x

当前上升沿在每一c

nx

上对应的采样点,并依次标注在c

1x

上,输出位于c

1x

当前上升沿之后,且距离下降沿最近的采样点的序号u

x

,并传输给所述芯片核心;所述目标工作曲线的横坐标为vdd值,纵坐标为所述数字延迟变换器对应的目标输出采样点序号,基于所述目标工作曲线确定目标vdd值对应的目标序号u0,基于所述目标工作曲线确定采样点序号每减小一个单位所需补偿的电压值e;所述芯片核心用于将u

x

与目标序号u0比较,若u

0-u

x

》r,则基于u

0-u

x

和电压值e补偿vdd,其中,r为预设的序号差阈值。

5.本发明与现有技术相比具有明显的优点和有益效果。借由上述技术方案,本发明提供的一种芯片核心调压补偿系统可达到相当的技术进步性及实用性,并具有产业上的广泛利用价值,其至少具有下列优点:本发明所述系统基于数字延迟变换器监测芯片核心的内部工作电压变化,基于目标工作曲线确定采样点序号每减小一个单位所需补偿的电压值,基于电压变化幅度和采样点序号每减小一个单位所需补偿的电压值实施补偿芯片核心的内部工作电压,提高了芯片核心调压补偿的准确性和效率,提高了芯片核心的性能。

6.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够ux

)*e,此时可以选则现有的任何一种调压方式来基于需要补偿的电压(u

0-u

x

)*e实时调整vdd。需要说明的是,r的值根据具体的芯片核心调压补偿精度需求等因素综合决定。

16.作为一种实施例,本发明也可以基于以下所提出的调整方式对芯片核心进行调压补偿,具体的:所述芯片核心还用于接收第二时钟信号,在所述第二时钟信号下接收负载进行工作,可以理解的是,负载越大,vdd值越小。需要说明的是通过对第二时钟信号进行控制,可以减小负载,从而间接调整vdd值。所述芯片核心设置了m个时钟门控{ck1,ck2,

…

,ckm,

…

,ckm}和m个电压调整范围{v1,v2,

…

,vm,

…

,vm},ckm为第m个时钟门控,vm为第m个电压调整范围,ckm和vm一一对应。所述芯片核心用于判断在u

0-u

x

》r时,确定(u

0-u

x

)*e所属的vm,基于(u

0-u

x

)*e所属的vm确定对应的ckm,通过所述对应的ckm调整所述第二时钟信号,从而调整在所述第二时钟信号下接收负载,进而调整vdd,若u

0-u

x

≤r,所述芯片核心不对所述第二时钟信号设置时钟门控,需要说明的是,u

x

是连续采集的,针对每一u

x

均需判断u

0-u

x

是否大于r,并设置对应的时钟门控实时调整vdd,当u

0-u

x

≤r,如果当前没有设置时钟门控实时调整vdd,则保持不变,如果当前存在时钟门控实时调整vdd,则将对应的门控时钟去除。通过设置多个不同的门控时钟,按照电压调整范围能够准确及时地调整vdd,提高了芯片核心的内部工作电压的调整效率和准确率。

17.例如,目标vdd值为0.7v,n=32,对应的u0=7,r=2,当vdd下降,数字延迟变换器输出的u

x

=6时,由于u

0-u

x

=1《2,因此此时无需调压,当数字延迟变换器输出的u

x

=5时,u

0-u

x

=2,则需要启动对应的调压过程。

18.需要说明的是,m的具体取值可以根据芯片核心的内部工作电压的精确度等具体应用需求来设置,作为一种实施例,v1,v2,

…

,vm,

…

,v

m 依次变大,ck1,ck2,

…

,ckm,

…

,ck

m 的调整幅度也依次变大,m=2,ck1为1/2门控时钟,ck2为全门控时钟,也即当选择ck1调整芯片核心的内部工作电压时,将第二时钟信号中1/2的低电平变为高电平,从而会实现减少被拉高的1/2的电平对应的负载,当选择ck2调整芯片核心的内部工作电压时,将第二时钟信号中全部低电平拉高,从而会实现直接减少当前所有负载,使得vdd的值迅速回升。

19.作为一种实施例,所述数字延迟变换器还用于获取基于多个内部工作电压值vddy进行测试,生成多组测试数值对(vddy,uy),uy为vddy对应的输出采样点的序号,以内部工作电压为横坐标,以输出采样点的序号为纵坐标构建坐标系,基于所有(vddy,uy)在所述坐标系统拟合生成所述目标工作曲线,y=1,2,3,

…

,uy≤n。优选的,所述目标工作曲线为线性曲线,基于所述线性曲线获取采样点序号每减小一个单位所需补偿的电压值e=(vdd

y+1

‑ꢀ

vddy)/( u

y+1

‑ꢀ

uy)。需要说明的是,当基于目标工作曲线和vdd值确定对应的输出采样点的序号时,如果得到的输出采样点的序号为非整数时,则向下取整即可。

20.所述系统在纳秒级别进行调压补偿。作为一种实施例,一个导致vdd压降从发生压降到回升的时间为50ns,若需保障芯片核心性能不受影响,则通常需要在10ns左右完整压降的检测和补偿,因此,所述系统是需要在纳秒级进行调压补偿的。

21.本发明所述系统基于数字延迟变换器监测芯片核心的内部工作电压变化,基于目标工作曲线确定采样点序号每减小一个单位所需补偿的电压值,基于电压变化幅度和采样点序号每减小一个单位所需补偿的电压值实施补偿芯片核心的内部工作电压,提高了芯片核心调压补偿的准确性和效率,提高了芯片核心的性能。

22.以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽

然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容作出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1