内嵌式触控显示面板的制作方法

1.本发明是有关于一种触控显示面板,且特别是有关于一种将共同电极当作触控电极的内嵌式触控显示面板。

背景技术:

2.触控和显示驱动器整合单一芯片的架构是将显示面板中的数据线以及连接至触控电极的触控导线都连接至单一个芯片,借此这个单一个芯片可以同时控制显示与触控两个功能。如何设置触控导线,为此领域技术人员所关心的议题。

技术实现要素:

3.本发明的目的在于提供一种内嵌式触控显示面板,其触控电极可以作为共同电极使用,而感测线是形成在第一金属层之中。

4.本发明的实施例提出一种内嵌式触控显示面板,具有显示区域与非显示区域。在面板中,多条栅极线与多条数据线彼此交叉形成于基板上。多条感测线形成于基板上。多个像素区域形成于栅极线与数据线彼此交叉处,其中每个像素区域具有像素结构,像素结构具有像素电极,且像素电极是由第一透明导电层所形成。触控电极是由第二透明导电层所形成,其中触控电极对应多个像素电极。薄膜晶体管形成于像素结构内,薄膜晶体管包含栅极、源极、漏极及半导体层,且源极电性连接数据线,栅极电性连接至栅极线,像素电极电性连接至漏极。第一绝缘层形成于感测线之上并具有第一开口以暴露其中一条感测线,栅极形成于第一绝缘层之上。第二绝缘层形成于栅极线之上并具有第二开口以对应至第一开口,其中源极形成于第二绝缘层之上。第三绝缘层形成于源极之上并具有第三开口以对应至第二开口,触控电极形成于第三绝缘层之上,触控电极通过第三开口、第二开口与第一开口以电性连接至感测线。

5.在一些实施例中,第一绝缘层与第二绝缘层具有相同的材料,第一绝缘层在第一开口内具有第一侧面,第二绝缘层在第二开口内有第二侧面,并且第一侧面与第二侧面形成顺向坡。

6.在一些实施例中,面板还具有金属连接结构,此金属连接结构与数据线具有相同的材料,金属连接结构形成于触控电极与感测线之间。

7.在一些实施例中,第一绝缘层的蚀刻速率比第二绝缘层的蚀刻速率慢。

8.在一些实施例中,内嵌式触控显示面板在非显示区域还包括多个显示垫与多个触控垫。每条数据线电性连接其中一个显示垫,每条感测线电性连接触控垫的其中一个。其中一个显示垫在两个触控垫之间,其中一个触控垫设置于两个显示垫之间。

9.在一些实施例中,触控垫的数量少于显示垫的数量,显示垫与触控垫排列为多个行,触控垫仅配置在其中一行。

10.在一些实施例中,显示垫与触控垫排列为多个行,在第一行仅具有部分的显示垫,第二行具有部分的显示垫与部分的触控垫。

11.在一些实施例中,显示垫与触控垫排列为多个行,在其中一行内任意两个触控垫之间设置相同数量的显示垫。

12.在一些实施例中,非显示区包括信号线转接区与走线区,在显示区中感测线形成在第一金属层中,在信号线转接区中感测线或数据线通过连接结构转换至另一金属层。

13.在一些实施例中,其中一条感测线包括第一部分与第二部分。第一部分形成于第一金属层。第一绝缘层具有第四开口以暴露出第一部分,第二绝缘层具有第五开口以对应至第四开口,第二部分形成于第三金属层并在第二绝缘层之上。第三绝缘层具有第六开口与第七开口,其中第六开口对应至第四开口,第七开口暴露出第二部分。第二透明导电层通过第七开口电性连接至第二部分,并通过第四开口、第五开口与第六开口电性连接至第一部分。

14.在一些实施例中,连接结构还包括金属连接层,形成于第三金属层。此金属连接层设置于第二透明导电层与第一部分之间。

15.与现有技术相比,本发明具有如下有益效果:本发明的内嵌式触控显示面板,其触控电极可以作为共同电极使用,而感测线是形成在第一金属层之中,可以避免下切(under cut)的现象。

16.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附附图作详细说明如下。

附图说明

17.图1是根据一实施例绘示显示面板中数据线与感测线的连接示意图。

18.图2是根据一实施例绘示感测线与驱动电路的连接示意图。

19.图3a至图3f是根据一些实施例绘示驱动电路上显示垫与触控垫的配置示意图。

20.图4是根据一实施例绘示像素结构的俯视图。

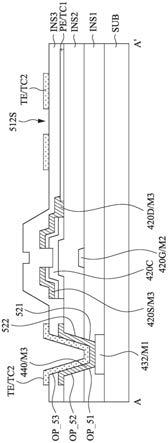

21.图5是沿着图4的剖面线aa’绘示像素结构的剖面图。

22.图6是根据一实施例绘示连接结构450的剖面图。

23.图7是根据一实施例绘示连接结构450的剖面图。

24.主要附图标记说明:

25.sub-基板,ins1-第一绝缘层,ins2-第二绝缘层,ins3-第三绝缘层,pe-像素电极,tc1-第一透明导电层,tc2-第二透明导电层,te-触控电极,420c-通道层,420g-闸极,420s-源极,420d-漏极,m1-第一金属层,m2-第二金属层,m3-第三金属层,op_51,op_52,op_53-开口,432-感测线,440-金属连接结构,512s:间隙,521-第一侧面,522-第二侧面,aa

’-

剖面线。

具体实施方式

26.关于本文中所使用的“第一”、“第二”等,并非特别指次序或顺位的意思,其仅为了区别以相同技术用语描述的元件或操作。

27.图1是根据一实施例绘示显示面板中数据线与感测线的连接示意图。请参照图1,显示面板100是一种内嵌式(in-cell)的显示面板,也就是说侦测触控用的电极是设置在薄膜晶体管基板上的像素结构之中。

28.显示面板100包括显示区域101与非显示区域102。非显示区域102包括了信号线转接区103与走线区104。在此先说明显示区域101,显示区域101内包括多个像素区域,这些像素区域形成于栅极线与数据线彼此交叉处,每一个像素区域具有一个像素结构。具体来说,显示区域101中包括多个像素结构p11~p14、p21~p24、p31~p34、p41~p44;多条沿着x方向(也称第一方向)延伸的栅极线g1~g4;多条沿着y方向(也称第二方向)延伸的数据线d1~d4,这些数据线d1~d4在空间上彼此不相交;以及多条沿着y方向延伸的感测线s1~s4。数据线d1~d4与栅极线g1~g4是交错在基板上,在交叉处具有对应的像素结构。每个像素结构中都具有一个薄膜晶体管,每条数据线d1~d4会连接至对应像素结构中薄膜晶体管的源极,并且每条栅极线g1~g4会连接至对应像素结构中薄膜晶体管的栅极。举例来说,像素结构p11具有薄膜晶体管t1,薄膜晶体管t1具有栅极t1g与源极t1s,栅极线g1是连接栅极t1g,而数据线d1是连接至源极t1s。显示面板中还包括共同电极,此共同电极在显示区域101被分割成多个触控电极c11、c12、c21、c22,且每一个触控电极对应多个像素电极且电性连接至至少一条感测线。举例来说,像素结构p11~p14对应至触控电极c11,且触控电极c11连接至感测线s1;像素结构p21~p24对应至触控电极c12,且触控电极c12连接至感测线s3;像素结构p31~p34对应至触控电极c21,且触控电极c21连接至感测线s2;像素结构p44~p44对应至触控电极c22,且触控电极c22连接至感测线s4。

29.一个帧(frame)的期间可至少被分为显示期间与触控期间。在显示期间,触控电极c11、c12、c21、c22会电性连接至共同电压,栅极线g1~g4上的电压是用以依序导通像素结构中的薄膜晶体管,驱动电路110会将像素数据通过数据线d1~d4传送至像素结构中的像素电极,借此决定对应像素的灰阶值。另一方面,而在触控期间,触控电极c11、c12、c21、c22是用以侦测显示面板100上的触控操作,驱动电路110会根据触控电极c11、c12、c21、c22上的电压产生触控感测信号。换言之,触控操作的解析度是由触控电极的数量来决定,而触控操作的解析度会低于显示的解析度。

30.信号线转接区103位于显示区域101与走线区104之间。在信号线转接区103中,数据线d1~d4与感测线s1~s4可转接至不同的金属层。例如,感测线s1~s4可以在显示区域101中属于第一金属层,但在走线区104中属于第三金属层,因此信号线转接区103中具有连接结构以将感测线s1~s4从第一金属层转接至第三金属层,以下会再详细说明连接结构的实施例。此外,在信号线转接区103中也可以设置透明或不透明的导电层,借此避免静电放电对显示面板100的损坏。

31.在走线区104中显示面板100上设置有多个显示垫121~124与多个触控垫131~134,驱动电路110电性连接至这些显示垫121~124与触控垫131~134。显示垫121~124是分别电性连接至数据线d1~d4,而触控垫131~134是分别电性连接至感测线s1~s4。特别的是,在x方向上,其中一个显示垫是设置在两个触控垫之间,而其中一个触控垫是设置于两个显示垫之间。例如,显示垫122是设置于触控垫131与触控垫132之间,且触控垫131是设置于显示垫121与显示垫122之间。在图1的实施例中,显示垫121~124与触控垫131~134是交错地设置。在现有技术中,驱动电路110是连续地配置显示垫121~124,然后再连续地配置触控垫131~134,这使得信号线d1~d4与感测线s1~s4在走线区104中会彼此交错。然而,在此实施例中由于显示垫121~124与触控垫131~134是彼此交错地设置,这使得数据线d1~d4与感测线s1~s4在显示区域101内是彼此平行,并且在非显示区域102内彼此不重

叠。

32.在一些实施例中,驱动电路110可设置在可挠式(flexible)电路板上,例如在卷带承载封装(tape carrier package,tcp)或晶粒软模封装(chip on film,cof)上,或者驱动电路110也可以设置在薄膜晶体管基板上。此外,驱动电路110可以是触控与显示整合(touch and display driver integration,tddi)单一芯片,同时提供显示与触控的功能。或者,驱动电路110中也可以包括多个芯片,分别提供显示与触控的功能。驱动电路110也可以是面板内栅极驱动器(gate-driver in plane,gip)或整合栅极驱动器(integrated gate driver,igd)。另外,驱动电路110的数量也可以大于一个,分别设置在面板的上下或左右两侧,或者也可以只设置在面板的一侧。

33.在图1中是每四个像素结构会共用一个触控电极,但在其他实施例中也可以由更多或更少个像素结构来共同一个触控电极。此外,在图1中数据线d1~d4与感测线s1~s4的数量是相同。然而,在一般情况下每个像素结构(也称为子像素)只会显示单一个颜色,而三个子像素才会构成一个像素,这三个子像素通常是沿着x方向排列,因此像素结构在x方向上的解析度会大于在y方向上的解析度。在一些实施例中,可以将至少两条感测线彼此连接后通过导线电性连接驱动电路110上其中一个触控垫。举例来说,请参照图2,图2是根据一实施例绘示感测线与驱动电路的连接示意图。为了简化起见,在图2中并未绘示出数据线、栅极线等导线。在图2的实施例中,触控电极c11、c21、c31中各有27个像素结构(共有3行(row)与9列(column))。感测线s1~s3中的至少一条感测线电性连接至触控电极c11,并且感测线s1~s3在信号线转接区103中彼此连接后通过导线201连接至驱动电路110上的触控垫。感测线s4~s6中的至少一条感测线电性连接至触控电极c21,并且感测线s4~s6在信号线转接区103中彼此连接后通过导线202连接至驱动电路110上的触控垫。感测线s7~s9中的至少一条感测线电性连接至触控电极c31,并且感测线s7~s9在信号线转接区103中彼此连接后通过导线203连接至驱动电路110上的触控垫。在图2的实施例中,感测线s1~s3中有两条感测线电性连接至触控电极c11,感测线s4~s6中有一条感测线电性连接至触控电极c21,而感测线s7~s9中有三条感测线电性连接至触控电极c31。本发明并不限制每个触控电极会电性连接至几条感测线。例如,若有五条感测线通过一个触控电极,则此触控电极可以电性连接至这五条感测线中任意数量的感测线。

34.此外,每个像素结构都具有一条数据线,而每一条数据线都会连接至驱动电路110上的一个显示垫。也就是说,显示垫的数量会多于触控垫的数量。在图2的实施例中,每3个显示垫之间都会设置一个触控垫,借此在非显示区域102中感测线与数据线不会彼此重叠。

35.图3a至图3f是根据一些实施例绘示驱动电路上显示垫与触控垫的配置示意图。为了简化起见,在图3a至图3f中并未绘示数据线与感测线。

36.请先参照图3a,在一些实施例中,显示垫与触控垫沿着y方向排列为第一行301、第二行302与第三行303。其中在第一行301中仅具有触控垫tp,而在第二行302与第三行303仅具有显示垫dp。在此实施例中,所有的触控垫都设置在第一行301,但在其他的实施例中也可以将所有的触控垫排列为多个行。此外,在图3a中,触控垫tp是设置上面,即触控垫tp是设置在显示区域与显示垫dp之间。图3b类似于图3a,显示垫与触控垫沿着y方向排列为第一行311、第二行312与第三行313。其中在第二行312与第三行313仅具有显示垫dp,在第一行311中仅具有触控垫tp。然而,在图3b中,触控垫tp是设置在下方,即显示垫dp是设置在显示

区域与触控垫tp之间。

37.在图3c中,显示垫与触控垫沿着y方向排列为第一行321与第二行322。其中第一行321仅具有部分的显示垫dp,而第二行322具有部分的显示垫dp与触控垫tp。第一行321是设置在上方,即第一行321是设置在显示区域与第二行322之间。图3d类似于图3c,不同的是,在图3d中参杂有触控垫tp与显示垫dp的第二行332是设置在上方,即第二行332是设置在显示区域与第一行331之间。

38.在图3e中,显示垫与触控垫沿着y方向排列为第一行341、第二行342、第三行343与第四行344。其中第一行341仅具有触控垫tp,而第二行342、第三行343与第四行344仅具有显示垫dp。此外,在y方向上触控垫tp与显示垫dp是彼此重叠。

39.在图3f中,触控垫tp是平均地分散在第一行351、第二行352与第三行353上。在同一行中相邻的两个触控垫tp之间则相隔有三个显示垫dp,换言之任意两个触控垫tp之间设置相同数量的显示垫dp。在y方向上触控垫tp不会彼此重叠。

40.在上述图3a至图3f的实施例中,触控垫tp在x方向上的宽度是相同于显示垫dp在x方向上的宽度。但在其他实施例中,触控垫tp在x方向上的宽度也可以大于显示垫dp在x方向上的宽度,本发明并不在此限。值得一提的是,本文中所指的“在x方向上,其中一个显示垫是设置在两个触控垫之间,而其中一个触控垫是设置于两个显示垫之间”涵盖了图3a至图3f的实施例。例如,在图3e中显示垫347在x方向上是位于触控垫345与触控垫346之间,而触控垫346是位于显示垫347与显示垫348之间。以另一个角度来说,显示垫347在x轴上的投影会位于触控垫345与触控垫346在x轴上的两个投影之间,且触控垫346在x轴上的投影是位于显示垫347与显示垫348在x轴上的两个投影之间。对于图3a至图3d与图3f的解读也可以此类推,并不再赘述。

41.图4是根据一实施例绘示像素结构的俯视图,图5是沿着图4的剖面线aa’绘示像素结构的剖面图。请参照图4,在此以像素结构410为例,像素结构410中具有薄膜晶体管420、像素电极pe与共同电极(未绘示)。薄膜晶体管420具有栅极420g、源极420s与漏极420d。属于第二金属层m2的栅极线430是连接至栅极420g。属于第三金属层m3的数据线431连接至源极420s。此外,感测线432属于第一金属层m1,感测线432用以通过孔洞连接至共同电极(即触控电极)。在此实施例中感测线432是设置在数据线431的左侧,但在一些实施例中感测线432也可以设置在数据线431的右侧。

42.请同时参照图4与图5,第一金属层m1是形成在基板sub之上,并且第一金属层m1包括感测线432。第一绝缘层ins1是形成在第一金属层m1之上,第一绝缘层ins1具有开口op_51以暴露感测器432。第二金属层m2形成在第一绝缘层ins1之上,第二金属层m2具有栅极420g。第二绝缘层ins2形成在第二金属层m2之上,第二绝缘层ins2具有开口op_52以对应开口op_51。第一透明导电层tc1形成在第二绝缘层ins2之上,第一透明导电层tc1包括像素电极pe。半导体层420c形成在第二绝缘层ins2之上以作为薄膜晶体管的通道,半导体层420c上具有欧姆接触层。第三金属层m3形成在半导体层420c之上,第三金属层m3具有源极420s、漏极420d与金属连接结构440,其中金属连接结构440通过开口op_52与开口op_51电性连接至感测线432,而漏极420d则接触像素电极pe。第三绝缘层ins3形成在第三金属层m3之上,第三绝缘层ins3具有开口op_53以对应至开口op_52。第二透明导电层tc2形成在第三绝缘层ins3之上,第二透明导电层tc2具有触控电极(即共同电极)te,触控电极te通过开口op_

53、op_52、op_51电性连接至感测线432。在此实施例中触控电极te也包括间隙(slit)512s。

43.在显示期间,触控电极te上会施加共同电压,而触控电极te与像素电极pe之间的电场可用来控制液晶的旋转方向。在触控期间,触控电极te上的电压可通过感测线432传送至驱动电路,进而产生触控感测信号。在图5的实施例中触控电极te是在像素电极pe的上面,然而在其他实施例中触控电极te也可以设置在像素电极pe的下面。

44.在一些实施例中,第一绝缘层ins1与第二绝缘层ins2具有相同的材料,两者是以相同的工艺(包含压力、温度、形成时间等)来形成,因此两者的蚀刻速率相同。在蚀刻第一绝缘层ins1与第二绝缘层ins2以分别形成开口op_52与开口op_51以后,第一绝缘层ins1在开口op_51内具有第一侧面511,第二绝缘层ins2在开口op_52内具有第二侧面522,并且第一侧面511与第二侧面522形成顺向坡。

45.在一些实施例中,第一绝缘层ins1与第二绝缘层ins2具有相同的材料,但两者的工艺不相同,通过调整工艺(例如温度、压力以及/或者形成时间),使得第一绝缘层ins1的蚀刻速率比第二绝缘层ins2的蚀刻速率慢,如此一来不会在第一绝缘层ins1的侧面形成下切(under cut)的现象。另一方面,金属连接结构440形成于触控电极te与感测线432之间,这可以避免因为太深的孔洞使得触控电极te形成断线。

46.请参照图4,在信号线转接区103中还设置了连接结构450以将感测线432转换至另一金属层。在此实施例中感测线432包括第一部分461与第二部分462,其中第一部分461是属于第一金属层m1,但第二部分462是属于第三金属层m3,换言之连接结构450是用以将感测线432转换至第三金属层m3。在其他实施例中连接结构450也可以将感测线432转换至第二金属层m2。在一些实施例中也可以不设置连接结构450,让感测线432维持在第一金属层m1。在一些实施例中也可以在数据线431上设置连接结构以将数据线431转换至第一金属层m1或是第二金属层m2。在一些实施例中,相邻的两条数据线431中,其中一条数据线上设置了连接结构以转换至第二金属层m2,另一条数据线上则没有设置连接结构,如此一来在走线区104这两条数据线便不会彼此接触。图6是根据一实施例绘示连接结构450的剖面图。请参照图6,第一部分461形成在基板sub之上。第一绝缘层ins1具有开口op_64以暴露出第一部分461。第二绝缘层ins2具有开口op_65以对应至开口op_64。第二部分462形成在第二绝缘层ins2之上。第三绝缘层ins3具有开口op_66与开口op_67,其中开口op_66对应至开口op_65与开口op_64,开口op_67暴露出第二部分462。第二透明导电层tc2通过开口op_67电性连接至第二部分462,并通过开口op_66、开口op_65与开口op_64电性连接至第一部分461。图6的连接结构也可以设置在数据线上以将数据线从第三金属层转换至第一金属层。

47.图7是根据一实施例绘示连接结构450的剖面图。图7与图6的不同之处在于多设置了形成于第三金属层m3的金属连接层710,此金属连接层710设置于第二透明导电层tc2与第一部分461之间并与这两者直接接触。设置金属连接层710的目的在于避免开口op_66、开口op_65与开口op_64形成太深的凹槽,导致第二透明导电层tc2断线。

48.上述基板sub的材料例如包括玻璃、聚合物(polymer)、聚对苯二甲酸乙二酯(polyethylene terephthalate,pet)、聚碳酸酯(polycarbonate,pc)、聚醚砜(polyether sulfone,pes)、三醋酸纤维素(triacetyl cellulose,tac)、聚甲基丙烯酸甲酯(pmma)、聚乙烯(polyethylene)、环烯烃聚合物(cop)、聚亚酰胺(polyimide,pi),以及聚碳酸酯(pc)与聚甲基丙烯酸甲酯(pmma)构成的复合材料等等,本发明并不在此限。第一透明导电层tc1

与第二透明导电层tc2的材料可包括氧化铟锡(indium tin oxide,ito)、氧化铟锌(indium zinc oxide,izo)、氧化鍗锡(antimony tin oxide,ato)、氧化氟锡(fluorine tin oxide,fto)或其他导电且透明的材料。在本说明书中提到的金属层可为铝、铜、钛、钨等单一金属层或者是钼/铝/钼、钛/铝钛、钛/铜/钛、钛/铜

…

等复合金属层,本发明并不在此限。另一方面,在本说明书中提到的绝缘层可以为氮化硅、氧化硅、氮氧化硅或其他合适的绝缘层,并且在图示中的一层绝缘层可以包含两层以上材料不同且彼此堆叠的绝缘层。

49.虽然本发明已经以实施例公开如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许变动与润饰,所以本发明的保护范围当视权利要求所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1