一种三模冗余计算机软件数据同步方法与流程

1.本发明涉及数据处理技术领域,尤其涉及一种三模冗余计算机软件数据同步方法。

背景技术:

2.目前三模冗余系统是航天设备中常用的一种容错设计技术,三个模块运行同一份软件、执行相同的操作,以多数相同的输出作为表决系统的正确输出,三个模块中只要不同时出现两个相同的错误,就能掩蔽掉故障模块的错误,保证系统正确的输出。由于三个模块是互相独立的,两个模块同时出现错误是极小概率事件,故可以大大提高系统的可信性,在航天领域以及一些需要高可靠的环境应用较多。

3.三模冗余计算机表决的基础需要:1.参与计算的数据一致2.运行步调一致,即同时输出结果或控制命令。为保证三模冗余计算机输入数据一致,运行步调一致,通常采用发送给冗余模块的数据一致,保证参与计算的数据一致,如:1.将三模冗余计算机的3个模块接在同一个总线上如(mil-std-1553b总线、实时以太网);2.在三模冗余计算机上加一个高可靠设备(如质量等级高的宇航级芯片)采集数据,然后同时将数据分发给3个模块;3.三模冗余软件每个运行周期接收到同一个中断后进行数据读取后执行计算和结果输出,保证三模冗余软件运行步调一致。

4.然而,将三模冗余计算机的3个模块接在同一个总线上,虽然能三模冗余计算机保证输入一致,但是当三模冗余计算机其中一个模块输入存在故障时,由于三模冗余计算机读取到的数据未互相分发确认,则无法保证三冗余模块参与计算数据一致;通过高可靠设备获取数据分发给三模冗余软件进行数据同步的方法,需要额外的硬件设备支持,同时高可靠设备对于冗余系统是一个单点,降低了整个冗余系统的可靠性。

技术实现要素:

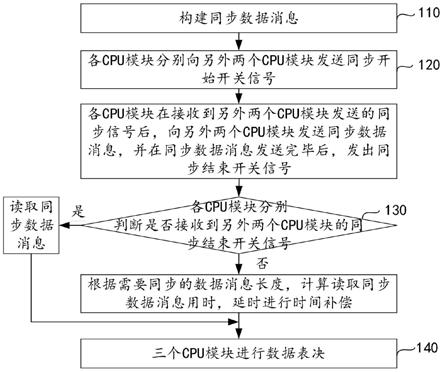

5.本发明提供了一种三模冗余计算机软件数据同步方法,所述方法用于协调三模冗余计算机三个cpu模块的数据同步,所述方法具体包括:

6.构建同步数据消息;

7.各cpu模块分别向另外两个cpu模块发送同步开始开关信号;

8.各cpu模块在接收到另外两个cpu模块发送的同步信号后,向另外两个cpu模块发送同步数据消息,并在同步数据消息发送完毕后,发出同步结束开关信号;

9.各cpu模块分别判断是否接收到另外两个cpu模块的同步结束开关信号,若收到同步结束开关信号,则读取同步数据消息,若未接收到同步结束开关信号,则根据需要同步的数据消息长度,计算读取同步数据消息用时,延时进行时间补偿;

10.三个cpu模块进行数据表决。

11.如上所述的一种三模冗余计算机软件数据同步方法,其中,在冗余数据交互时刻,无论是否存在有效数据,均对数据进行交互;若存在有效数据,则将数据有效标志设置为有

效,并根据本执行周期发送的同步消息次数设置同步数据消息序号,并计算同步消息内容crc值,填入同步数据消息中。

12.如上所述的一种三模冗余计算机软件数据同步方法,其中,同步数据消息包括同步数据格式、同步数据区、数据有效标志、同步数据消息序号和数据crc校验值。

13.如上所述的一种三模冗余计算机软件数据同步方法,其中,三模冗余计算机三个cpu模块之间有两两互联的开关,cpu1通过互联开关向cpu2和cpu3发送同步开始开关信号、cpu2通过互联开关向cpu1和cpu3发送同步开始开关信号、cpu3通过互联开关向cpu1和cpu2发送同步开始开关信号。

14.如上所述的一种三模冗余计算机软件数据同步方法,其中,cpu1接收到cpu2和cpu3发送的同步结束开关信号后,向cpu2和cpu3发送同步结束开关信号;cpu2接收到cpu1和cpu3发送的同步结束开关信号后,向cpu1和cpu3发送同步结束开关信号;cpu3接收到cpu1和cpu2发送的同步结束开关信号后,向cpu1和cpu2发送同步结束开关信号。

15.如上所述的一种三模冗余计算机软件数据同步方法,其中,若cpu1接收到cpu2和cpu3的同步结束开关信号,则cpu1读取cpu2和cpu3的同步消息数据;若cpu2接收到cpu1和cpu3的同步结束开关信号,则cpu2读取cpu1和cpu3的同步消息数据;若cpu3接收到cpu1和cpu2的同步结束开关信号,则cpu3读取cpu1和cpu2的同步消息数据。

16.如上所述的一种三模冗余计算机软件数据同步方法,其中,所述方法还包括:在读取同步数据后,判断数据crc校验值、数据有效标识和同步消息序列是否正确。

17.如上所述的一种三模冗余计算机软件数据同步方法,其中,三个cpu模块进行数据表决,具体包括:若cpu1、cpu2和cpu3的同步消息数据中均存在有效数据,则进行三取二表决,选用至少两个模块一直的数据用于后续计算;若三个模块数据均不一致,则优先使用cpu1数据用于之后计算。

18.本发明还提供一种计算机可读存储介质,所述计算机存储介质中包含一个或多个程序指令,所述一个或多个程序指令用于被处理器执行上述任一项所述的一种三模冗余计算机软件数据同步方法。

19.本发明实现的有益效果如下:采用本技术提出的三模冗余计算机软件数据同步方式,每次同步数据在三模冗余计算机3个cpu上同时进行分发处理以及表决,保证参与计算的数据一致;同时保证同步过程中发生异常导致程序执行分支不同情况下,三模冗余计算机软件数据同步用时一致,三模冗余软件运行步调一致。

附图说明

20.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明中记载的一些实施例,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的附图。

21.图1是本发明实施例一提供的一种三模冗余计算机软件数据同步方法流程图;

22.图2是三冗余计算机数据通道关系图。

具体实施方式

23.下面结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

24.实施例一

25.如图1所示,本发明实施例一提供一种三模冗余计算机软件数据同步方法,用于协调三个cpu模块的数据同步,实现三个cpu模块数据的实时同步,保证了参与计算数据的一致性,并且保证在正常和异常情况下,即使三模软件在数据同步时执行分支不一致、执行时间不一致,通过时间补偿方式,也能够保证在各种模式下三模冗余计算机软件执行时间一致。

26.所述三模冗余计算机软件数据同步方法具体包括:

27.步骤110、构建同步数据消息;

28.为保证三模冗余计算机软件执行步调一致,即同一时间执行相同功能,在冗余数据交互时刻,无论是否存在有效数据,均对数据进行交互。若存在有效数据,则将数据有效标志设置为有效,并根据本执行周期发送的同步消息次数设置同步数据消息序号,并针对数据分发中可能出现的误码,添加的crc(循环冗余校验),保证数据的完整性和正确性,计算出同步消息内容crc值填入同步消息数据中。

29.同步数据消息格式如表1所示:

30.表1同步数据消息格式

[0031][0032]

步骤120、各cpu模块分别向另外两个cpu模块发送同步开始开关信号;

[0033]

为保证三模软件数据同步的实时性,三模冗余计算机三个模块之间有两两互联的开关,采用三机互联开关进行握手,保证三模冗余计算机软件握手后时间差小于1us;如图2所示,cpu1可以通过互联开关向cpu2/3发送开关信号、cpu2可以通过互联开关向cpu1/3发送开关信号、cpu3可以通过互联开关向cpu1/2发送开关信号。

[0034]

步骤130、各cpu模块在接收到另外两个cpu模块发送的同步信号后,向另外两个cpu模块发送同步数据消息,并在同步数据消息发送完毕后,发出同步结束开关信号;

[0035]

三模冗余计算机软件发送完同步开关信号后,不断查询接收到的同步信号,查询到另外两个模块同步信号后发送同步数据,在数据发送完毕后,向另外两个模块发送同步结束开关信号,即cpu1向cpu2/3发送同步结束开关信号、cpu2向cpu1/3发送同步结束开关信号、cpu3向cpu1/2发送同步结束开关信号。

[0036]

步骤150、各cpu模块分别判断是否接收到另外两个cpu模块的同步结束开关信号,若收到同步结束开关信号,则读取同步数据消息,若未接收到同步结束开关信号,则不读取同步数据,根据需要同步的数据长度,计算读取同步数据用时,延时进行时间补偿;

[0037]

由于三个cpu模块之间为串行处理,因此各cpu模块分别判断是否接收到另外两个cpu模块的同步结束开关信号,具体包括:

[0038]

(1)判断是否收到左侧cpu同步结束信号量,即cpu1判断是否收到cpu2同步结束信号量、cpu2判断是否收到cpu3同步结束信号量、cpu3判断是否收到cpu1同步结束信号量。

[0039]

①

若收到同步结束信号量,则读取同步消息数据(cpu1读取cpu2同步数据、cpu2读取cpu3同步数据、cpu3读取cpu1同步数据)。

[0040]

②

若未收到同步结束信号量,则不读取同步数据,根据需要同步的数据长度,计算读取同步数据用时,延时进行时间补偿。

[0041]

(二)判断是否收到右侧同步结束信号量,即cpu1判断是否收到cpu3同步结束信号量、cpu2判断是否收到cpu1同步结束信号量、cpu3判断是否收到cpu2同步结束信号量。

[0042]

①

若收到同步结束信号量,则读取同步数据(cpu1读取cpu3同步数据、cpu2读取cpu1同步数据、cpu3读取cpu2同步数据)。

[0043]

②

若未收到同步结束信号量,则不读取同步数据,根据需要同步的数据长度,计算读取同步数据用时,延时进行时间补偿。

[0044]

针对数据分发中可能出现的异常,针对不同执行分支添加了执行时间约束和时间补偿,使三模冗余计算机软件执行数据同步耗时一致,误差小于10us,保证三模冗余计算机软件执行的步调一致。

[0045]

本步骤还包括:在读取同步数据后,判断数据crc校验值、数据有效标识和同步消息序列是否正确。

[0046]

步骤160、三个cpu模块进行数据表决;

[0047]

三个cpu模块进行数据表决,具体包括:若cpu1、cpu2和cpu3的同步消息数据中均存在有效数据,则进行三取二表决,选用至少两个模块一直的数据用于后续计算;若三个模块数据均不一致,则优先使用cpu1数据用于之后计算。通过数据表决,在发生单一数据异常情况下,三模表决后数据一致,保证了参与计算数据一致。

[0048]

与上述实施例对应的,本发明实施例提供一种计算机可读存储介质,计算机存储介质中包含一个或多个程序指令,一个或多个程序指令用于被处理器执行一种三模冗余计算机软件数据同步方法。

[0049]

本发明所公开的实施例提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序指令,当所述计算机程序指令在计算机上运行时,使得计算机执行上述的一种三模冗余计算机软件数据同步方法。

[0050]

在本发明实施例中,处理器可以是一种集成电路芯片,具有信号的处理能力。处理器可以是通用处理器、数字信号处理器(digital signal processor,简称dsp)、专用集成电路(application specific工ntegrated circuit,简称asic)、现场可编程门阵列(fieldprogrammable gate array,简称fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件。

[0051]

可以实现或者执行本发明实施例中的公开的各方法、步骤及逻辑框图。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等。结合本发明实施例所公开的方法的步骤可以直接体现为硬件译码处理器执行完成,或者用译码处理器中的硬件及软件模块组合执行完成。软件模块可以位于随机存储器,闪存、只读存储器,可编程只读存储

器或者电可擦写可编程存储器、寄存器等本领域成熟的存储介质中。处理器读取存储介质中的信息,结合其硬件完成上述方法的步骤。

[0052]

存储介质可以是存储器,例如可以是易失性存储器或非易失性存储器,或可包括易失性和非易失性存储器两者。

[0053]

其中,非易失性存储器可以是只读存储器(read-only memory,简称rom)、可编程只读存储器(programmable rom,简称prom)、可擦除可编程只读存储器(erasable prom,简称eprom)、电可擦除可编程只读存储器(electrically eprom,简称eeprom)或闪存。

[0054]

易失性存储器可以是随机存取存储器(random access memory,简称ram),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的ram可用,例如静态随机存取存储器(static ram,简称sram)、动态随机存取存储器(dynamic ram,简称dram)、同步动态随机存取存储器(synchronous dram,简称sdram)、双倍数据速率同步动态随机存取存储器(double data ratesdram,简称ddrsdram)、增强型同步动态随机存取存储器(enhancedsdram,简称esdram)、同步连接动态随机存取存储器(synchlink dram,简称sldram)和直接内存总线随机存取存储器(directrambus ram,简称drram)。

[0055]

本发明实施例描述的存储介质旨在包括但不限于这些和任意其它适合类型的存储器。

[0056]

本领域技术人员应该可以意识到,在上述一个或多个示例中,本发明所描述的功能可以用硬件与软件组合来实现。当应用软件时,可以将相应功能存储在计算机可读介质中或者作为计算机可读介质上的一个或多个指令或代码进行传输。计算机可读介质包括计算机存储介质和通信介质,其中通信介质包括便于从一个地方向另一个地方传送计算机程序的任何介质。存储介质可以是通用或专用计算机能够存取的任何可用介质。

[0057]

以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的技术方案的基础之上,所做的任何修改、等同替换、改进等,均应包括在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1