一种基于PCIE标准接口互连的chiplet芯粒及接口复用方法与流程

一种基于pcie标准接口互连的chiplet芯粒及接口复用方法

技术领域

1.本发明涉及一种基于pcie标准接口互连的chiplet芯粒及接口复用方法,属于集成电路芯片技术领域。

背景技术:

2.目前芯粒(die)间直连技术主要有:(1)intel(英特尔)基于硅基板的chiplet技术,即通过专门的“互连die”——硅基板进行互连,在引出bump到封装基板(package substrate)上,从而实现将多个不同类型不同工艺的die封装在一个芯片中。由于传输介质相同、传输距离极短,基于硅基板的die间互连最有可能达到超低延迟、超高带宽的性能需求,但对工艺也有极高的要求。

3.②

定制serdes(串行器): infinity fabric(if)是amd cpu采用的一种通用互连架构,在串行互连方面由两种定制serdes实现,一种为用于封装内部die间直连的ifop(if on-package)serdes,另一种是用于片间直连的ifis(if inter-socket)serdes。由于传输介质和传输距离不同,两种定制serdes采用不同的传输方式、设计方法,以达到最优的性能与最低的功耗。

4.intel的基于硅基板的die间互连技术虽然有超低延迟、超高宽带的性能,但对工艺有极高要求。而定制serdes可以根据不同层次、不同介质、不同距离的互连需求,定制不同的传输协议、实现方式,以达到最优的性价比、能耗比。但对工艺、设计能力、成本等均有极高的要求,这两种方式,都对芯片的设计水平和制造工艺有极高要求,尤其是基于当前的国产工艺条件下,均很难实现。

技术实现要素:

5.本发明的目的在于提供一种基于pcie标准接口互连的chiplet芯粒及接口复用方法,实现了pcie标准接口和芯粒互连接口的复用,解决了单独的io与直连接口占用芯片面积大、高速引脚多、成本高的问题。

6.一种基于pcie标准接口互连的chiplet芯粒,包括:至少一个die芯粒,所述die芯粒之间通过pcie接口实现多个die芯粒直连接;所述die芯粒包括中心模块、选择模块、piu模块、ciu模块和rc模块,所述选择模块用于对中心模块发送的head包和data包或者接收rc模块的head包和data包,选择物理链路由ciu模块使用或由piu模块使用,所述rc模块用于将head包和data包打包成协议包,或者将协议包分离出head包和data包,所述rc模块通过pcie phy实现与外部设备或者die芯粒接收或者发送,其中所述选择模块选择ciu模块时, head包与data包作为一个整体放入data’包中,通过rc模块按照pcie包格式要求与其它die芯粒通信,实现pcie接口复用。

7.进一步地,所述die芯粒包括四个8x的pcie4.0接口。

8.进一步地,所述pcie4.0接口的四个通路均为复用通路。

9.进一步地,所述选择模块选择piu模块时,将head包组成head’包,data包组成

data’包,发送至rc模块转换成pice协议包通过pcie接口与外部设备通信。

10.进一步地,所述选择模块选择ciu模块时,die芯粒之间直连,ciu模块将head包和data包作为一个整体放入data’包中,发送至rc模块转换成pice协议包通过pcie接口发送与其直连的die芯粒。

11.进一步地,所述die芯粒通过pcie接口直连行成单die、2-die,3-die、4-die多种芯粒形态。

12.一种基于pcie标准接口互连的chiplet芯粒接口复用方法,所述方法包括:与外部设备连接时,选择模块将中心模块发送的head包和data包或者接收rc模块的head包和data包通过piu模块转换符合rc模块协议要求,rc模块及pcie phy根据pcie接口协议,将从piu模块收到的包组成pice协议包发送至外部设备,进行高速通信;与die芯粒直连时,选择模块将中心模块发送的head包和data包通过ciu模块打包成一个整体data’包,并按照pcie协议包格式发送至rc模块,rc模块及pcie phy根据pcie接口协议与die芯粒对应的pcie接口连接,进行高速通信。

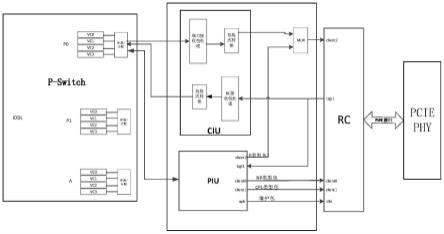

13.进一步地,所述方法还包括:待接收die芯粒通过rc模块分离出head’包和data’包,发送至ciu模块,然后根据head’包从data’包中解析出head包和data包交给中心模块。

14.与现有技术相比,本发明所达到的有益效果:本发明通过复用pcie接口物理通路、分别处理传输层协议包的方法,只占用一组芯片高速引脚即可实现通用io接口和die芯粒间直连接口两种功能,大大节省了面积和成本,同时又具有相当的灵活性,不但能够支持多芯粒封装时芯粒之间通过有机基板互连,还能支持芯片间通过印制线互连,以及标准pcie设备的扩展,在提供高带宽互连的同时节省芯片引脚、降低对工艺的要求。

附图说明

15.图1是本发明4e芯片不同数量核心的多die形态示意图;图2是本发明piu和ciu模块示意图;图3是本发明pcie协议包格式示意图;图4是本发明直连传输包格式示意图;图5是本发明与外部设备通信的流程图;图6是本发明die间通信的流程图;图7是本发明与外部设备通信时各种包的转换流程图;图8是本发明die间通信时各种包的转换流程图;图9是本发明各个阶段包组成示意图。

具体实施方式

16.为使本发明实现的技术手段、创作特征、达成目的与功效易于明白了解,下面结合具体实施方式,进一步阐述本发明。

17.实施例1如图1-图6所示,公开了一种基于pcie标准接口互连的chiplet芯粒,包括:

至少一个die芯粒,所述die芯粒之间通过pcie接口实现多个die芯粒直连接;图1显示了每个die芯粒实现4个8x的pcie4.0接口,通过pcie die间直连技术形成的单die芯粒、2-die芯粒,3-die芯粒、4-die芯粒的产品形态,可覆盖不同领域的性能需求。

18.具体方案中,每个die芯粒的4个8x的pcie4.0通路均为复用通路,复用层次在tlp层(事务层),即在rc(root complex port)控制器以上。

19.本发明中主要通过piu模块和ciu模块实现上述复用功能,见图2:所述die芯粒包括中心模块、选择模块、piu模块、ciu模块和rc模块,所述选择模块用于对中心模块发送的head包和data包或者接收rc模块的head包和data包,选择物理链路由ciu模块使用或由piu模块使用,所述rc模块用于将head包和data包打包成协议包,或者将协议包分离出head包和data包,所述rc模块通过pcie phy实现与外部设备或者die芯粒接收或者发送,其中所述选择模块选择ciu模块时,head包与data包作为一个整体放入data’包中,通过rc模块按照pcie包格式要求与其它die芯粒通信,实现pcie接口复用;piu模块(pcie interface unit):作为io设备接口时处理pcie设备包,通过与交叉开关通信,完成设备的io、dma(直接存储器访问)、中断包在pcie协议与核心协议之间的转换。

20.ciu(connection interface unit)模块:作为直连接口,通过与交叉开关通信,完成自定义片间直连协议包格式与pcie协议包格式之间的转换,具体介绍:中心模块产生的包由head和data组成,piu模块/ciu模块的通路也分为head通路和data通路,与外部设备由piu完成,由于协议不同,需要将包格式重组,按照rc模块的协议要求,将head包组成head’包,data包组成data’包发给rc模块,rc模块以及pcie phy会根据pcie接口协议,将从piu模块收到的包组成pice协议包,此时可以认为head信息和data信息被打包在一起,从而发送给外部设备,进行高速通信,如图5;ciu模块需要控制管理pcie接口作为直连接口时,对包的发送与接收,具体如下:(1)、直连传输包的类型选择。对于rc模块来说,ciu只提供pcie存储器写包(mmwr)这一种包类型,即所有穿过直连接口的包类型,经过ciu后都转换成了pcie协议中的mmwr()包在pcie链路上传输。选择该种包类型的原因是mmwr包是post类型,对于发送端来说只要发送出去就算完成,不需要响应,在rc模块中没有请求悬挂、超时等逻辑,所以可以选择作为传输通道而不需要考虑对协议本身的支持。

21.(2)、直连传输包的格式。pcie的64位mmwr包格式如图3所示。将mmwr包作为直连传输包,除了4dw(double word)包头外至少带一拍128bit的数据(4dw),作为直连传输包的控制信息,真正的数据从第5个dw开始,最多128b(byte)。其中需要固定fmt[1:0]为2’b11,type[4:0]为5’b00000,address[63:0]地址信息可以固定,但与真正的空间地址无关,落在对端rc的缺省范围之外即可。length是包数据的dw长度,至少需要为4,即一拍的控制信息长度,所以若不带数据的协议包,length=4即可,带数据的协议包,length=数据dw长度+4。

[0022] ciu模块在工作时,die芯粒间直连,具体介绍:如图6,例如,由die1发送给die2,中心模块产生的包由head和data,ciu会将核心的head包和data包作为一个整体放入data’包中,作为发送给die2的数据,而发送给rc的head’包则会按照pcie包格式要求,由ciu根据数据产生控制信息交给rc,这部分控制信息是为了满足pcie协议规范要求而产生的,是传输所必要的,但对于die2的核心来说,这个

head’包是没有用的,它需要的是data包。这是与外部通信不同之处,在与外部通信中,head’包的信息也是设备所需要的信息。而当pcie的协议包达到die2对应的pcie接口后,通过rc重新解包,再分离出head’包和data’包然后交给ciu,而ciu根据head’包,从data’包中解析出head包和data包交给核心。

[0023]

实施例2 一种基于pcie标准接口互连的chiplet芯粒接口复用方法,所述方法包括:与外部设备连接时,选择模块将中心模块发送的head包和data包或者接收rc模块的head包和data包通过piu模块转换符合rc模块协议要求,rc模块及pcie phy根据pcie接口协议,将从piu模块收到的包组成pice协议包发送至外部设备,进行高速通信;与die芯粒直连时,选择模块将中心模块发送的head包和data包通过ciu模块打包成一个整体data’包,并按照pcie协议包格式发送至rc模块,rc模块及pcie phy根据pcie接口协议与die芯粒对应的pcie接口连接,进行高速通信。

[0024]

基于上述所述方法,还包括:待接收die芯粒通过rc模块分离出head’包和data’包,发送至ciu模块,然后根据head’包从data’包中解析出head包和data包交给中心模块。

[0025]

本发明通过在标准pcie接口传输层之上支持特定的直连传输协议,实现了pcie标准接口和芯粒互连接口的复用,解决了单独的io与直连接口占用芯片面积大、高速引脚多、成本高的问题。大大节省了面积和经费开销,通过复用pcie 接口,实现芯粒(die)间直连接口和pcie 高速io接口的复用,即pcie接口既可以作为高速io接口,又可以在多die形态下作为die芯粒间直连接口使用。在不增加额外芯片引脚和芯片面积的基础上,大大降低了对工艺的要求,并能支持多种封装形态。

[0026]

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明技术原理的前提下,还可以做出若干改进和变形,这些改进和变形也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1