模块边界时序约束方法及相关设备与流程

本技术涉及但不限定于一种模块边界时序约束方法及相关设备。

背景技术:

1、随着电子技术的发展,集成电路中包含晶体管的数量也逐渐庞大,已达到百亿级别。因此在芯片实现的过程中,需要将集成电路划分为多个模块进行分别设计,最终在将多模块连接构成整个芯片。

2、在芯片设计过程中,数字集成电路的时序收敛(timing closure)是保障芯片准确运行的关键,在模块设计过程中,内部逻辑电路的时序器件构建的信号传输路径是已知的,因此,模块的设计人员可对内部逻辑电路时序收敛进行准确地把控。但是,当信号传输路径进行跨模块传输时,模块的设计人员对电信号在模块外的路径传输情况是不清楚的,如何保障跨模块路径的时序收敛是芯片设计研究的重点。

3、在现有的时序约束方法中,一般通过top-down形式,在顶层确定各模块的逻辑级数,根据当前模块和相邻模块的逻辑级数进行时序约束的粗略分配,由于芯片中模块的数量较大,与当前模块关联的相邻模块的数量也很多,依照此构建的时间约束复杂,依赖于该时序约束在芯片物理实现的过程中,模块中逻辑电路的实际拓扑结构会为了满足相对于一部分相邻模块的时序约束进行调整,造成相对于其他相邻模块或者模块内部的逻辑电路的实际时延与预先分配的时序约束存在偏差,导致时序无法收敛的情况,需要在当前模块和相邻模块全部设计完成后,进行多次调整来达到时序收敛,导致时序收敛效率较低。

技术实现思路

1、本技术提供一种模块边界时序约束方法及相关设备,用以解决的芯片物理实现过程中时序收敛效率低的技术问题。

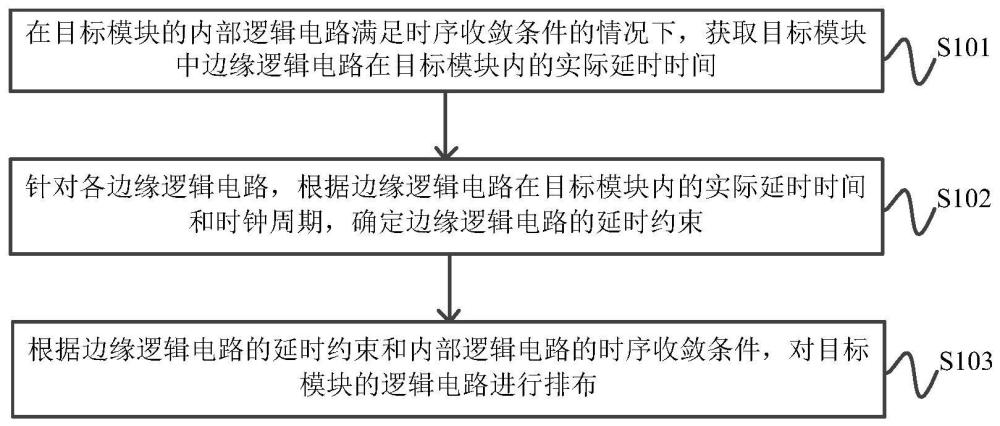

2、第一方面,本技术实施例提供一种模块边界时序约束方法,包括:

3、在目标模块的内部逻辑电路满足时序收敛条件的情况下,获取所述目标模块中边缘逻辑电路在所述目标模块内的实际延时时间;所述目标模块设有所述内部逻辑电路和至少一个所述边缘逻辑电路,各所述边缘逻辑电路包括时序器件;

4、针对各所述边缘逻辑电路,根据所述边缘逻辑电路在所述目标模块内的实际延时时间和时钟周期,确定所述边缘逻辑电路的延时约束;

5、根据所述边缘逻辑电路的延时约束和内部逻辑电路的时序收敛条件,对所述目标模块的逻辑电路进行排布。

6、在上述技术方案中,电子设备在确定目标模块的内部逻辑电路满足时序收敛的情况下,确定支持该情况的目标模块的边缘逻辑电路的实际延时时间,以此构建目标模块的边缘逻辑电路的延时约束,不再依赖于目标模块外部的其他模块的信息进行延时约束,降低了边缘逻辑路径的时间约束的复杂度,只需在此基础上进行最优化设计电路结构即可提高与目标模块的相邻模块的时延收敛的可能,在物理实现后期对全部模块进行统一测试时减少针对边缘时序收敛的修改,从而提高了时序收敛效率。

7、可选地,根据所述边缘逻辑电路在所述目标模块内的实际延时时间和时钟周期,确定所述边缘逻辑电路的延时约束,包括:

8、根据所述时钟周期和所述实际延时时间的差值,确定所述边缘逻辑电路的延时约束。

9、可选地,根据所述时钟周期和所述实际延时时间的差值,确定所述边缘逻辑电路的延时约束,包括:

10、将所述差值和预设时延余量的和作为所述边缘逻辑电路的延时约束。

11、可选地,在目标模块的内部逻辑电路满足时序收敛条件的情况下,获取所述目标模块中边缘逻辑电路在所述目标模块内的实际延时时间,包括:

12、获取各所述边缘逻辑电路的预设延时约束;

13、根据所述预设延时约束,调整各所述边缘逻辑电路的布局,以确定所述目标模块的内部逻辑电路满足时序收敛条件时,各边缘逻辑电路中时序器件至所述目标模块的边界之间路径的信号传输时间;

14、将所述信号传输时间确定为所述边缘逻辑电路的实际延时时间。

15、可选地,获取各所述边缘逻辑电路的预设延时约束,包括:

16、获取顶层内,所述目标模块和与各所述边缘逻辑电路电连接的相邻模块的逻辑级数;

17、根据所述目标模块、各所述相邻模块的逻辑级数和时钟周期,确定各所述边缘逻辑电路的预设延时约束。

18、可选地,在确定各所述边缘逻辑电路的延时约束之后,所述方法还包括:

19、获取相邻模块内边缘逻辑电路的延时约束;

20、根据所述相邻模块内边缘逻辑电路的延时约束和所述目标模块内边缘逻辑电路的延时约束,确定所述目标模块内各边缘逻辑电路的延时约束的收敛状态;

21、当所述收敛状态为不收敛时,根据所述边缘逻辑电路的延时约束和与所述边缘逻辑电路电连接的、所述相邻模块内的边缘逻辑电路的延时约束、时钟周期,对所述时钟周期和/或所述延时约束进行调整,直至所述收敛状态调整为收敛。

22、可选地,根据所述相邻模块内边缘逻辑电路的延时约束和所述目标模块内边缘逻辑电路的延时约束,确定所述目标模块内各边缘逻辑电路的延时约束的收敛状态,包括:

23、针对所述目标模块,根据各所述边缘逻辑电路的延时约束和所述内部逻辑电路的结构,构建所述目标模块的原始时序模型;

24、获取根据相邻模块内边缘逻辑电路的延时约束构建的原始时序模型;

25、根据所述目标模块的原始时序模型和所述相邻模块的原始时序模型,确定所述目标模块中边缘逻辑电路的时序器件将电信号传输至所述相邻模块中边缘逻辑电路的时序器件的延时时间,或者,确定所述相邻模块中边缘逻辑电路的时序器件将电信号传输至所述目标模块中边缘逻辑电路的时序器件的延时时间;

26、当所述延时时间大于时钟周期时,确定所述边缘逻辑电路的延时约束不收敛。

27、在上述技术方案中,在芯片物理设计前期,在利用各模块的内部逻辑电路确定各模块针对边缘逻辑电路的延时约束后,即可利用相邻的两模块中、具有电连接关系的延时约束确定信号跨模块传输时的延时时间,从而在物理实现早期确定跨模块路径的时序收敛情况,降低了后续全芯片时序分析针对时序收敛的逻辑电路修改的情况,提高了时序收敛效率。

28、第二方面,本技术提供一种模块边界时序约束装置,包括:

29、获取模块,用于在目标模块的内部逻辑电路满足时序收敛条件的情况下,获取所述目标模块中边缘逻辑电路在所述目标模块内的实际延时时间;所述目标模块设有所述内部逻辑电路和至少一个所述边缘逻辑电路,各所述边缘逻辑电路包括时序器件;

30、处理模块,用于针对各所述边缘逻辑电路,根据所述边缘逻辑电路在所述目标模块内的实际延时时间和时钟周期,确定所述边缘逻辑电路的延时约束;

31、所述处理模块还用于根据所述边缘逻辑电路的延时约束和内部逻辑电路的时序收敛条件,对所述目标模块的逻辑电路进行排布。

32、在一些实施例中,所述处理模块具体用于:

33、根据所述时钟周期和所述实际延时时间的差值,确定所述边缘逻辑电路的延时约束。

34、在一些实施例中,所述处理模块具体用于:

35、将所述差值和预设时延余量的和作为所述边缘逻辑电路的延时约束。

36、在一些实施例中,所述处理模块具体用于:

37、获取各所述边缘逻辑电路的预设延时约束;

38、根据所述预设延时约束,调整各所述边缘逻辑电路的布局,以确定所述目标模块的内部逻辑电路满足时序收敛条件时,各边缘逻辑电路中时序器件至所述目标模块的边界之间路径的信号传输时间;

39、将所述信号传输时间确定为所述边缘逻辑电路的实际延时时间。

40、在一些实施例中,所述处理模块具体用于:

41、获取顶层内,所述目标模块和与各所述边缘逻辑电路电连接的相邻模块的逻辑级数;

42、根据所述目标模块、各所述相邻模块的逻辑级数和时钟周期,确定各所述边缘逻辑电路的预设延时约束。

43、在一些实施例中,所述处理模块具体用于:

44、获取相邻模块内边缘逻辑电路的延时约束;

45、根据所述相邻模块内边缘逻辑电路的延时约束和所述目标模块内边缘逻辑电路的延时约束,确定所述目标模块内各边缘逻辑电路的延时约束的收敛状态;

46、当所述收敛状态为不收敛时,根据所述边缘逻辑电路的延时约束和与所述边缘逻辑电路电连接的、所述相邻模块内的边缘逻辑电路的延时约束、时钟周期,对所述时钟周期和/或所述延时约束进行调整,直至所述收敛状态调整为收敛。

47、在一些实施例中,所述处理模块具体用于:

48、针对所述目标模块,根据各所述边缘逻辑电路的延时约束和所述内部逻辑电路的结构,构建所述目标模块的原始时序模型;

49、获取根据相邻模块内边缘逻辑电路的延时约束构建的原始时序模型;

50、根据所述目标模块的原始时序模型和所述相邻模块的原始时序模型,确定所述目标模块中边缘逻辑电路的时序器件将电信号传输至所述相邻模块中边缘逻辑电路的时序器件的延时时间,或者,确定所述相邻模块中边缘逻辑电路的时序器件将电信号传输至所述目标模块中边缘逻辑电路的时序器件的延时时间;

51、当所述延时时间大于时钟周期时,确定所述边缘逻辑电路的延时约束不收敛。

52、第三方面,本技术提供一种电子设备,包括:处理器,以及与所述处理器通信连接的存储器;

53、所述存储器存储计算机指令;

54、所述处理器执行所述存储器存储的计算机指令,以实现第一方面涉及的方法。

55、第四方面,本技术提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机指令,所述计算机指令被处理器执行时用于实现第一方面涉及的方法。

56、本技术提供的模块边界时序约束方法及相关设备中,电子设备在确定目标模块的内部逻辑电路满足时序收敛的情况下,确定支持该情况的目标模块的边缘逻辑电路的实际延时时间,以此构建目标模块的边缘逻辑电路的延时约束,不再依赖于目标模块外部的其他模块的信息进行延时约束,降低了边缘逻辑路径的时间约束的复杂度,只需在此基础上进行最优化设计电路结构即可提高与目标模块的相邻模块的时延收敛的可能,在物理实现后期对全部模块进行统一测试时减少针对边缘时序收敛的修改,从而提高了时序收敛效率。

- 还没有人留言评论。精彩留言会获得点赞!