一种内存测试方法及内存测试设备与流程

1.本发明的所公开实施例涉及存储器领域,且更具体而言,涉及一种内存测试方法及内存测试设备。

背景技术:

2.目前,dram(dynamic random access memory,动态随机存取存储器)的测试主要分为机台测试,例如advantest系列等机台,以及平台测试,例如arm平台、x86平台等。在机台测试或平台测试中,分别运行不同的测试算法,以验证dram颗粒是否良品。

3.其中,机台测试或平台测试中的各种图形(pattern)测试算法,均是在固定电压及固定频率下进行测试,这样待测dram颗粒是针对特定电压及频率而言,无法确定待测dram颗粒的稳定性,从而无法提高测试的良品率。

技术实现要素:

4.根据本发明的实施例,本发明提出一种内存测试方法及内存测试设备,以解决上述问题。

5.根据本发明的第一方面,公开一种实例性的内存测试方法,包括:控制待测内存的至少一个工作电压和/或运行频率按照预设规则进行变化;以及在变化中的至少一个工作电压和/或运行频率下,控制执行至少一个图形算法,以对所述待测内存进行测试。

6.在一些实施例中,所述预设规则包括间隔预设时间等值下降的规则、间隔预设时间等值上升的规则和随机变化的规则中至少一个。

7.在一些实施例中,所述控制所述待测内存的至少一个工作电压和/或运行频率按照预设规则进行变化,包括:控制所述待测内存的至少一个工作电压按照所述间隔预设时间等值下降的规则、所述间隔预设时间等值上升的规则或所述随机变化的规则进行变化。

8.在一些实施例中,所述控制所述待测内存的至少一个工作电压和/或运行频率按照预设规则进行变化,包括:控制所述待测内存的运行频率按照所述间隔预设时间等值下降的规则、所述间隔预设时间等值上升的规则或所述随机变化的规则进行变化。

9.在一些实施例中,所述控制所述待测内存的至少一个工作电压和/或运行频率按照预设规则进行变化,包括:控制所述待测内存的至少一个工作电压按照所述间隔预设时间等值下降的规则、所述间隔预设时间等值上升的规则或所述随机变化的规则进行变化;以及控制所述待测内存的运行频率按照所述间隔预设时间等值下降的规则、所述间隔预设时间等值上升的规则或所述随机变化进行变化。

10.在一些实施例中,该方法进一步包括:控制对所述待测内存执行读写测试,以获取所述待测内存读取的数据和写入的数据;判断所述读取的数据与所述写入的数据是否一致;若是,则所述待测内存通过所述至少一个图形算法所对应的测试。

11.在一些实施例中,所述至少一个图形算法包括全0/全1图形算法、奇偶校验板图形算法和齐步图形算法。

12.在一些实施例中,所述待测内存包括ddr和lpddr

13.在一些实施例中,所述至少一个工作电压包括第一工作电压vdd、第二工作电压vdd1、第三工作电压vdd2和第四工作电压vddq中的至少一个。

14.根据本发明的第二方面,公开一种实例性的一种内存测试设备,包括与内存连接的控制电路和与所述控制电路连接的存储电路,其中,所述存储电路存储有测试程序,在执行时使得所述控制电路执行如上述第一方面中所述的内存测试方法。

15.本发明的有益效果有:通过控制待测内存的至少一个工作电压和/或运行频率按照预设规则进行变化,增大待测内存中颗粒的测试压力,使得在变化中的至少一个工作电压和/或运行频率下,控制至少一个图形算法,以对待测内存进行测试,实现测试出稳定性高的内存,排除稳定性差的内存,有效提高良品率。

附图说明

16.下面将结合附图及实施方式对本发明作进一步说明,附图中:

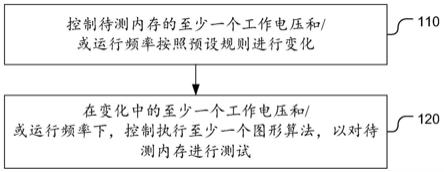

17.图1是本发明第一实施例的内存测试方法的流程图。

18.图2是本发明第二实施例的内存测试方法的流程图。

19.图3是本发明实施例的内存测试设备的结构示意图。

具体实施方式

20.为使本领域的技术人员更好地理解本发明的技术方案,下面结合附图和具体实施方式对本发明的技术方案做进一步详细描述。

21.如图1所示,为本发明第一实施例的内存测试方法的流程图。该内存测试方法可应用于机台测试或平台测试。该方法包括:

22.步骤110:控制待测内存的至少一个工作电压和/或运行频率按照预设规则进行变化。

23.待测内存可以为dram,包括ddr(double data rate,双倍速率同步动态随机存储器)1、ddr2、ddr3、ddr3l和ddr4,以及lpddr(low power ddr,低功率ddr)1芯片、lpddr2芯片、lpddr3芯片、lpddr4芯片、lpddr4x芯片和lpddr5芯片。

24.待测内存具有多个工作电压,以待测内存为dram为例,其工作电压包括第一工作电压vdd、第二工作电压vdd1、第三工作电压vdd2和第四工作电压vddq中的一个或多个,例如,lpddr1芯片包括第一工作电压vdd和第四工作电压vddq,lpddr2芯片包括第二工作电压vdd1、第三工作电压vdd2和第四工作电压vddq。

25.待测内存的工作电压具有电压范围,如下表1所示,其示出了不同类型内存的工作电压范围,例如,lpddr4芯片的第二工作电压vdd1的电压范围为1.7v-1.95v。按照预设规则进行变化,变化后的工作电压仍处于该电压范围内。

26.待测内存的运行频率具有频率范围,如下表1所示,其示出了不同类型内存的运行频率的范围,例如,lpddr4芯片的运行频率的频率范围为133mhz-1866mhz。按照预设规则进行变化,变化后的运行频率仍处于该频率范围内。

27.表1 不同类型内存工作电压以及运行频率范围的表

[0028][0029]

步骤120:在变化中的至少一个工作电压和/或运行频率下,控制执行至少一个图形算法,以对待测内存进行测试。

[0030]

在变化中的工作电压和/或运行频率下,控制执行某个图形算法,从而对待测内存进行测试。若控制执行图形算法以对待测内存进行测试后,没有检测出相应故障,或者满足执行该图形算法后的测试要求,则待测内存通过该图形算法所对应的测试。

[0031]

至少一个图形算法包括全0/全1图形算法、奇偶校验板图形算法和齐步图形算法等规则图形算法,或者不规则图形算法,例如不规则的随机读写算法。

[0032]

全0/全1图形算法采用的是全0/全1图形,其将待测内存中的全部存储单元(也称为存储晶粒)按照顺序写0、读0、写1、读1,测试图形序列长度为4n,可用于测试待测内存的固定故障。

[0033]

奇偶校验板图形算法采用的是奇偶校验板图形,其是根据存储单元选址地址码的奇偶性而定的,其中,如果某个存储单元的行地址码和列地址码中有偶数个1,其奇偶性为0,则该存储单元中写“0”,否则写“1”。奇偶校验板图形算法可用于检测待测内存的固定故障、地址译码故障和相邻位的短路故障。

[0034]

齐步图形算法,也称为march算法,采用的是齐步图形,其对待测内存中的每个存储单元依次进行检验,从第一个存储单元开始,逐一对每个存储单元进行取反和检验,直到最后一个存储单元检测结束,此时完成一遍扫描。齐步图形算法可用于检测全部的固定故障、地址译码故障和转换故障。

[0035]

不规则的随机读写算法,将待测内存中的存储单元按照无规则写0、读0,或者按照无规则写1、读1,以对待测内存进行测试。

[0036]

本实施例中,通过控制待测内存的至少一个工作电压和/或运行频率按照预设规则进行变化,增大待测内存中颗粒的测试压力,使得在变化中的至少一个工作电压和/或运

行频率下,控制至少一个图形算法,以对待测内存进行测试,实现测试出稳定性高的内存,排除稳定性差的内存,有效提高良品率。

[0037]

在一些实施例中,预设规则包括间隔预设时间等值下降的规则、间隔预设时间等值上升的规则和随机变化的规则中至少一个。

[0038]

其中,间隔预设时间等值下降的规则,表示控制工作电压和/或运行频率的数值在其电压范围和/或频率范围内每间隔预设时间下降预设数值。例如,从工作电压vdd的电压范围中的最大值到最小值,每间隔预设时间t1,控制工作电压vdd的数值下降预设数值y1。

[0039]

间隔预设时间等值上升的规则,表示控制工作电压和/或运行频率的数值在其电压范围和/或频率范围内每间隔预设时间上升预设数值。例如,从工作电压vdd的电压范围中的最小值到最大值,每间隔预设时间t2,控制工作电压vdd的数值下降预设数值y2。

[0040]

随机变化的规则,表示控制工作电压和/或运行频率的数值在其电压范围和/或频率范围内无规则变化。

[0041]

在一些实施例中,步骤120包括:控制待测内存的至少一个工作电压按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化。例如,控制lpddr4芯片的第二工作电压vdd1、第三工作电压vdd2和第四工作电压vddq按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化,从而在变化中的第二工作电压vdd1、第三工作电压vdd2和第四工作电压vddq中的一个或多个下,控制执行至少一个图形算法,以对lpddr4芯片进行测试。本实施例中,控制待测内存的至少一个工作电压按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化,也就是说,仅控制待测内存的工作电压进行变化,进而仅在变化中的工作电压下,对待测内存进行测试,增大内存的测试压力,提高测试的良品率。

[0042]

在一些实施例中,步骤120包括:控制待测内存的运行频率按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化。例如,控制dram(例如,lpddr1芯片、ddr1等)的运行频率按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化,从而在变化中的运行频率下,控制执行至少一个图形算法,以对dram进行测试。本实施例中,控制待测内存的运行频率按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化,也就是说,仅控制待测内存的运行频率进行变化,进而仅在变化中的运行频率下,对待测内存进行测试,增大内存的测试压力,提高测试的良品率。

[0043]

在一些实施例中,步骤120包括:控制待测内存的至少一个工作电压按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化;以及控制待测内存的运行频率按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化进行变化。

[0044]

例如,先控制lpddr4芯片的第二工作电压vdd1、第三工作电压vdd2和第四工作电压vddq按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化,随后,控制lpddr4芯片的运行频率按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化,从而在变化中的第二工作电压vdd1、第三工作电压vdd2和第四工作电压vddq以及变化中的运行频率下,控制执行至少一个图形算法,对lpddr4芯片进行测试。

[0045]

又例如,先控制lpddr4芯片的运行频率按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化,随后,控制lpddr4芯片的第二工作电压vdd1、第三工作电压vdd2和第四工作电压vddq按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化,从而在变化中的第二工作电压vdd1、第三工作电压vdd2和第四工作电压vddq以及变化中的运行频率下,控制执行至少一个图形算法,对lpddr4芯片进行测试。

[0046]

又例如,控制lpddr4芯片的运行频率按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化,同时,控制lpddr4芯片的第二工作电压vdd1、第三工作电压vdd2和第四工作电压vddq按照间隔预设时间等值下降的规则、间隔预设时间等值上升的规则或随机变化的规则进行变化,从而在变化中的第二工作电压vdd1、第三工作电压vdd2和第四工作电压vddq以及变化中的运行频率下,控制执行至少一个图形算法,对lpddr4芯片进行测试。

[0047]

本实施例中,控制内存的至少一个工作电压和运行频率,进而仅在变化中的工作电压和运行频率下,对待测内存进行测试,进一步增大内存的测试压力,提高测试的良品率。

[0048]

如图2所示,为本发明第二实施例的内存测试方法的流程图。在上述实施例的基础上,该方法进一步包括:

[0049]

步骤210:控制待测内存的至少一个工作电压和/或运行频率按照预设规则进行变化。

[0050]

步骤220:在变化中的至少一个工作电压和/或运行频率下,控制执行至少一个图形算法,以对待测内存进行测试。

[0051]

步骤230:控制对待测内存执行读写测试,以获取待测内存读取的数据和写入的数据。

[0052]

在步骤220之后,即对待测内存进行至少一个图形算法所对应的测试之后,进行至少一个图形算法所对应的测试的待测内存进行读写测试。

[0053]

步骤240:判断读取的数据与写入的数据是否一致。若是,则执行步骤250,若否,则内存没有通过相应的测试。

[0054]

步骤250:待测内存通过至少一个图形算法所对应的测试。

[0055]

本实施例中,通过在控制执行至少一个图形算法以对待测内存进行相应的测试之后,进一步通过读写测试来判断待测内存是否通过相应测试,进一步提高的良品率。

[0056]

需要说明的是,本实施例中的相关内容,例如步骤210和步骤220,与上述实施例中相同,详见上述实施例的说明,在此不再说明。

[0057]

如图3所示,为本发明实施例的内存测试设备的结构示意图。该设备300可以为机台或平台,例如arm平台、x86平台。该设备300包括控制电路310和存储电路320,其中待测内存与控制电路310连接,存储电路320与控制电路310连接。需要说明的是,本发明仅描述与本发明相关的部分,其他未提及的部分也应在本发明的范围内。例如,待测内存通过测试架实现与控制电路310的连接。

[0058]

存储电路320存储有测试程序。该存储电路320还用于存储系统程序以及图形算法。

[0059]

在一些实施例中,该测试程序在执行时使得控制电路310执行如下操作:

[0060]

控制待测内存的至少一个工作电压和/或运行频率按照预设规则进行变化;

[0061]

在变化中的至少一个工作电压和/或运行频率下,控制执行至少一个图形算法,以对待测内存进行测试。

[0062]

对于根据本实施例的内存测试设备300中的各个组件的功能的具体描述,请参考上述内存测试方法的相应实施例的相关描述。

[0063]

所属领域的技术人员易知,可在保持本发明的教示内容的同时对装置及方法作出诸多修改及变动。因此,以上公开内容应被视为仅受随附权利要求书的范围的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1