半导体存储装置的制作方法

半导体存储装置

1.[相关申请案]

[0002]

本技术案享有以日本专利申请案2021-047990号(申请日:2021年3月22日)为基础申请案的优先权。本技术案通过参照该基础申请案而包含基础申请案的全部内容。

技术领域

[0003]

本实施方式涉及一种半导体存储装置。

背景技术:

[0004]

众所周知的是如下半导体存储装置,其在与衬底表面交叉的方向上积层有多个存储单元。

技术实现要素:

[0005]

本发明所要解决的课题是提供一种能够高集成化的半导体存储装置。

[0006]

一实施方式的半导体存储装置具备:多个存储区块区域,沿第1方向排列;接线区域,相对于多个存储区块区域沿第1方向排列;及配线区域,在第1方向上延伸,且与多个存储区块区域及接线区域沿与第1方向交叉的第2方向排列。多个存储区块区域分别具备:多个存储串,在第1方向上延伸,且沿第2方向排列;及第1配线,在第2方向上延伸,且共通地连接于多个存储串。配线区域具备第2配线,该第2配线在第1方向上延伸,且共通地连接于与多个存储区块区域对应的多个第1配线。接线区域具备:第3配线,电连接于第2配线;及接触电极,在与第1方向及第2方向交叉的第3方向上延伸,且连接于第3配线。

[0007]

一实施方式的半导体存储装置具备:多个存储单元,沿第1方向排列;多个第1配线,沿第1方向排列,且电连接于多个存储单元;及接触电极,在第1方向上延伸,且连接于多个第1配线中的任一配线。接触电极具备:第1部分,在第1方向上延伸;及第2部分,连接于第1部分,且连接于多个第1配线中的任一配线的与第1方向交叉的第2方向的侧面。当将与第1方向垂直、且包含接触电极的第2部分的截面设为第1截面时,在第1截面中,第2部分的轮廓线的一部分沿着第1圆的圆周设置,第2部分的轮廓线的除所述部分以外的部分设置在第1圆的内侧。

[0008]

一实施方式的半导体存储装置具备:多个存储层,沿第1方向排列;多个接触电极,在第1方向上延伸,且连接于多个存储层;及电压供给线,在第1方向上延伸,且连接于多个存储层。多个存储层分别具备:存储单元;第1配线,电连接于存储单元;第2配线,电连接于多个接触电极中的任一接触电极;第1晶体管,电连接于第1配线与第2配线之间;第2晶体管,电连接于第2配线与电压供给线之间;及第3晶体管,电连接于第2晶体管与电压供给线之间。第1配线作为第3晶体管的栅极电极发挥功能。

附图说明

[0009]

图1是表示第1实施方式的半导体存储装置的一部分构成的示意性俯视图。

[0010]

图2是将图1中的a所示的部分放大而表示的示意性俯视图。

[0011]

图3是将图2中的b所示的部分放大而表示的示意性俯视图。

[0012]

图4是包含图3所示的部分的示意性立体图。

[0013]

图5是将图1中的c所示的部分放大而表示的示意性俯视图。

[0014]

图6是将图5所示的结构沿着d-d'线切断并沿着箭头方向观察的示意性剖视图。

[0015]

图7是将图5所示的结构沿着e-e'线切断并沿着箭头方向观察的示意性剖视图。

[0016]

图8是用以说明第1实施方式的半导体存储装置的制造方法的示意性剖视图。

[0017]

图9是用以说明所述制造方法的示意性俯视图。

[0018]

图10是用以说明所述制造方法的示意性剖视图。

[0019]

图11是用以说明所述制造方法的示意性剖视图。

[0020]

图12是用以说明所述制造方法的示意性俯视图。

[0021]

图13是用以说明所述制造方法的示意性剖视图。

[0022]

图14是用以说明所述制造方法的示意性剖视图。

[0023]

图15是用以说明所述制造方法的示意性俯视图。

[0024]

图16是用以说明所述制造方法的示意性剖视图。

[0025]

图17是用以说明所述制造方法的示意性剖视图。

[0026]

图18是用以说明所述制造方法的示意性俯视图。

[0027]

图19是用以说明所述制造方法的示意性剖视图。

[0028]

图20是用以说明所述制造方法的示意性剖视图。

[0029]

图21是用以说明所述制造方法的示意性剖视图。

[0030]

图22是用以说明所述制造方法的示意性剖视图。

[0031]

图23是用以说明所述制造方法的示意性俯视图。

[0032]

图24是用以说明所述制造方法的示意性俯视图。

[0033]

图25是用以说明所述制造方法的示意性俯视图。

[0034]

图26是用以说明所述制造方法的示意性俯视图。

[0035]

图27是用以说明所述制造方法的示意性俯视图。

[0036]

图28是用以说明所述制造方法的示意性剖视图。

[0037]

图29是用以说明所述制造方法的示意性剖视图。

[0038]

图30是用以说明所述制造方法的示意性剖视图。

[0039]

图31是用以说明所述制造方法的示意性剖视图。

[0040]

图32是用以说明所述制造方法的示意性剖视图。

[0041]

图33是用以说明所述制造方法的示意性剖视图。

[0042]

图34是用以说明所述制造方法的示意性剖视图。

[0043]

图35是用以说明所述制造方法的示意性剖视图。

[0044]

图36是用以说明所述制造方法的示意性剖视图。

[0045]

图37是用以说明所述制造方法的示意性剖视图。

[0046]

图38是用以说明所述制造方法的示意性剖视图。

[0047]

图39是用以说明所述制造方法的示意性剖视图。

[0048]

图40是表示第2实施方式的半导体存储装置的一部分构成的示意性俯视图。

[0049]

图41是表示所述半导体存储装置的一部分构成的示意性电路图。

[0050]

图42是表示所述半导体存储装置的一部分构成的示意性立体图。

[0051]

图43是用以说明第2实施方式的半导体存储装置的制造方法的示意性俯视图。

[0052]

图44是用以说明所述制造方法的示意性剖视图。

[0053]

图45是用以说明所述制造方法的示意性俯视图。

[0054]

图46是用以说明所述制造方法的示意性剖视图。

[0055]

图47是用以说明所述制造方法的示意性俯视图。

[0056]

图48是用以说明所述制造方法的示意性剖视图。

[0057]

图49是用以说明所述制造方法的示意性剖视图。

[0058]

图50是用以说明所述制造方法的示意性剖视图。

[0059]

图51是用以说明所述制造方法的示意性俯视图。

[0060]

图52是用以说明所述制造方法的示意性剖视图。

[0061]

图53是用以说明所述制造方法的示意性剖视图。

[0062]

图54是用以说明所述制造方法的示意性剖视图。

[0063]

图55是用以说明所述制造方法的示意性俯视图。

[0064]

图56是用以说明所述制造方法的示意性剖视图。

[0065]

图57是用以说明所述制造方法的示意性剖视图。

[0066]

图58是用以说明所述制造方法的示意性剖视图。

[0067]

图59是用以说明所述制造方法的示意性俯视图。

[0068]

图60是用以说明所述制造方法的示意性剖视图。

[0069]

图61是用以说明所述制造方法的示意性剖视图。

[0070]

图62是用以说明所述制造方法的示意性剖视图。

[0071]

图63是用以说明所述制造方法的示意性俯视图。

[0072]

图64是用以说明所述制造方法的示意性俯视图。

[0073]

图65是用以说明所述制造方法的示意性俯视图。

[0074]

图66是用以说明所述制造方法的示意性俯视图。

[0075]

图67是用以说明所述制造方法的示意性俯视图。

[0076]

图68是用以说明所述制造方法的示意性俯视图。

[0077]

图69是用以说明所述制造方法的示意性俯视图。

[0078]

图70是用以说明所述制造方法的示意性剖视图。

[0079]

图71是用以说明所述制造方法的示意性剖视图。

[0080]

图72是用以说明所述制造方法的示意性剖视图。

[0081]

图73是用以说明第2实施方式的半导体存储装置的变化例的示意性俯视图。

[0082]

图74是用以说明第2实施方式的半导体存储装置的变化例的示意性俯视图。

[0083]

图75是用以说明第2实施方式的半导体存储装置的变化例的示意性电路图。

[0084]

图76是用以说明第2实施方式的半导体存储装置的变化例的示意性俯视图。

[0085]

图77是用以说明第2实施方式的半导体存储装置的变化例的示意性俯视图。

具体实施方式

[0086]

接下来,参照附图对实施方式的半导体存储装置进行详细说明。另外,以下所示的实施方式仅为一例,并未意图限定本发明。此外,以下附图为示意性的图,有时为便于说明而省略一部分构成等。此外,有时对在多个实施方式中共通的部分附上相同符号,并省略说明。

[0087]

此外,本说明书中提及“半导体存储装置”的情况下,有时是指存储晶粒,也有时是指存储芯片、存储卡、ssd(solid state drive,固态驱动器)等包含控制器晶粒的存储系统。进而,也有时是指智能手机、平板终端、个人电脑等包含主机电脑的构成。

[0088]

此外,本说明书中,提及第1构成与第2构成“电连接”的情况下,可为第1构成与第2构成直接连接,也可为第1构成与第2构成经由配线、半导体构件或晶体管等连接。例如在将3个晶体管串联连接的情况下,即便第2个晶体管为断开(off)状态,第1个晶体管也可与第3个晶体管“电连接”。

[0089]

此外,本说明书中,提及第1构成“连接于”第2构成与第3构成“之间”的情况下,有时是指第1构成、第2构成及第3构成串联连接,且第2构成经由第1构成与第3构成连接。

[0090]

此外,本说明书中,提及电路等使2个配线等“导通”的情况下,例如有时是指该电路等包含晶体管等,该晶体管等设置在2个配线之间的电流路径上,且该晶体管等为接通(on)状态。

[0091]

此外,本说明书中,将与衬底的上表面平行的特定方向称为x方向,将与衬底的上表面平行且与x方向垂直的方向称为y方向,将与衬底的上表面垂直的方向称为z方向。

[0092]

此外,本说明书中,有时将沿特定面的方向称为第1方向,将沿该特定面与第1方向交叉的方向称为第2方向,将与该特定面交叉的方向称为第3方向。这些第1方向、第2方向及第3方向可与x方向、y方向及z方向中的任一方向对应,也可不与x方向、y方向及z方向中的任一方向对应。

[0093]

此外,本说明书中,“上”、“下”等表述以衬底为基准。例如,将沿上述z方向离开衬底的方向称为“上”,将沿z方向接近衬底的方向称为“下”。此外,对于某构成,在提及下表面、下端的情况下,是指该构成的衬底侧的面、端部,在提及上表面、上端的情况下,是指该构成的与衬底为相反侧的面、端部。此外,将与x方向或y方向交叉的面称为侧面等。

[0094]

[第1实施方式]

[0095]

[构成]

[0096]

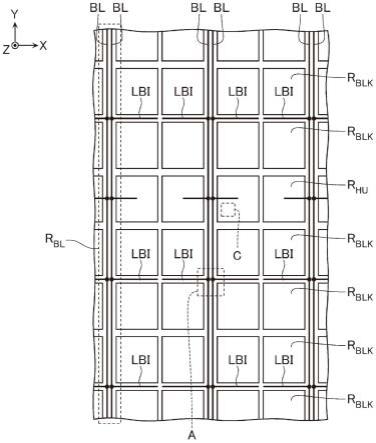

图1是表示第1实施方式的半导体存储装置的一部分构成的示意性俯视图。本实施方式的半导体存储装置具备多个存储区块区域r

blk

、多个接线区域r

hu

、及多个位线区域r

bl

。存储区块区域r

blk

在x方向及y方向上呈矩阵状排列。接线区域r

hu

分别对应于沿y方向排列的多个存储区块区域r

blk

而设置。接线区域r

hu

沿x方向排列,且在y方向上与存储区块区域r

blk

相邻。位线区域r

bl

分别对应于沿y方向排列的多个存储区块区域r

blk

、及这些存储区块区域r

blk

所对应的接线区域r

hu

而设置。位线区域r

bl

与这多个存储区块区域r

blk

及接线区域r

hu

沿x方向排列。

[0097]

图1的例子中,在沿y方向排列的2个存储区块区域r

blk

之间,设置有在x方向上延伸的局部区块连接线lbi。这2个存储区块区域r

blk

中的构成分别连接于局部区块连接线lbi。此外,在位线区域r

bl

设置有在y方向上延伸的位线bl。沿y方向排列的多个局部区块连接线

lbi共通地连接于该位线bl。此外,位线bl经由接线区域r

hu

中的构成而电连接于未图示的周边电路。

[0098]

图2是将图1中的a所示的部分放大而表示的示意性俯视图。图3是将图2中的b所示的部分放大而表示的示意性俯视图。图4是包含图3所示的部分的示意性立体图。

[0099]

如图2所示,在存储区块区域r

blk

设置有:多个存储单元区域r

mc

,沿y方向排列;及阶梯区域r

ld

,设置在y方向上相邻的2个存储单元区域r

mc

之间。此外,在存储区块区域r

blk

的y方向上的端部设置有选择晶体管区域r

sgd

。另外,沿y方向排列的2个存储区块区域r

blk

之间设置有局部区块连接线区域r

lbi

。

[0100]

图4表示半导体衬底sub的一部分。半导体衬底sub例如为包含硼(b)等p型杂质的硅(si)等半导体衬底。如图所示,本实施方式的半导体存储装置具备沿z方向排列的多个存储层ml。此外,在z方向上相邻的2个存储层ml之间设置有氧化硅(sio2)等绝缘层101。

[0101]

存储层ml具备沿x方向排列的多个半导体层110。这多个半导体层110分别跨及参照图2所说明的多个存储单元区域r

mc

、多个阶梯区域r

ld

、及选择晶体管区域r

sgd

而在y方向上延伸。半导体层110例如作为串联连接的多个存储晶体管(存储单元)、及与这些存储晶体管连接的选择晶体管的通道区域发挥功能。另外,以下说明中,有时将包含串联连接的多个存储晶体管、及与这些存储晶体管连接的选择晶体管的构成称为存储串。半导体层110例如也可包含非掺杂多晶硅(si)等。

[0102]

例如图3所示,存储单元区域r

mc

中设置有多个导电层120,这些导电层120位于在x方向上相邻的2个半导体层110之间,且沿y方向排列。此外,在存储单元区域r

mc

中,存储层ml具备多个栅极绝缘层130,这些栅极绝缘层130设置在多个导电层120的x方向上的侧面与半导体层110之间。

[0103]

导电层120例如作为多个存储晶体管的栅极电极、及与这些存储晶体管的栅极电极连接的字线等发挥功能。例如图3所示,导电层120也可包含氮化钛(tin)等阻障导电层121、及钨(w)等导电层122。例如图4所示,导电层120贯通多个存储层ml而在z方向上延伸。另外,在y方向上相邻的2个导电层120之间,设置有氧化硅(sio2)等绝缘层123(图3)。

[0104]

栅极绝缘层130例如具备:隧道绝缘层131,设置在半导体层110的x方向上的侧面;电荷储存层132,设置在该x方向上的侧面;及阻挡绝缘层133,设置在该x方向上的侧面。

[0105]

隧道绝缘层131例如也可包含氧化硅(sio2)等。

[0106]

电荷储存层132例如也可包含多晶硅(si)等。此外,该多晶硅(si)中可包含磷(p)等n型杂质或硼(b)等p型杂质,也可不包含这些杂质。

[0107]

阻挡绝缘层133例如也可包含氧化硅(sio2)等。此外,阻挡绝缘层133也可包含氧化铝(alo)、氧化铪(hfo)或其它绝缘性的金属氧化膜。

[0108]

选择晶体管区域r

sgd

(图2)中设置有导电层140及导电层150,该导电层140及导电层150位于在x方向上相邻的2个半导体层110之间,且沿y方向排列。在选择晶体管区域r

sgd

中,存储层ml具备多个半导体层160,这些半导体层160连接于多个半导体层110的y方向上的一端。

[0109]

导电层140例如作为接触电极等发挥功能,该接触电极用以在半导体层110中形成电洞的通道,或用以对形成在半导体层110中的电洞的通道供给电压。例如图3所示,导电层140也可包含:多晶硅(si)等半导体层141,包含硼(b)等p型杂质;及氮化钛(tin)等导电层

142。导电层140贯通多个存储层ml而在z方向上延伸。此外,也可在导电层140的外周面设置包含非掺杂多晶硅(si)等的半导体层143。另外,也可省略半导体层143。

[0110]

导电层150例如作为晶体管的栅极电极、及与该晶体管的栅极电极连接的配线等发挥功能。例如图3所示,导电层150也可包含:多晶硅(si)等半导体层151,包含磷(p)等n型杂质;及氮化钛(tin)等导电层152。导电层150贯通多个存储层ml而在z方向上延伸。此外,在导电层150的外周面设置有氧化硅(sio2)等绝缘层153。此外,也可在导电层150的中心部分设置有氧化硅(sio2)等绝缘层154。另外,导电层150的y方向上的宽度,也可大于导电层140的y方向上的宽度。

[0111]

半导体层160例如也可包含多晶硅(si)等半导体层,该多晶硅(si)等半导体层包含磷(p)等n型杂质。此外,在x方向上相邻的2个半导体层160之间设置有绝缘层161。绝缘层161例如也可包含氧化硅(sio2)等。绝缘层161贯通多个存储层ml而在z方向上延伸。

[0112]

在阶梯区域r

ld

(图2)中,在x方向上相邻的2个半导体层110之间设置有导电层140或导电层150。此外,在导电层140及导电层150的外周面分别设置有半导体层143(图3)及绝缘层153(图3),但省略此图示。

[0113]

在局部区块连接线区域r

lbi

(图2)中,存储层ml具备导电层170。此外,在局部区块连接线区域r

lbi

中,设置有沿着导电层170排列在x方向上的多个绝缘层171(图3)。

[0114]

导电层170例如作为局部区块连接线lbi(图1)发挥功能。导电层170例如也可包含氮化钛(tin)等导电层。导电层170在x方向上延伸,且经由多个半导体层160而连接于多个半导体层110。另外,导电层170电连接于沿y方向排列的2个存储区块区域r

blk

中的半导体层110。

[0115]

绝缘层171例如也可包含氧化硅(sio2)等。例如图4所示,绝缘层171贯通多个存储层ml而在z方向上延伸。

[0116]

在位线区域r

bl

中,存储层ml具备在y方向上延伸的一对导电层180。此外,在位线区域r

bl

中设置有多个绝缘层181,这些绝缘层181位于在x方向上相邻的2个导电层180之间,且沿y方向排列。

[0117]

导电层180例如作为位线bl(图1)发挥功能。导电层180例如也可包含氮化钛(tin)等导电层。导电层180在y方向上延伸,且连接于多个导电层170的x方向上的一端部。

[0118]

绝缘层181例如也可包含氧化硅(sio2)等。绝缘层181贯通多个存储层ml而在z方向上延伸。另外,在y方向上相邻的2个绝缘层181之间,设置有氧化硅(sio2)等绝缘层182。绝缘层181的x方向上的宽度,也可大于绝缘层182的x方向上的宽度。

[0119]

图5是将图1中的c所示的部分放大而表示的示意性俯视图。图6是将图5所示的结构沿着d-d'线切断并沿着箭头方向观察的示意性剖视图。图7是将图5所示的结构沿着e-e'线切断并沿着箭头方向观察的示意性剖视图。

[0120]

如图5所示,在接线区域r

hu

设置有:多个引出线区域r

ll

,沿x方向排列;及接触电极区域r

cc

,设置在x方向上相邻的2个引出线区域r

ll

之间。

[0121]

在引出线区域r

ll

中,存储层ml具备在y方向上延伸的导电层190。此外,在引出线区域r

ll

中设置有多个绝缘层191,这些绝缘层191沿着导电层190排列在y方向上。

[0122]

导电层190例如也可包含氮化钛(tin)等导电层。导电层190与参照图2~图4所说明的导电层180导通,并经由这些导电层180而与参照图2~图4所说明的导电层170导通。另

外,图5的例子中,在导电层190的x方向上的侧面设置有多个凸状曲面,这些曲面对应于多个绝缘层191。

[0123]

绝缘层191例如也可包含氧化硅(sio2)等绝缘层。例如图6所示,绝缘层191贯通多个存储层ml而在z方向上延伸。

[0124]

例如图5所示,在接触电极区域r

cc

中设置有多个接触电极cc,这些接触电极cc沿着导电层190排列在y方向上。此外,在接触电极区域r

cc

中,存储层ml具备氮化硅(si3n4)等绝缘层102。

[0125]

例如图6所示,接触电极cc具备:大致圆柱状的部分192;及大致圆盘状的部分193,设置在该部分192的下端部。

[0126]

部分192例如也可包含氮化钛(tin)等阻障导电层194、及钨(w)等导电层195。部分192贯通多个存储层ml而在z方向上延伸。此外,也可在该部分192的外周面设置有氧化硅(sio2)等绝缘层196。绝缘层196的外周面的一部分与绝缘层101相接。此外,绝缘层196的外周面的一部分与绝缘层102相接。绝缘层196的与绝缘层102相接的部分的径向上的厚度,也可大于绝缘层196的与绝缘层101相接的部分的径向上的厚度。

[0127]

部分193例如也可包含氮化钛(tin)等阻障导电层194。部分193包含在任一存储层ml中,且连接于任一存储层ml中所含的导电层190的x方向上的侧面。另外,在接线区域r

hu

中也可设置有接触电极cc,该接触电极cc对应于所有存储层ml。此时,接触电极cc的个数可与存储层ml的个数一致,也可多于存储层ml的个数。

[0128]

另外,例如图5中所例示,部分192的轮廓线也可沿着具备特定半径的圆的圆周来设置。此外,部分193的轮廓线的一部分也可沿着具有比所述圆大的半径的圆的圆周来设置。此外,部分193的轮廓线的除所述部分以外的部分也可设置在该圆的内侧。例如图5的例子中,部分193的与导电层190的连接部分包含多个凹状曲面。该连接部分设置在所述圆的内侧。此外,图5的例子中,部分193的与绝缘层196的连接部分包含凹状曲面,该曲面沿着以与该绝缘层196对应的接触电极cc的中心点为中心的圆的外周面来设置。该连接部分设置在所述圆的内侧。另外,部分193的xy截面中的面积,也可大于部分192的xy截面中的面积。

[0129]

[效果]

[0130]

具备沿z方向排列的多个导电层或半导体层的半导体存储装置为人所周知。在此种半导体存储装置中有时会设置有接线区域,该接线区域用以连接这多个导电层或半导体层与周边电路。在接线区域中设置有在z方向上延伸的多个接触电极。此外,在接线区域中,为了将多个导电层或半导体层与多个接触电极连接,例如有时会使多个导电层或半导体层的端部位置偏移而形成大致阶梯状的结构。此时,沿z方向排列的导电层或半导体层的层数越增加,接线区域的面积就越增大。

[0131]

此处,如参照图1所说明,本实施方式的半导体存储装置中,多个存储区块区域r

blk

沿y方向排列。此外,不是对应于这多个存储区块区域r

blk

而分别设置接线区域,而是设置与这多个存储区块区域r

blk

对应的共通的接线区域r

hu

。根据此种构成,能够大幅削减接线区域r

hu

的面积。

[0132]

此外,在采用上述大致阶梯状的结构时,导电层或半导体层的整个下表面对向于比其更靠下层的导电层或半导体层的上表面。由此,在z方向上相邻的2个导电层或半导体层之间的静电电容有时相对性变大。此外,越是设置在下层的导电层或半导体层,该对向面

积就越大。

[0133]

由此,本实施方式的半导体存储装置中,采用参照图5~图7所说明的接触电极cc来代替上述大致阶梯状的结构。该接触电极cc具备:部分192,在z方向上延伸;及大致圆盘状的部分193,连接于该部分192的下端。此外,该大致圆盘状的部分193分别连接于导电层190的侧面。

[0134]

所述构成能够使沿z方向排列的2个部分193之间的对向面积相对较小。由此,能够使在z方向上相邻的2个导电层或半导体层之间的静电电容相对较小。此外,根据所述构成,也能够将设置在下层的导电层或半导体层之间的静电电容抑制在固定大小的范围内。

[0135]

[制造方法]

[0136]

图8~图39是用以说明第1实施方式的半导体存储装置的制造方法的示意性剖视图或俯视图。图8、图10、图11、图13、图14、图16、图17、图19~图22、图28及图29对应于图4的一部分所示的截面。但,为便于说明,在这些图中追加有与绝缘层181对应的截面。图9、图12、图15、图18、及图23~图27表示与图3对应的部分。图30、图32、图34、图36及图38表示对应于图6的部分。图31、图33、图35、图37及图39表示对应于图7的部分。

[0137]

所述制造方法中,例如图8所示,交替形成多个绝缘层101与多个绝缘层102。例如通过cvd(chemical vapor deposition,化学气相沉积)等进行该工序。

[0138]

接下来,例如图9及图10所示,形成开口123a。开口123a如图9所示在y方向上延伸,且沿x方向排列。此外,开口123a如图10所示在z方向上延伸,且贯通沿z方向排列的多个绝缘层101及多个绝缘层102。例如通过rie(reactive ion etching,反应性离子蚀刻)等进行该工序。

[0139]

接下来,例如图11所示,形成绝缘层123、182。例如通过cvd等进行该工序。

[0140]

接下来,例如图12及图13所示,在与导电层120对应的位置形成开口120a。此外,在与导电层140对应的位置形成开口140a。此外,在与绝缘层161对应的位置形成开口161a。这些开口120a、140a、161a如图13所示在z方向上延伸,使沿z方向排列的多个绝缘层101及多个绝缘层102的x方向上的侧面露出。例如通过rie等进行该工序。

[0141]

接下来,例如图14所示,在开口120a的内部形成牺牲层120b。此外,在开口140a的内部形成牺牲层140b,但省略此图示。此外,在开口161a的内部形成牺牲层161b,但省略此图示。例如通过cvd等进行该工序。

[0142]

接下来,例如图15及图16所示,在与导电层150对应的位置形成开口150a。此外,在与绝缘层171对应的位置形成开口171a。此外,在与绝缘层181对应的位置形成开口181a。此外,在与绝缘层191(图5)对应的位置形成开口,但省略此图示。这些开口150a、171a、181a等如图16所示在z方向上延伸,使沿z方向排列的多个绝缘层101及多个绝缘层102的x方向上的侧面露出。例如通过rie等进行该工序。

[0143]

接下来,例如图17所示,在开口181a的内部形成牺牲层181b。此外,在开口150a的内部形成牺牲层150b,但省略此图示。此外,在开口171a的内部形成牺牲层171b,但省略此图示。此外,在与绝缘层191(图5)对应的位置形成牺牲层,但省略此图示。例如通过cvd等进行该工序。

[0144]

接下来,例如图18及图19所示,除去牺牲层120b。例如通过湿式蚀刻等进行该工序。

[0145]

接下来,例如图20所示,形成半导体层110的一部分。该工序中,例如通过经由开口120a的湿式蚀刻等方法而将绝缘层102的一部分除去。此外,通过cvd等方法而形成半导体层110的一部分。

[0146]

接下来,例如图21所示形成隧道绝缘层131及电荷储存层132。该工序中,例如通过经由开口120a的湿式蚀刻等方法而将半导体层110的一部分除去,从而使绝缘层101的上表面的一部分及下表面的一部分露出。此外,通过氧化处理或cvd等方法而形成隧道绝缘层131。此外,通过cvd等方法而形成电荷储存层132。此外,通过湿式蚀刻等方法而将电荷储存层132的一部分除去,电荷储存层132在z方向上断开。

[0147]

接下来,例如图22所示,在开口120a的内部形成阻挡绝缘层133、阻障导电层121及导电层122。例如通过cvd等方法进行该工序。

[0148]

接下来,例如图23所示,除去牺牲层140b。例如通过湿式蚀刻等进行该工序。

[0149]

接下来,例如图24所示,形成半导体层110的一部分。该工序中,例如通过经由开口140a的湿式蚀刻等方法而将绝缘层102的一部分除去。此外,通过cvd等方法而形成半导体层110的一部分。

[0150]

接下来,在开口140a的内部形成半导体层143、半导体层141及导电层142。例如通过cvd等方法进行该工序。

[0151]

接下来,除去牺牲层150b。例如通过湿式蚀刻等进行该工序。

[0152]

接下来,例如图25所示,在开口150a的内部形成绝缘层153、半导体层151、导电层152及半导体层154。例如通过cvd等方法进行该工序。

[0153]

接下来,除去牺牲层161b。例如通过湿式蚀刻等进行该工序。

[0154]

接下来,例如图26所示,形成半导体层160。该工序中,例如通过经由开口161a的湿式蚀刻等方法而将绝缘层102的一部分除去。此外,通过cvd等方法而形成半导体层160。

[0155]

接下来,在开口161a的内部形成绝缘层161。例如通过cvd等方法进行该工序。

[0156]

接下来,例如图27及图28所示,除去牺牲层171b、181b。此外,在与绝缘层191对应的位置上除去牺牲层,但省略此图示。例如通过湿式蚀刻等进行该工序。

[0157]

接下来,例如图29所示,形成导电层180。此外,形成导电层170(图3)及导电层190(图5),但省略此图示。该工序中,例如通过经由开口171a、181a等的湿式蚀刻等方法而将绝缘层102的一部分除去。此外,通过cvd等方法而形成导电层170、180、190。

[0158]

接下来,例如图3及图4所示,在开口171a、181a的内部形成绝缘层171、181。此外,形成绝缘层191(图5、图6),但省略此图示。例如通过cvd等方法进行该工序。

[0159]

接下来,例如图30及图31所示,在与接触电极cc对应的位置形成开口cca。开口cca在z方向上延伸,使任一绝缘层101的上表面的一部分露出。该工序中,设置在接线区域r

hu

中的所有绝缘层101的上表面的一部分也可经由多个开口cca露出。此外,多个开口cca贯通多个绝缘层101、102而在z方向上延伸,使这些绝缘层101、102的侧面露出。

[0160]

接下来,例如图32及图33所示,经由开口cca而将绝缘层102的一部分除去。例如通过湿式蚀刻等方法进行该工序。

[0161]

接下来,例如图34及图35所示,经由开口cca而形成绝缘层196。例如通过cvd等方法进行该工序。

[0162]

接下来,例如图36及图37所示,经由开口cca而将绝缘层196的一部分及绝缘层101

的一部分除去,使绝缘层102的上表面露出。例如通过rie等方法进行该工序。

[0163]

接下来,例如图38及图39所示,经由开口cca而将绝缘层102的一部分除去。例如通过湿式蚀刻等方法进行该工序。该工序中,例如将绝缘层102除去至导电层190的x方向上的侧面在开口cca的内部露出为止。

[0164]

接下来,例如图5~图7所示,在开口cca的内部形成接触电极cc。例如通过cvd等方法进行该工序。

[0165]

[第2实施方式]

[0166]

[构成]

[0167]

图40是表示第2实施方式的半导体存储装置的一部分构成的示意性俯视图。图41是表示所述半导体存储装置的一部分构成的示意性电路图。图42是表示所述半导体存储装置的一部分构成的示意性立体图。

[0168]

另外,以下说明中,对与第1实施方式相同的构成附上相同符号,并省略说明

[0169]

第2实施方式的半导体存储装置基本上以与第1实施方式的半导体存储装置相同的方式构成。但,第2实施方式的半导体存储装置具备存储层ml2(图42)来代替存储层ml。存储层ml2基本上以与存储层ml相同的方式构成。但,存储层ml2的接线区域中的结构与存储层ml的接线区域r

hu

中的结构不同。

[0170]

在接线区域中,存储层ml2具备图41所例示的前置放大器电路pa(信号放大电路)。

[0171]

接下来,对前置放大器电路pa的电路构成进行说明。

[0172]

前置放大器电路pa具备节点n1~n5。节点n1与参照图2~图4所说明的导电层180(位线bl)导通。节点n2与参照图5~图7所说明的接触电极cc导通。节点n3与供给接地电压的电压供给线导通。节点n4、n5分别连接于未图示的定序器。

[0173]

此外,前置放大器电路pa具备:晶体管tr1,连接于节点n1、n2之间;及晶体管tr2、tr3,串联连接于节点n2、n3之间。晶体管tr1~tr3例如为n通道型场效晶体管。

[0174]

晶体管tr1的源极电极连接于节点n2。晶体管tr1的漏极电极连接于节点n1。晶体管tr1的栅极电极连接于节点n4。

[0175]

晶体管tr2的源极电极连接于晶体管tr3的漏极电极。晶体管tr2的漏极电极连接于节点n2。晶体管tr2的栅极电极连接于节点n5。

[0176]

晶体管tr3的源极电极连接于节点n3。晶体管tr3的漏极电极连接于晶体管tr2的源极电极。晶体管tr3的栅极电极连接于节点n1。

[0177]

接下来,对前置放大器电路pa的动作进行简单说明。

[0178]

例如,在半导体存储装置的读出动作时,首先,对节点n4、n5供给“h、l”信号。由此,使晶体管tr1为接通状态,使晶体管tr2为断开状态。该状态下,经由节点n1、n2对位线bl(图1)进行充电。

[0179]

接下来,对节点n4、n5供给“l、l”信号。由此,使晶体管tr1、tr2为断开状态。该状态下,对特定导电层120(图2~图4)供给读出电压。由此,与该导电层120连接的选择存储单元对应于记录的数据而成为接通状态或断开状态。此外,对多个导电层120(图2~图4)供给比该读出电压大的读出通过电压。由此,选择存储单元与位线bl(图1)及未图示的源极线sl导通。由此,与接通状态的选择存储单元连接的位线释放电荷。伴随此,晶体管tr3(图41)成为断开状态。另一方面,维持与断开状态的选择存储单元连接的位线的电荷。此时,晶体管tr3

(图41)维持于接通状态。

[0180]

接下来,对节点n4、n5供给“l、h”信号。由此,使晶体管tr1为断开状态,使晶体管tr2为接通状态。此时,电流不流经与接通状态的选择存储单元对应的接触电极cc。另一方面,电流流经与断开状态的选择存储单元对应的接触电极cc。由此,通过检测该电流,能够检测选择存储单元中所记录的数据。

[0181]

根据所述构成,在与节点n1导通的位线bl(图1)进行放电时,位线bl与接触电极cc电切断。由此,能够相对高速地执行位线bl的放电。

[0182]

接下来,对前置放大器电路pa的构成更详细地进行说明。

[0183]

例如图40所示,在接线区域中,存储层ml2具备导电层210。此外,在接线区域中设置有沿导电层210排列的多个绝缘层211。

[0184]

导电层210作为参照图41所说明的节点n1发挥功能。导电层210例如也可包含氮化钛(tin)等阻障导电层、及钨(w)等导电层。

[0185]

绝缘层211例如也可包含氧化硅(sio2)等。例如图42所示,绝缘层211贯通多个存储层ml2而在z方向上延伸。

[0186]

此外,在接线区域中,存储层ml2具备导电层220。此外,在接线区域中设置有沿导电层220排列的多个绝缘层221。

[0187]

导电层220作为参照图41所说明的节点n2发挥功能。导电层220例如也可包含氮化钛(tin)等阻障导电层、及钨(w)等导电层。

[0188]

绝缘层221例如也可包含氧化硅(sio2)等。绝缘层221贯通多个存储层ml2而在z方向上延伸。

[0189]

此外,在接线区域中,存储层ml2具备半导体层230。此外,在接线区域中设置有导电层231,该导电层231连接于半导体层230。

[0190]

半导体层230作为参照图41所说明的晶体管tr3的源极区域发挥功能。半导体层230例如也可包含多晶硅(si)等,该多晶硅包含磷(p)等n型杂质。

[0191]

导电层231作为参照图41所说明的节点n3发挥功能。导电层231例如也可包含氮化钛(tin)等阻障导电层、及钨(w)等导电层。例如图42所示,导电层231贯通多个存储层ml2而在z方向上延伸。

[0192]

此外,在接线区域中,存储层ml2具备多个半导体层240。此外,在接线区域中设置有:多个导电层241,对应于多个半导体层240而设置;及绝缘层242,覆盖这多个导电层241的外周面。

[0193]

半导体层240作为参照图41所说明的晶体管tr1、tr2的通道区域发挥功能。半导体层240例如也可包含多晶硅(si)等,该多晶硅包含硼(b)等p型杂质。

[0194]

导电层241作为参照图41所说明的tr1、tr2的栅极电极发挥功能。此外,导电层241作为参照图41所说明的节点n4或节点n5发挥功能。导电层241例如也可包含氮化钛(tin)等阻障导电层、及钨(w)等导电层。

[0195]

绝缘层242作为参照图41所说明的晶体管tr1、tr2的栅极绝缘膜发挥功能。绝缘层242例如也可包含氧化硅(sio2)等。例如图42所示,导电层241及绝缘层242贯通多个存储层ml2而在z方向上延伸。

[0196]

此外,在接线区域中,存储层ml2具备:半导体层250,连接于半导体层230的外周面

的一部分;及绝缘层251,连接于半导体层250的外周面的一部分。此外,在接线区域中设置有:绝缘层252,连接于半导体层250;及半导体层253,连接于半导体层250的外周面的一部分。

[0197]

半导体层250作为参照图41所说明的晶体管tr3的通道区域发挥功能。半导体层250例如也可包含多晶硅(si)等,该多晶硅包含硼(b)等p型杂质。

[0198]

绝缘层251作为参照图41所说明的晶体管tr3的栅极绝缘膜发挥功能。绝缘层251例如也可包含氧化硅(sio2)等。

[0199]

绝缘层252例如也可包含氧化硅(sio2)等。例如图42所示,绝缘层252贯通多个存储层ml2而在z方向上延伸。

[0200]

半导体层253在包含半导体层250等的晶体管tr3中抑制泄漏电流。半导体层253例如也可包含多晶硅(si)等,该多晶硅包含硼(b)等p型杂质。另外,半导体层253中所含的杂质的浓度,大于半导体层250中所含的杂质的浓度。半导体层253贯通多个存储层ml2而在z方向上延伸。

[0201]

此外,在接线区域中,存储层ml2具备多个半导体层260。此外,在接线区域中设置有多个绝缘层261,这些绝缘层261连接于多个半导体层260。

[0202]

多个半导体层260的一部分连接于导电层210及半导体层240。所述半导体层260作为参照图41所说明的晶体管tr1的漏极区域发挥功能。此外,多个半导体层260的一部分连接于2个半导体层240、及导电层220。所述半导体层260作为参照图41所说明的晶体管tr1的源极区域、及晶体管tr2的漏极区域发挥功能。此外,多个半导体层260的一部分连接于半导体层240及半导体层250。所述半导体层260作为参照图41所说明的晶体管tr2的源极区域、及晶体管tr3的漏极区域发挥功能。半导体层260例如也可包含多晶硅(si)等,该多晶硅包含磷(p)等n型杂质。

[0203]

绝缘层261例如也可包含氧化硅(sio2)等。绝缘层261贯通多个存储层ml2而在z方向上延伸。

[0204]

此外,在接线区域中,存储层ml2具备半导体层270。半导体层270隔着绝缘层251而与半导体层250对向,且连接于导电层210。此外,在接线区域中设置有绝缘层271,该绝缘层271连接于半导体层270。

[0205]

半导体层270作为参照图41所说明的晶体管tr3的栅极电极发挥功能。半导体层270例如也可包含多晶硅(si)等,该多晶硅包含磷(p)等n型杂质。

[0206]

绝缘层271例如也可包含氧化硅(sio2)等。绝缘层271贯通多个存储层ml2而在z方向上延伸。

[0207]

[制造方法]

[0208]

图43~图72是用以对第2实施方式的半导体存储装置的制造方法进行说明的示意性剖视图或俯视图。图43、图45、图47、图51、图55、图59、及图63~图69表示与图40对应的平面。图44、图46、图48~图50、图52~图54、图56~图58、图60~图62、及图70~图72对应于图42的一部分所示的截面。

[0209]

第2实施方式的半导体存储装置基本上以与第1实施方式的半导体存储装置相同的方式制造。

[0210]

但,第2实施方式的半导体存储装置的制造方法中,在参照图12及图13所说明的工

序、或参照图15及图16所说明的工序中,例如图43及图44所示,在与绝缘层211对应的位置形成开口210a。此外,在与绝缘层221对应的位置形成开口220a。此外,在与导电层231对应的位置形成开口230a。此外,在与导电层241对应的位置形成开口240a。此外,在与绝缘层252对应的位置形成开口250a。此外,在与半导体层253对应的位置形成开口253a。此外,在与绝缘层261对应的位置形成开口260a。此外,在与绝缘层271对应的位置形成开口270a。这些开口210a、开口220a、开口230a、开口240a、开口250a、开口253a、开口260a及开口270a如图44所示在z方向上延伸,使沿z方向排列的多个绝缘层101及多个绝缘层102的x方向上的侧面露出。例如通过rie等进行该工序。

[0211]

接下来,例如图45及图46所示,在开口210a、开口220a、开口230a、开口240a、开口250a、开口253a、开口260a及开口270a的内部,形成牺牲层230b、牺牲层240b、牺牲层250b、牺牲层253b、牺牲层260b及牺牲层270b。例如通过cvd等进行该工序。

[0212]

接下来,例如图47及图48所示除去牺牲层250b。例如通过湿式蚀刻等进行该工序。

[0213]

接下来,例如图49所示形成半导体层250。该工序中,例如通过经由开口250a的湿式蚀刻等方法而将绝缘层102的一部分除去。此外,通过cvd等方法而形成半导体层250。

[0214]

接下来,例如图50所示,在开口250a的内部形成绝缘层251。例如通过cvd等方法进行该工序。

[0215]

接下来,例如图51及图52所示除去牺牲层240b。例如通过湿式蚀刻等进行该工序。

[0216]

接下来,例如图53所示形成半导体层240。该工序中,例如通过经由开口240a的湿式蚀刻等方法而将绝缘层102的一部分除去。此外,通过cvd等方法而形成半导体层240。

[0217]

接下来,例如图54所示,在开口240a的内部形成绝缘层242及导电层241。例如通过cvd等方法进行该工序。

[0218]

接下来,例如图55及图56所示除去牺牲层230b。例如通过湿式蚀刻等进行该工序。

[0219]

接下来,例如图57所示形成半导体层230。该工序中,例如通过经由开口230a的湿式蚀刻等方法而将绝缘层102的一部分除去。此外,通过cvd等方法而形成半导体层230。

[0220]

接下来,例如图58所示,在开口230a的内部形成导电层231。例如通过cvd等方法进行该工序。

[0221]

接下来,例如图59及图60所示除去牺牲层260b。例如通过湿式蚀刻等进行该工序。

[0222]

接下来,例如图61所示形成半导体层260。该工序中,例如通过经由开口260a的湿式蚀刻等方法而将绝缘层102的一部分除去。此外,通过cvd等方法而形成半导体层260。

[0223]

接下来,例如图62所示,在开口260a的内部形成绝缘层261。例如通过cvd等方法进行该工序。

[0224]

接下来,例如图63所示除去牺牲层270b。例如通过湿式蚀刻等进行该工序。

[0225]

接下来,例如图64所示形成绝缘层251。该工序中,例如通过经由开口270a的湿式蚀刻等方法而将绝缘层102的一部分除去。此外,通过热氧化处理等方法而使半导体层250的外周面的一部分氧化,由此形成绝缘层251。

[0226]

接下来,例如图65所示形成半导体层270。例如通过cvd等方法进行该工序。

[0227]

接下来,例如图66所示,在开口270a的内部形成绝缘层271。例如通过cvd等方法进行该工序。

[0228]

接下来,例如图67所示除去牺牲层253b。例如通过湿式蚀刻等进行该工序。

[0229]

接下来,例如图68所示,在开口253a的内部形成半导体层253。例如通过cvd等方法进行该工序。

[0230]

接下来,例如在参照图27及图28所说明的工序中,例如图69及图70所示除去牺牲层210b、220b。例如通过湿式蚀刻等进行该工序。

[0231]

接下来,例如在参照图29所说明的工序中,例如图71所示形成导电层210。此外,形成导电层220,但省略此图示。该工序中,例如通过经由开口210a、220a的湿式蚀刻等方法而将绝缘层102的一部分除去。此外,通过cvd等方法而形成导电层210、220。

[0232]

接下来,例如图72所示,在开口210a的内部形成绝缘层211。此外,在开口220a的内部形成绝缘层221,但省略此图示。例如通过cvd等方法进行该工序。

[0233]

[前置放大器电路pa的构成例]

[0234]

图40~图42所例示的前置放大器电路pa的构成只不过为例示,具体构成能够适当调整。

[0235]

例如,图40所例示的构成具备半导体层250、及与该半导体层250的外周面的一部分相接的半导体层253。另一方面,图73所例示的构成虽然基本上以与图40所例示的构成相同的方式构成,但具备半导体层350来代替半导体层250。此外,该构成不具备半导体层253。

[0236]

半导体层350基本上以与半导体层250相同的方式构成。但,在半导体层250的外周面设置有1个绝缘层251,半导体层250隔着该绝缘层251而与1个半导体层270对向。另一方面,在半导体层350的外周面设置有2个绝缘层251,半导体层350隔着这些绝缘层251而与2个半导体层270对向。所述构成中,能够使包含半导体层350的晶体管tr3的通道宽度变大,从而能够使接通电流增大。

[0237]

此外,例如图40所例示的构成具备半导体层250、及与该半导体层250相接的1个绝缘层252。另一方面,图74所例示的构成虽然基本上以与图40所例示的构成相同的方式构成,但具备半导体层450来代替半导体层250,并具备与该半导体层450相接的2个绝缘层252。

[0238]

半导体层450基本上以与半导体层250相同的方式构成。但,半导体层250的外周面的一部分沿着以1个绝缘层252的中心位置为中心的1个圆的圆周而设置。此外,半导体层250的外周面的其它部分设置在该圆的范围内。另一方面,半导体层450的外周面的一部分沿着分别以2个绝缘层252的中心位置为中心的2个圆的圆周而设置。此外,半导体层450的外周面的其它部分设置在该2个圆中的至少一个圆的范围内。此外,半导体层450与半导体层270的对向面积,大于半导体层250与半导体层270的对向面积。所述构成中,能够使包含半导体层450的晶体管tr3的通道长变大,从而能够抑制断开泄漏电流。

[0239]

此外,例如图75所示,前置放大器电路pa也可具备2个以上的电路元件pa,这些电路元件pa并联连接于节点n1、n2之间。电路元件pa也可分别具备参照图41所说明的晶体管tr1、tr2、tr3。所述情况下,例如图76所示,也可将上述任一构成的构成元件设置在2组以上的接线区域中,且并联连接于共通的导电层210、220之间。

[0240]

此外,以上例中,导电层210、220、及半导体层230、240、250、260、270的轮廓线的至少一部分,沿着以贯通这些半导体层的构成的中心位置为中心的圆的圆周而形成为曲线状。然而,所述构成只不过为例示,具体构成能够适当调整。例如图77的例子中,导电层210、220及半导体层230、240、250、260、270的轮廓线,沿着在x方向或y方向上延伸的直线形成。

在制造所述构成时,例如在参照图9及图10所说明的工序中能够进行接线区域的图案化而形成多个槽,在参照图11所说明的工序中,能够在这多个槽中形成氧化硅(sio2)等绝缘层。

[0241]

[其它实施方式]

[0242]

以上,对第1实施方式及第2实施方式的半导体存储装置进行了说明。然而,这些实施方式的半导体存储装置只不过为例示,具体构成、动作等能够适当调整。

[0243]

例如,第1实施方式及第2实施方式的半导体存储装置具备所谓的nand(not and,与非)闪速存储器。然而,第1实施方式及第2实施方式中例示的构成,也能够应用于nand闪速存储器以外的半导体存储装置。例如,也能够将第1实施方式及第2实施方式中例示的构成应用于具备一个或多个存储晶体管的构成,该存储晶体管是在多个存储层ml、ml2设置沿y方向延伸的半导体层,且以该半导体层为通道区域。此外,也能够将第1实施方式及第2实施方式中例示的构成应用于具备其它存储晶体管的构成。此外,也能够将第1实施方式及第2实施方式中例示的构成应用于其它存储器。

[0244]

此外,如参照图1等所说明,第1实施方式及第2实施方式的半导体存储装置具备:多个存储区块区域r

blk

,沿y方向排列;及1个接线区域r

hu

,对应于这多个存储区块区域r

blk

而设置。然而,接线区域r

hu

的配置能够适当调整。例如,第1实施方式及第2实施方式中,也可对应于多个存储区块区域r

blk

而设置多个接线区域r

hu

。所述情况下,也可省略位线区域r

bl

。

[0245]

此外,如参照图5~图7所说明,第1实施方式及第2实施方式的接触电极cc具备:部分192,在z方向上延伸;及大致圆盘状的部分193,连接于部分192的下端。然而,接触电极cc的构成能够适当调整。例如,第1实施方式及第2实施方式中,也可从接触电极cc中省略大致圆盘状的部分193。所述情况下,例如也可将多个接触电极cc的下端分别连接于在z方向上积层的多个导电层190的上表面。

[0246]

[其它]

[0247]

对本发明的几个实施方式进行了说明,但这些实施方式是作为例子提出的,并未意图限定发明范围。这些新颖实施方式可用其它各种方式实施,且可在不脱离发明主旨的范围内进行各种省略、替换、变更。这些实施方式或其变化包含在发明的范围或主旨中,并且包含在权利要求书所述的发明及与其相同的范围内。

[0248]

[符号的说明]

[0249]

110

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

半导体层

[0250]

120

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导电层

[0251]

130

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极绝缘层

[0252]

140

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导电层

[0253]

150

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导电层

[0254]

160

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

半导体层

[0255]

170

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导电层

[0256]

180

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导电层

[0257]rblk

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储区块区域

[0258]rhu

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

接线区域

[0259]rbl

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

位线区域。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1