半导体存储器的验证错误位量化电路和方法与流程

半导体存储器的验证错误位量化电路和方法

1.本技术是针对申请日为2021年03月15日,申请号为202110275767.5,发明名称为半导体存储器的验证错误位量化电路和方法的专利的分案申请。

技术领域

2.本发明涉及集成电路的制造领域,尤其涉及一种半导体存储器的验证错误位量化电路和方法。

背景技术:

3.为了克服二维存储器件的限制,业界已经研发并大规模量产了具有三维(3d)结构的存储器件,其通过将存储器单元三维地布置在衬底之上来提高集成密度。在3d nand存储器的生产制造中,需要对存储单元进行写入验证,以统计写入失败或错误的存储单元的个数,该过程被称为验证错误位计数(verify failbit count,vfc)。执行vfc的电路相应的被称为vfc电路,vfc电路的运行需要消耗3d nand存储器的功耗,为了节省功耗,需要对vfc电路进行优化设计。

技术实现要素:

4.因本发明所要解决的技术问题包括提供一种节省功耗的半导体存储器的验证错误位量化电路、方法以及包括该验证错误位量化电路的半导体存储器。

5.本发明为解决上述技术问题而采用的技术方案是一种半导体存储器的验证错误位量化电路,所述量化电路包括:模式选择单元和多个量化单元,其中,所述多个量化单元至少包括最高位量化单元和最低位量化单元;其中;

6.所述模式选择单元被配置为从至少两个大小不同的验证标准中选择一个作为所述验证错误位量化电路的验证标准信号;向与所述模式选择单元耦接的所述最高位量化单元传输所述验证标准信号;

7.所述最高位量化单元被配置为:接收所述验证标准信号;比较所述验证标准信号和验证错误位信号生成第一比较结果;根据所述第一比较结果输出第一使能信号;基于所述第一使能信号控制与所述最高位量化单元耦接的所述最低位量化单元开启或继续处于关断;

8.所述最低位量化单元被配置为:在基于所述第一使能信号开启时,比较所述验证错误位信号和第一基准信号生成第二比较结果;

9.其中,所述第一基准信号为所述量化电路所能量化的最低位标准信号,小于所述验证标准信号。

10.在本发明的一些实施例中,所述多个量化单元中还包括中间位量化单元;

11.所述最低位量化单元还配置为:根据所述第二比较结果输出第二使能信号;基于所述第二使能信号控制与所述最低位量化单元耦接的所述中间位量化单元开启或继续处于关断;

12.所述中间位量化单元被配置为:在基于所述第二使能信号开启时,比较所述验证错误位信号和第二基准信号生成第三比较结果;

13.其中,所述第二基准信号大于所述第一基准信号且小于等于所述验证标准信号。

14.在本发明的一些实施例中,所述量化电路还包括与所述中间位量化单元相邻地布置的中间较高位量化单元;

15.所述中间位量化单元还配置为:根据所述第三比较结果输出第三使能信号;基于所述第三使能信号控制所述中间较高位量化单元的开启或继续处于关断;

16.所述中间较高位量化单元被配置为:在基于所述第三使能信号开启时,比较所述验证错误位信号和第三基准信号生成第四比较结果;

17.其中,所述第三基准信号大于所述第二基准信号、小于等于所述验证标准信号。

18.在本发明的一些实施例中,当所述验证错误位信号小于所述验证标准信号时,所述最高位量化单元被配置为:基于所述第一使能信号控制所述最低位量化单元开启;

19.当所述验证错误位信号不小于所述验证标准信号时,所述最高位量化单元被配置为:基于所述第一使能信号控制所述最低位量化单元继续处于关断。

20.在本发明的一些实施例中,当所述验证错误位信号大于所述第一基准信号时,所述最低位量化单元被配置为:基于所述第二使能信号控制所述中间位量化单元开启;

21.当所述验证错误位信号不大于所述第一基准信号时,所述最低位量化单元被配置为:基于所述第二使能信号控制所述中间位量化单元继续处于关断。

22.在本发明的一些实施例中,在所述中间位量化单元开启时,所述最低位量化单元被关断。

23.在本发明的一些实施例中,当所述验证错误位信号大于所述第二基准信号时,所述中间位量化单元被配置为:基于所述第三使能信号控制所述中间较高位量化单元开启;

24.当所述验证错误信号弊大于所述第二基准信号时,所述中间位量化单元被配置为:基于所述第三使能信号控制所述中间较高位量化单元继续处于关断。

25.在本发明的一些实施例中,在所述中间较高位量化单元开启时,所述中间位量化单元被关断。

26.在本发明的一些实施例中,所述最高位量化单元还被配置为:根据所述第一比较结果输出第四使能信号;

27.所述最低位量化单元还包括第一或门,所述第一或门的输入端连接所述第四使能信号和所述第二使能信号,所述第一或门的输出作为所述最低位量化单元输出的所述第二比较结果。

28.在本发明的一些实施例中,所述最高位量化单元还被配置为:根据所述第一比较结果输出第四使能信号;

29.所述中间位量化单元还包括第二或门,所述第二或门的输入端连接所述第四使能信号和所述第三使能信号,所述第二或门的输出作为所述中间位量化单元输出的所述第三比较结果。

30.在本发明的一些实施例中,所述量化单元还包括码制转换单元,被配置为:将温度计编码转换成二进制码;其中,所述码制转换单元的输入从高位到低位依次为所述第一比较结果、所述第三比较结果和所述第二比较结果。

31.在本发明的一些实施例中,所述量化单元还包括累加器,被配置为:累加从所述码制转换单元获得的多个二进制码。

32.本发明为解决上述技术问题还提出一种半导体存储器,包括:存储阵列;及与所述存储阵列耦合的外围电路,其中;所述外围电路被控制为:控制所述存储阵列的存储操作;其中,所述外围电路被配置有包括如上任一所述的验证错误位量化电路。

33.本发明为解决上述技术问题还提出一种半导体存储器的验证错误位量化方法,应用于如上任一所述的验证错误位量化电路,所述方法包括:

34.模式选择单元从至少两个大小不同的验证标准中选择一个作为最高位的验证标准信号;向与所述模式选择单元耦接的最高位量化单元传输所述验证标准信号;

35.所述最高位量化单元接收所述验证标准信号;比较验证错误位信号和所述验证标准信号生成第一比较结果;根据所述第一比较结果输出第一使能信号;基于所述第一使能信号控制最低位量化单元开启或继续处于关断;

36.所述最低位量化单元在基于所述第一使能信号开启时,比较所述验证错误位信号和第一基准信号生成第二比较结果;其中,所述第一基准信号为所述量化电路所能量化的最低位标准信号,小于所述验证标准信号。

37.在本发明的一些实施例中,所述方法还包括:

38.所述最低位量化单元根据所述第二比较结果输出第二使能信号;基于所述第二使能信号用于控制中间位量化单元的开启或继续处于关断;

39.所述中间位量化单元在基于所述第二使能信号开启时,比较所述验证错误位信号和第二基准信号生成第三比较结果,其中,所述第二基准信号大于所述第一基准信号且小于等于所述验证标准信号。

40.在本发明的一些实施例中,所述方法还包括:

41.所述中间位量化单元还根据所述第三比较结果输出第三使能信号;基于所述第三使能信号控制中间较高位量化单元的开启或继续处于关断;以及

42.所述中间较高位量化单元在基于所述第三使能信号开启时,比较所述验证错误位信号和第三基准信号生成第四比较结果,其中,所述第三基准信号大于所述第二基准信号且小于等于所述验证标准信号,所述中间较高位量化单元与所述中间位量化单元相邻。

43.在本发明的一些实施例中,当所述验证错误位信号小于所述验证标准信号时,所述最高位量化单元基于所述第一使能信号控制所述最低位量化单元开启;

44.当所述验证错误位信号不小于所述验证标准信号时,所述最高位量化单元基于所述第一使能信号控制所述最低位量化单元继续处于关断。

45.在本发明的一些实施例中,当所述验证错误位信号大于所述第一基准信号时,所述最低位量化单元基于所述第二使能信号控制所述中间位量化单元开启;

46.当所述验证错误位信号不大于所述第一基准信号时,所述最低位量化单元基于所述第二使能信号控制所述中间位量化单元继续处于关断。

47.在本发明的一些实施例中,在所述中间位量化单元开启时,所述最低位量化单元被关断。

48.在本发明的一些实施例中,当所述验证错误位信号大于所述第二基准信号时,所述中间位量化单元基于所述第三使能信号控制所述中间较高位量化单元开启;

49.当所述验证错误信号弊大于所述第二基准信号时,所述中间位量化单元基于所述第三使能信号控制所述中间较高位量化单元继续处于关断。

50.在本发明的一些实施例中,在所述中间较高位量化单元开启时,所述中间位量化单元被关断。

51.在本发明的一些实施例中,所述方法还包括:

52.所述最高位量化单元根据所述第一比较结果输出第四使能信号;在所述验证错误位信号大于所述验证标准信号时,基于所述第四使能信号控制所述最低位量化单元、所述中间位量化单元和所述中间较高位量化单元都继续处于关断。

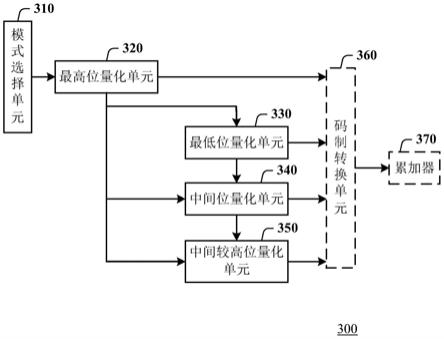

53.本发明实施例的验证错误位量化电路和方法可以从至少两个不同的验证标准中选择一个作为验证标准信号,可以灵活切换验证错误位量化电路的验证标准,并且采用最高位量化单元、最低位量化单元和中间位量化单元相互配合,根据验证错误位信号与不同的基准电流之间的大小关系,选择开启最合适的量化单元,关闭不必要的量化单元,使电路功耗获得的最大程度的节省。

附图说明

54.为让本发明的上述目的、特征和优点能更明显易懂,以下结合附图对本发明的具体实施方式作详细说明,其中:

55.图1是一种vfc电路的结构示意图;

56.图2a-2d是vfc电路中的量化单元的示例;

57.图3是本发明一实施例的验证错误位量化电路的模块框图;

58.图4a是本发明一实施例的验证错误位量化电路中的模式选择单元的结构示意图;

59.图4b是本发明一实施例的验证错误位量化电路中的最高位量化单元的结构示意图;

60.图5是本发明一实施例的验证错误位量化电路中的最低位量化单元的结构示意图;

61.图6是本发明一实施例的验证错误位量化电路中的中间位量化单元的结构示意图;

62.图7是本发明一实施例的验证错误位量化电路中的中间较高位量化单元的结构示意图;

63.图8是本发明一实施例的验证错误位量化电路中的使能信号控制电路的结构示意图;

64.图9a和9b是本发明一实施例的验证错误位量化电路中的中间位量化单元的结构示意图;

65.图10是本发明一实施例的验证错误位量化电路中的码制转换单元和累加器的结构示意图;

66.图11是本发明一实施例的半导体存储器的结构框图;

67.图12是本发明一实施例的半导体存储器的验证错误位量化方法的示例性流程图;

68.图13是本发明一实施例的验证错误位量化电路和方法的功耗测试结果示意图。

具体实施方式

69.为让本发明的上述目的、特征和优点能更明显易懂,以下结合附图对本发明的具体实施方式作详细说明。

70.在下面的描述中阐述了很多具体细节以便于充分理解本发明,但是本发明还可以采用其它不同于在此描述的其它方式来实施,因此本发明不受下面公开的具体实施例的限制。

71.如本技术和权利要求书中所示,除非上下文明确提示例外情形,“一”、“一个”、“一种”和/或“该”等词并非特指单数,也可包括复数。一般说来,术语“包括”与“包含”仅提示包括已明确标识的步骤和元素,而这些步骤和元素不构成一个排它性的罗列,方法或者设备也可能包含其他的步骤或元素。

72.在详述本发明实施例时,为便于说明,表示器件结构的剖面图会不依一般比例作局部放大,而且所述示意图只是示例,其在此不应限制本发明保护的范围。此外,在实际制作中应包含长度、宽度及深度的三维空间尺寸。

73.为了方便描述,此处可能使用诸如“之下”、“下方”、“低于”、“下面”、“上方”、“上”等等的空间关系词语来描述附图中所示的一个元件或特征与其他元件或特征的关系。将理解到,这些空间关系词语意图包含使用中或操作中的器件的、除了附图中描绘的方向之外的其他方向。例如,如果翻转附图中的器件,则被描述为在其他元件或特征“下方”或“之下”或“下面”的元件的方向将改为在所述其他元件或特征的“上方”。因而,示例性的词语“下方”和“下面”能够包含上和下两个方向。器件也可能具有其他朝向(旋转90度或处于其他方向),因此应相应地解释此处使用的空间关系描述词。此外,还将理解,当一层被称为在两层“之间”时,它可以是所述两层之间仅有的层,或者也可以存在一个或多个介于其间的层。

74.在本技术的上下文中,所描述的第一特征在第二特征之“上”的结构可以包括第一和第二特征形成为直接接触的实施例,也可以包括另外的特征形成在第一和第二特征之间的实施例,这样第一和第二特征可能不是直接接触。

75.此外,需要说明的是,使用“第一”、“第二”等词语来限定零部件,仅仅是为了便于对相应零部件进行区别,如没有另行声明,上述词语并没有特殊含义,因此不能理解为对本技术保护范围的限制。

76.在本文中所使用的术语“三维(3d)存储器件”是指在横向取向的衬底上具有竖直取向的存储单元晶体管串(在文中被称为“存储器串”,例如nand串)从而存储器串相对于衬底在竖直方向上延伸的半导体器件。如在本文中所使用的,术语“竖直/竖直地”表示标称垂直于衬底的横向表面。

77.在本文中所使用的属于“衬底”是指在其上添加后续材料层的材料。衬底本身可以被图案化。添加在衬底的顶部上的材料可以被图案化或可以保持未被图案化。此外,衬底可以包括多种半导体材料,例如硅、锗、砷化镓、磷化铟等。或者,衬底可以由非导电材料制成,例如玻璃、塑料或蓝宝石晶圆。

78.在本技术中所使用的术语“层”是指包括具有厚度的区域的材料部分。层可以在整个下层或上层结构上延伸,或者可以具有小于下层或上层结构范围的范围。此外,层可以是厚度小于连续结构的厚度的均匀或不均匀连续结构的区域。例如,层可以位于连续结构的顶表面和底表面之间或其处的任何一对水平平面之间。层可以水平地、垂直地和/或沿着锥

形表面延伸。衬底可以是层,其中可以包括一层或多层,和/或可以在其上、其上方和/或其下方具有一层或多层。层可以包括多个层。例如,互连层可以包括一个或多个导体和触点层(其中形成有触点、互连线和/或通孔)以及一个或多个电介质层。

79.本技术中使用了流程图用来说明根据本技术的实施例的系统所执行的操作。应当理解的是,前面或下面操作不一定按照顺序来精确地执行。相反,可以按照倒序或同时处理各种步骤。同时,或将其他操作添加到这些过程中,或从这些过程移除某一步或数步操作。

80.图1是一种vfc电路的结构示意图。参考图1所示,存储单元阵列110通过位线(bl)与页缓存器(page buffer)120相连接,页缓存器120和vfc电路130相连接。存储单元阵列110中包括多个存储单元(cell)。经过编程操作之后,页缓存器120输出电流信号至vfc电路130。如果存储单元通过了编程验证,则该电流信号为0;如果存储单元未通过编程验证,则存储单元对应的位线支路的页缓存器会输出对应的电流信号。vfc电路130通过对该电流信号进行统计,可以得到未通过编程验证的存储单元的个数并输出该个数。参考图1所示,vfc电路130中通常包括多个量化单元。

81.图2a-2d是vfc电路中的量化单元的示例。在该示例中,vfc电路总共包括14个量化单元,可以将来自页缓存器的验证错误位电流iverok_q分别与不同大小的基准电流进行比较,从而获得比较结果vercont《0:13》,根据该比较结果可以输出验证错误位的具体数量。图2a-2d示出了该14个量化单元中的4个量化单元。其中,图2a所示为基准电流ibase_0为1b的量化单元,其中1b表示为1份电流或1个标准电流。当验证错误位电流iverok_q大于基准电流ibase_0时,则输出vercont《0》=1,否则vercont《0》=0。图2b所示为基准电流ibase_1为2b的量化单元,其中2b表示为2份电流或2个标准电流。当验证错误位电流iverok_q大于基准电流ibase_2时,则输出vercont《1》=1,否则vercont《1》=0。图2c所示为基准电流ibase_12为25b的量化单元,其中25b表示为25份电流或25个标准电流。当验证错误位电流iverok_q大于基准电流ibase_12时,则输出vercont《12》=1,否则vercont《12》=0。图2d所示为基准电流ibase_13为27b的量化单元,其中27b表示为27份电流或27个标准电流。当验证错误位电流iverok_q大于基准电流ibase_13时,则输出vercont《13》=1,否则vercont《13》=0。

82.在图2a-2d所示的示例中,vfc电路的验证标准为27b,也就是该vfc电路所能比较的最大电流是27份标准电流,并且只能设置一种最大电流水平。在vfc电路运行期间,无论验证错误位电流iverok_q是否达到27份标准电流,各个量化单元都处于工作状态,如果在整个验证过程中,验证错误位电流iverok_q都没有达到27份标准电流,则具有较大基准电流的量化单元实际上消耗了多余的功耗。

83.图2a-2d所示仅为示例,vfc电路中量化单元的数量可以根据需要来设定。当量化单元数量较多时,可以将量化单元分组,每组中的量化单元同时工作,不同组分时工作,这样可以一定程度上降低对多余功耗的消耗,然而会降低运行速度,延长处理时间。

84.图3是本发明一实施例的验证错误位量化电路的模块框图。参考图3所示,本发明实施例的半导体存储器的验证错误位量化电路300包括依次连接的模式选择单元310、最高位量化单元320、最低位量化单元330和中间位量化单元340。其中,模式选择单元310适于从至少两个大小不同的验证标准中选择一个作为验证错误位量化电路300的验证标准信号;最高位量化单元320与模式选择单元310耦接,其被配置为比较验证标准信号和验证错误位

信号并生成第一比较结果,根据第一比较结果输出第一使能信号,该第一使能信号用于控制最低位量化单元330的开启或关断;最低位量化单元330被配置为,在最低位量化单元330被控制为开启的情况下,比较验证错误位信号和第一基准信号生成第二比较结果,根据第二比较结果输出第二使能信号,第二使能信号用于控制中间位量化单元340的开启或关断;以及,中间位量化单元340被配置为:在中间位量化单元340被控制为开启的情况下,比较验证错误位信号和第二基准信号生成第三比较结果,其中,第二基准信号大于第一基准信号,并且第二基准信号小于验证标准信号。

85.图4a是本发明一实施例的验证错误位量化电路中的模式选择单元的结构示意图。参考图4a所示,该模式选择单元410是一个反相器,其输入端411连接一个验证标准model_sel,其输出端412连接另一个验证标准model_selb。显然,model_sel和model_selb相互反向。若model_sel为1,则model_selb为0;若model_sel为0,则model_selb为1。通过控制该反相器的输入信号即可以使model_sel和model_selb中的一个为0,另一个为1。

86.图4a所示是从两个大小不同的验证标准中选择一个作为验证标准信号的实施例。对于具有多于两个验证标准的实施例来说,可以设计相应的模式选择单元410来实现从多于两个验证标准中选择一个的功能。

87.图4b是本发明一实施例的验证错误位量化电路中的最高位量化单元的结构示意图。参考图4b所示,最高位量化单元420包括两个输入端421、422和一个输出端423。其中,输入端421可以连接验证错误位信号verok_q,输入端422可以连接验证标准信号ver_s。最高位量化单元420适于比较该验证错误位信号verok_q和验证标准信号ver_s,并从输出端423输出第一比较结果vercont《13》。

88.本发明实施例对验证错误位信号verok_q和验证标准信号ver_s是电流信号或电压信号不做限制,可以理解,验证错误位信号verok_q和验证标准信号ver_s可以为同一种类型的信号,例如都为电压信号或都为电流信号。在优选的实施例中,验证错误位信号verok_q是一种来自页缓存器的电流信号,验证标准信号ver_s是对应于某一种验证标准的电流信号。该验证标准是该验证错误位量化电路的验证标准,用来限定该验证错误位量化电路所能量化的验证错误位电流的最大电流。

89.参考图4b所示,输入端422与两个验证标准model_sel和model_selb相连接,其中model_sel对应于27b,即27份标准电流,model_selb对应于10b,即10份标准电流。也就是说验证标准model_sel所对应的验证标准较大,验证标准model_selb所对应的验证标准较小。同一时刻,根据图4a所示的模式选择单元,model_sel和model_selb所对应的验证标准只有一个会被选中,作为从输入端422输入至最高位量化单元420的验证标准信号ver_s。

90.根据上述实施例,可以从多个验证标准中为验证错误位量化电路选择一个合适的验证标准信号ver_s。相比仅有一个验证标准的vfc电路,本发明实施例的验证错误位量化电路可以灵活地切换验证标准信号。

91.参考图4b所示,最高位量化单元420所输出的第一比较结果vercont《13》相当于最高位的量化结果。为了便于说明,图4b中的数字13对应于图2a-2d所示的示例,也就是验证错误位量化电路中总共包括14个量化单元。然而该数字13仅为示例,不用于限制本发明的验证错误位量化电路中的量化单元的数量,量化单元的具体数量可以根据需要来设定。根据图4所示的实施例,最高位量化单元420对应于验证错误位量化电路中基准信号最大的量

化单元,其输出的第一比较结果vercont《13》是最终输出结果的第14位,即最高位。

92.参考图4b所示,最高位量化单元420根据第一比较结果vercont《13》输出第一使能信号ab《max》。在该实施例中,第一使能信号ab《max》是第一比较结果vercont《13》的反信号,图4b中所标示的最高位量化单元420的输出信号a《max》等于第一比较结果vercont《13》。

93.图5是本发明一实施例的验证错误位量化电路中的最低位量化单元的结构示意图。参考图5所示,最低位量化单元510包括三个输入端511-513和一个输出端514。其中,验证错误位信号verok_q与输入端511相连接;最高位量化单元420输出的第一使能信号ab《max》与输入端512相连接,第一使能信号ab《max》用于控制最低位量化单元510的开启或关断;第一基准信号ibase_0与输入端513相连接。当最低位量化单元510开启时,最低位量化单元510比较验证错误位信号verok_q和第一基准信号ibase_0生成第二比较结果vercont《0》。在图5所示的实施例中,输出端514输出第二使能信号a《0》,当第四使能信号a《max》=1时,第二比较结果vercont《0》等于第二使能信号a《0》。

94.在图5所示的实施例中,第一基准信号ibase_0对应于1b,即1份标准电流。因此,最低位量化单元510对应于验证错误位量化电路中基准信号最小的量化单元,其输出的第二比较结果vercont《0》是最终输出结果的第0位,即最低位。

95.结合图4b和图5所示,当验证错误位信号verok_q小于验证标准信号ver_s时,最高位量化单元420输出的第一比较结果vercont《13》为0,则第一使能信号ab《max》为1。根据该第一使能信号ab《max》,最低位量化单元510开启,最低位量化单元510比较验证错误位信号verok_q和第一基准信号ibase_0。在一些实施例中,当验证错误位信号verok_q大于第一基准信号ibase_0时,第二比较结果vercont《0》为1,否则,第二比较结果vercont《0》为0。最低位量化单元310比较完成后输出第二使能信号a《0》,该第二使能信号a《0》用于控制中间位量化单元610的开启或关断。

96.参考图4b和图5所示,当验证错误位信号verok_q大于验证标准信号ver_s时,最高位量化单元420输出的第一比较结果vercont《13》为1,则第一使能信号ab《max》为0,最低位量化单元310关闭。在这种情况下,表示验证错误位信号verok_q大于验证标准信号ver_s,则该错误位计数为最大值,同时输出验证不通过信号(数值过大)。

97.根据上述的实施例,当验证错误位信号verok_q大于验证标准信号ver_s时,无需开启最低位量化单元510,从而节省了最低位量化单元510的额外功耗。

98.图6是本发明一实施例的验证错误位量化电路中的中间位量化单元的结构示意图。参考图6所示,中间位量化单元610包括三个输入端611-613和一个输出端614。其中,验证错误位信号verok_q与输入端611相连接;最低位量化单元510根据第二比较结果vercont《0》输出的第二使能信号a《0》与输入端612相连接,第二使能信号a《0》用于控制中间位量化单元610的开启或关断;第二基准信号ibase_1与输入端613相连接。当中间位量化单元610开启时,中间位量化单元610比较验证错误位信号verok_q和第二基准信号ibase_1生成第三比较结果vercont《1》。在图6所示的实施例中,输出端614输出第三使能信号a《1》,当第四使能信号a《max》=1时,第三比较结果vercont《1》等于第三使能信号a《1》。

99.在图6所示的实施例中,第二基准信号ibase_1对应于2b,即2份标准电流。在一些实施例中,中间位量化单元610对应于验证错误位量化电路中基准信号处于中间水平的量

化单元,其输出的第三比较结果vercont《1》是最终输出结果的第1位,与第0位和第2位相邻。

100.图6不用于限制第二基准信号ibase_1的具体大小。根据需要,可以设置第二基准信号ibase_1是大于第一基准信号ibase_0并小于验证标准信号ver_s的任意值。

101.结合图5-6所示,当验证错误位信号verok_q大于第一基准信号ibase_0时,最低位量化单元510输出第二比较结果vercont《0》为1,根据该第二比较结果vercont《0》输出第二使能信号a《0》也为1,使中间位量化单元610开启。中间位量化单元610比较验证错误位信号verok_q和第二基准信号ibase_1。在一些实施例中,当验证错误位信号verok_q大于第二基准信号ibase_1时,第三比较结果vercont《1》为1,否则,第三比较结果vercont《1》为0。

102.在这些实施例中,第二基准信号ibase_1大于第一基准信号ibase_0,并且第二基准信号ibase_1小于等于验证标准信号ver_s。

103.结合图4b所示,当验证标准信号ver_s对应于10份标准电流时,中间位量化单元610中的第二基准信号ibase_1的大小等于验证标准信号ver_s。该验证错误位量化电路可以只包括一个最高位量化单元420、一个最低位量化单元510和一个中间位量化单元610。在这些实施例中,该一个最低位量化单元510、一个中间位量化单元610和一个最高位量化单元420在结构上相邻并依次连接。

104.在一些实施例中,本发明的验证错误位量化电路可以包括多个中间位量化单元610。例如,包括依次连接的一个最高位量化单元420、一个最低位量化单元510和多个中间位量化单元610,这些中间位量化单元610的基准信号的大小位于第一基准信号ibase_0和验证标准信号ver_s之间,并且各个基准信号都不相同,从低位向高位逐渐增大。

105.在一些实施例中,本发明的验证错误位量化电路还可以包括中间较高位量化单元。图7是本发明一实施例的验证错误位量化电路中的中间较高位量化单元的结构示意图。参考图7所示,中间较高位量化单元710包括三个输入端711-713和一个输出端714。其中,验证错误位信号verok_q与输入端711相连接。在包括中间较高位量化单元710的实施例中,中间位量化单元610还根据比较结果输出第三使能信号a《1》与输入端712相连接,第三使能信号a《1》用于控制中间较高位量化单元710的开启或关断;第三基准信号ibase_2与输入端713相连接。当中间较高位量化单元710开启时,中间较高位量化单元710比较验证错误位信号verok_q和第三基准信号ibase_2生成第四比较结果vercont《2》。在图7所示的实施例中,输出端714输出使能信号a《2》,当第四使能信号a《max》=1时,第四比较结果vercont《2》等于使能信号a《2》。

106.其中,第三基准信号ibase_2大于第二基准信号ibase_1,并且第三基准信号ibase_2小于等于验证标准信号ver_s。在结构上,中间较高位量化单元710与中间位量化单元610相邻。

107.在图7所示的实施例中,第三基准信号ibase_2对应于12b,即12份标准电流。在一些实施例中,中间较高位量化单元710对应于验证错误位量化电路中基准信号处于中间水平的量化单元,其输出的第四比较结果vercont《2》是最终输出结果的第2位,与第1位和第3位相邻。

108.对于图7所示的实施例,由于第三基准信号ibase_2大于10b,因此如果中间较高位量化单元710被开启,则在图4b所示的最高位量化单元420中必定要选择较大的验证标准信

号ver_s,即验证标准信号ver_s对应于27b。

109.结合图6和图7,当验证错误位信号verok_q大于第二基准信号ibase_1时,中间位量化单元610输出的第三比较结果vercont《1》为1,第三使能信号a《1》也为1,中间较高位量化单元710开启。若验证错误位信号verok_q小于第二基准信号ibase_1,则中间位量化单元610输出的第三比较结果vercont《1》为0,第三使能信号a《1》也为0,中间较高位量化单元710关闭。

110.根据上述的实施例,当验证错误位信号verok_q大于第一基准信号ibase_0时,中间位量化单元610才会开启,当验证错误位信号verok_q大于第二基准信号ibase_1时,中间较高位量化单元710才会开启。也就是说,中间位量化单元610、中间较高位量化单元710都只在必要的时候才开启,在不必要的时候则关闭,从而可以节省功耗的消耗。

111.根据上述的实施例,最低位量化单元510表示多个量化单元中的最低位量化单元,中间位量化单元610表示多个量化单元中的较低位量化单元,中间较高位量化单元710表示多个量化单元中的较高位量化单元,最高位量化单元420表示多个量化单元中的最高位量化单元。

112.在一些实施例中,当中间位量化单元610开启时,最低位量化单元510关断,从而进一步节省功耗。

113.在一些实施例中,当中间较高位量化单元710开启时,中间位量化单元610关断,从而进一步节省功耗。

114.参考图4b所示,在一些实施例中,本发明的最高位量化单元420还根据第一比较结果vercont《13》输出第四使能信号a《max》。参考图5所示,该实施例的最低位量化单元510还包括第一或门515,该第一或门515的输入端连接该第四使能信号a《max》和第二使能信号a《0》,第一或门515的输出为第二比较结果vercont《0》。参考图6所示,该实施例的中间位量化单元610还包括第二或门615,该第二或门615的输入端连接第四使能信号a《max》和第三使能信号a《1》,第二或门615的输出为第三比较结果vercont《1》。

115.结合图3所示,最高位量化单元320除了与最低位量化单元330相连接之外,还分别与中间位量化单元340、中间较高位量化单元350相连接,以输出第四使能信号a《max》至每一个量化单元。可以理解,对于具有多个量化单元的实施例,最高位量化单元320都输出该第四使能信号a《max》至每一个量化单元。

116.根据上述的实施例,无论验证标准信号ver_s为何,当验证错误位信号verok_q大于验证标准信号ver_s时,第四使能信号a《max》=1,则无论最低位量化单元510和中间位量化单元610的比较结果为何,最后输出的第二比较结果vercont《0》和第三比较结果vercont《1》都是1。此时,由于第一使能信号ab《max》=0,最低位量化单元510被关断,相应地中间位量化单元610、中间较高位量化单元710也都被关断。

117.在一些实施例中,参考图7所示,中间较高位量化单元710还包括第三或门715,第三或门715的输入端连接第四使能信号a《max》和中间较高位量化单元710输出的下一位使能信号a《2》,第三或门715的输出为第四比较结果vercont《2》。这里的下一位使能信号a《2》可以用于作为与中间较高位量化单元710相邻的更高位的量化单元的使能信号。当a《max》=0时,vercont《2》=a《2》。如果不存在与中间较高位量化单元710相邻的更高位的量化单元,则a《2》不作为使能信号。

118.图8是本发明一实施例的验证错误位量化电路中的使能信号控制电路的结构示意图。该使能信号控制电路是量化电路中的一部分,可以作为最高位量化单元420、最低位量化单元510、中间位量化单元610和中间较高位量化单元710中的一部分电路。参考图8所示,以第一使能信号ab《max》为例,该使能信号控制电路包括至少三个晶体管t1、t2和t3,第一使能信号ab《max》与晶体管t1的基极相连接,验证错误位信号verok_q与晶体管t2的基极和漏极相连接。当第一使能信号ab《max》为0时,晶体管t1被关断,从而使该使能信号控制电路关断,例如使最低位量化单元关断;当第一使能信号ab《max》为1时,晶体管t1导通,从而使该使能信号控制电路导通,例如使最低位量化单元开启。当选择不同的验证标准信号ver_s时,第一使能信号ab《max》对应的验证错误位信号verok_q的大小不同,从而可以控制不同验证标准下的量化电路的开启和关断。

119.可以理解,图8所示仅为示例。可以根据本发明的思想,采用本领域技术根据使能信号来控制量化单元的开启或关断,且不限于上述电路结构。

120.图9a是本发明一实施例的验证错误位量化电路中的中间位量化单元的结构示意图。图9b是本发明一实施例的验证错误位量化电路中的中间较高位量化单元的结构示意图。该实施例的验证错误位量化电路中包括多个中间位量化单元和中间较高位量化单元,对应于基准信号处于中间水平的量化单元,中间位量化单元和中间较高位量化单元相邻。在图9a中用第i个量化单元表示中间位量化单元,在图9b中用第i+1个量化单元表示中间较高位量化单元。在该实施例中,假设量化单元按照基准信号从低到高的顺序依次连接,则第i个量化单元的基准信号小于第i+1个量化单元的基准信号。

121.参考图9a所示,该第i个量化单元主要包括比较器910。该比较器910的输入端911接第i-1个量化单元输出的使能信号a《i-1》,输入端912接基准信号vbias《i》,输出端913输出比较结果vercont《i》。其中,第i-1个量化单元可以是一个中间位量化单元,其所对应的基准信号小于第i个量化单元的基准信号,则第i个量化单元是中间较高位量化单元。

122.对于第i个量化单元来说,第i-1个量化单元输出的使能信号a《i-1》作为该第i个量化单元的使能信号。当验证错误位信号verok_q大于第i-1个量化单元的基准信号时,使能信号a《i-1》=1,使第i个量化单元开启。第i个量化单元比较验证错误位信号verok_q和基准信号vbias《i》,若验证错误位信号verok_q大于基准信号vbias《i》,则第i个量化单元的比较结果vercont《i》=1,并且使能信号a《i》=1。使能信号a《i》还与系统电压vdd一起通过与非门914与晶体管t4的基极相连接,使能信号a《i》=1时,与非门914输出为0,使晶体管t4关断,从而关断该第i个量化单元。

123.参考图9b所示,该第i+1个量化单元主要包括比较器920。该比较器920的输入端922接第i个量化单元输出的使能信号a《i》,输入端921接基准信号vbias《i+1》,输出端913输出比较结果vercont《i+1》。当第i个量化单元是中间位量化单元时,第i+1个量化单元是中间较高位量化单元。

124.当使能信号a《i》=1时,使晶体管t1导通,从而使该第i+1个量化单元被开启。第i+1个量化单元的基准信号vbias《i+1》大于第i个量化单元的基准信号vbias《i》。第i+1个量化单元进而比较验证错误位信号verok_q和基准信号vbias《i+1》,若验证错误位信号verok_q小于基准信号vbias《i+1》,则比较器920输出使能信号a《i+1》=0;否则输出使能信号a《i+1》=1。使能信号a《i+1》还与系统电压vdd一起通过与非门924与晶体管t4的基极相

连接,当使能信号a《i+1》=1时,与非门924输出为0,晶体管t4关断,从而关断该第i+1个量化单元。

125.根据图9a和9b所示的量化单元,可以根据验证错误位信号verok_q与基准信号的关系,仅开启多个量化单元中的一个,从而最大限度的节省功耗,提高效率。

126.在一些实施例中,本发明实施例的验证错误位量化电路还可以包括码制转换单元,该码制转换单元适于将温度计编码转换成二进制码,该码制转换单元的输入从高位到低位依次为第一比较结果、第三比较结果和第二比较结果。

127.在一些实施例中,本发明实施例的验证错误位量化电路还可以包括累加器,该累加器适于累加从码制转换单元获得的多个二进制码。

128.参考图3所示,在该验证错误位量化电路300中,每个量化单元都将比较结果输出至码制转换单元360,码制转换单元360将转换之后的二进制码传输至累加器370,由累加器370累加多个二进制码并输出最后的结果。

129.图10是本发明一实施例的验证错误位量化电路中的码制转换单元和累加器的结构示意图。参考图10所示,码制转换单元1010的输入端与前文所述的量化单元的多个比较结果相连接。根据前文所述的实施例,14个量化单元的比较结果可以用vercont《0:13》表示,其中,vercont《13》是最高位量化单元420输出的第一比较结果,表示最高位;vercont《0》是最低位量化单元510输出的第二比较结果,表示最低位;vercont《1:12》是多个中间位量化单元610输出的第三比较结果,其中还可以区分为较低位和较高位,较低位是中间位量化单元610输出的第三比较结果,较高位是中间较高位量化单元710输出的第四比较结果。

130.第一比较结果、第三比较结果和第二比较结果依次可以表示为温度计编码的高位到低位。对于包括第四比较结果的实施例,第一比较结果、第三比较结果、第四比较结果和第二比较结果依次可以表示为温度计编码的高位到低位。

131.在图10所示的实施例中,码制转换单元1010的输出端为一个6位的二进制码数据data《5:0》。图10不用于限定该二进制码的具体位数。

132.将二进制码数据data《5:0》输入到累加器1020。在一些实施例中,对一个半导体存储器可以进行多次验证错误位量化,每次都采用本发明的验证错误位量化电路来获得错误位计数。累加器1020可以将多次的错误位计数结果累加起来,作为该半导体存储器的最终计数结果。由于采用多次验证错误位量化,每次量化所需要的电流较小,从而更进一步降低了电路的功耗。

133.图11是本发明一实施例的半导体存储器的结构框图。参考图11所示,该半导体存储器1100包括存储阵列1110和外围电路1120。其中,该外围电路1120与存储阵列1110耦接,并且用于控制存储阵列1110的存储操作。该外围电路1120被配置有前文所述的验证错误位量化电路。因此前文关于验证错误位量化电路的说明内容和附图都可以用于说明本发明的半导体存储器。

134.图12是本发明一实施例的半导体存储器的验证错误位量化方法的示例性流程图。该验证错误位量化方法可以由前文所述验证错误位量化电路来执行,因此前文的附图和相关说明内容都可以用于说明该实施例的验证错误位量化方法,重复的内容将不再展开。参考图12所示,该实施例的验证错误位量化方法包括以下步骤:

135.步骤s1210:从至少两个大小不同的验证标准中选择一个作为验证标准信号。

136.该步骤可以由图4a所示的模式选择单元410来执行。

137.步骤s1220:比较验证错误位信号和验证标准信号并生成第一比较结果,根据第一比较结果输出第一使能信号,第一使能信号用于控制最低位量化单元的开启或关断。

138.该步骤可以由图4b所示的最高位量化单元420来执行。该步骤中的最低位量化单元可以是图5所示的最低位量化单元510。

139.步骤s1230:在最低位量化单元被控制为开启的情况下,最低位量化单元比较验证错误位信号和第一基准信号生成第二比较结果,根据第二比较结果输出第二使能信号,第二使能信号用于控制中间位量化单元的开启或关断。

140.该步骤中的中间位量化单元可以是图6所示的中间位量化单元610。

141.步骤s1240:在中间位量化单元被控制为开启的情况下,中间位量化单元比较验证错误位信号和第二基准信号生成第三比较结果,其中,第二基准信号大于第一基准信号,并且所述第二基准信号小于等于所述验证标准信号。

142.在一些实施例中,该方法还可以包括:

143.步骤s1250:在中间位量化单元被控制为开启的情况下,中间位量化单元还根据第三比较结果输出第三使能信号,第三使能信号用于控制中间较高位量化单元的开启或关断。

144.该步骤中的中间较高位量化单元可以是图7所示的中间位量化单元710。

145.步骤s1260:在中间较高位量化单元被控制为开启的情况下,中间较高位量化单元比较验证错误位信号和第三基准信号生成第四比较结果,其中,第三基准信号大于第二基准信号,并且第三基准信号小于等于验证标准信号,中间较高位量化单元与中间位量化单元相邻。

146.在一些实施例中,当验证错误位信号小于验证标准信号时,第一使能信号使最低位量化单元开启。

147.在一些实施例中,当验证错误位信号大于第一基准信号时,第二使能信号使中间位量化单元开启。

148.在一些实施例中,在中间位量化单元被控制为开启的情况下,最低位量化单元关断。

149.在一些实施例中,当验证错误位信号大于第二基准信号时,第三使能信号使中间较高位量化单元开启。

150.在一些实施例中,在中间较高位量化单元被控制为开启的情况下,中间位量化单元关断。

151.在一些实施例中,还包括根据第一比较结果输出第四使能信号,当验证错误位信号大于验证标准信号时,第四使能信号使最低位量化单元、中间位量化单元和中间较高位量化单元都关断。

152.根据本发明实施例的验证错误位量化方法,可以灵活的切换验证标准信号,根据实际的验证错误位信号的大小,仅开启必要的量化单元,关断不必要的量化单元,可以最大限度的降低验证错误位量化功能所消耗的功耗。

153.图13是本发明一实施例的验证错误位量化电路和方法的功耗测试结果示意图。其中包括位于三个坐标系中的三条曲线。在每个坐标系中,横轴是失败位的计数值,纵轴是电

流平均值,电流平均值越低表示该测试结果对应的功耗越低。其中曲线1310是目前的vfc电路时的功耗测试结果,其纵轴的单位为ma;曲线1320是采用本发明的验证错误位量化电路和方法,并且验证标准是25b时的功耗测试结果,其纵轴的单位为ma;曲线1330是采用本发明的验证错误位量化电路和方法,并且验证标准是10b时的功耗测试结果,其纵轴的单位为μa。参考图13所示,显然,曲线1330所示的功耗最小。下表一是根据图13中的曲线1310、1320、1330所获得的电流峰值(peak i)和电流平均值(average i)进行比较获得的结果。

154.表一:

[0155][0156]

其中,6(peak i)表示错误位计数=6时的电流峰值,11(peak i)表示错误位计数=11时的电流峰值,16(peak i)表示错误位计数=16时的电流峰值,16-6(average i)表示错误位计数在6-16之间的电流平均值。

[0157]

根据表一的结果,对于一个晶粒(die)中包括4个面(plane),每个面中包括8个单元(unit),当验证标准为25b时,每个单元的电流峰值可以节省0.364ma。当错位计数=11时,电流峰值总共可以节省11.648ma。当验证标准为10b时,每个单元的电流峰值可以节省1.2ma。当错位计数=16时,电流峰值总共可以节省38.4ma。

[0158]

相比于目前的vfc电路,当验证标准为25b时,电流平均值可以减少i_sp=10.5ua;当验证标准为10b时,电流平均值可以减少i_sp=47.7ua。

[0159]

虽然本发明已参照当前的具体实施例来描述,但是本技术领域中的普通技术人员应当认识到,以上的实施例仅是用来说明本发明,在没有脱离本发明精神的情况下还可作出各种等效的变化或替换,因此,只要在本发明的实质精神范围内对上述实施例的变化、变型都将落在本技术的权利要求书的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1