列控制电路以及存储装置的制作方法

本公开实施例涉及半导体,特别涉及一种列控制电路以及存储装置。

背景技术:

1、半导体存储器在许多电子系统中用来存储可在以后时间检索的数据。一般通过为半导体存储器提供命令、地址及时钟控制半导体存储器。半导体存储器可响应于命令执行各种存储器操作。例如,读取命令引起半导体存储器执行读取操作以从半导体存储器检索数据,且写入命令引起半导体存储器执行写入操作以将数据存储到半导体存储器。地址识别用于存取操作的半导体存储器位置,且时钟提供各种操作及数据提供的时序。为了提升内部数据吞吐量,方便同时读取更多的数据,可以将半导体存储器划分为多个存储体组(bg,bank group),每个存储体组可以独立读写数据。

技术实现思路

1、本公开实施例提供一种列控制电路以及存储装置,至少提供一种可应用于多个存储体组的列控制电路,保证列选择终止信号始终可以被目标列选择窗口信号采样到以得到目标列选择终止信号。

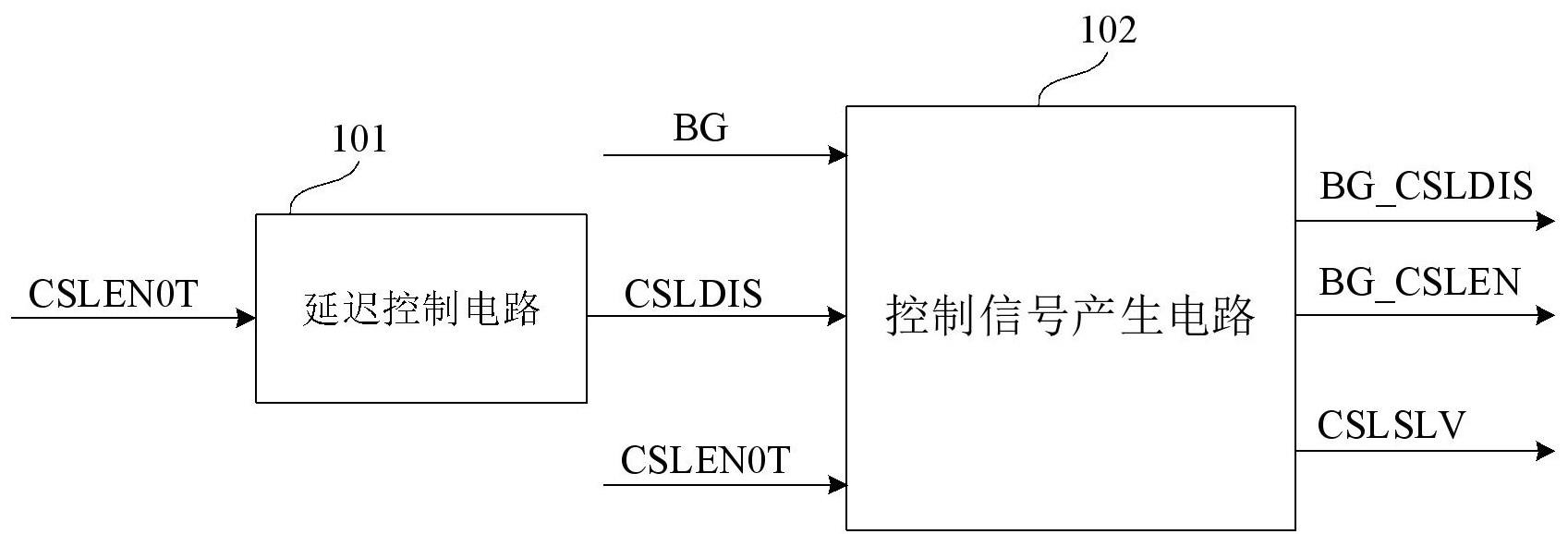

2、根据本公开一些实施例中,本公开实施例一方面提供一种列控制电路,包括:延迟控制电路,被配置为,接收列选择起始信号并对所述列选择起始信号进行延迟处理,生成并输出列选择终止信号,其中,所述列选择终止信号相对于所述列选择起始信号具有第一延迟量;控制信号产生电路,连接所述延迟控制电路,被配置为,接收所述列选择起始信号、所述列选择终止信号以及目标存储体组选择信号,并对所述列选择起始信号以及所述目标存储体组选择信号进行第一逻辑运算,以生成并输出目标列选择起始信号;基于所述列选择起始信号以及目标存储体组选择信号,以生成并输出目标列选择窗口信号,以及,对所述目标列选择窗口信号以及所述列选择终止信号进行第二逻辑运算,以生成并输出目标列选择终止信号;其中,所述目标列选择窗口信号相对于所述列选择起始信号具有第二延迟量,所述第二延迟量小于或等于所述第一延迟量,所述目标列选择窗口信号的有效时长大于或等于所述目标存储体组选择信号的有效时长。

3、在一些实施例中,所述控制信号产生电路包括:多个目标信号产生电路,每一所述目标信号产生电路与一存储体组相对应,每一所述存储体组与一所述目标存储体组选择信号相对应;与每一所述存储体组相对应的每一所述目标信号产生电路被配置为,接收所述列选择起始信号、所述列选择终止信号以及与所述存储体组相对应的所述目标存储体组选择信号,并输出与所述存储体组相对应的所述目标列选择起始信号、所述目标列选择窗口信号以及所述目标列选择终止信号。

4、在一些实施例中,每一所述目标信号产生电路包括:同步电路,被配置为,接收所述目标存储体组选择信号以及所述列选择起始信号,并响应于所述列选择起始信号对所述目标存储体组选择信号进行采样,生成并输出目标存储体组同步信号;其中,在所述目标存储体组选择信号处于有效状态,且所述列选择起始信号从无效变为有效时,输出处于有效状态的所述目标存储体组同步信号,而在所述目标存储体组选择信号处于无效状态,且所述列选择起始信号从无效变为有效时,输出处于无效状态的所述目标存储体组同步信号;起始信号产生电路,被配置为,接收所述目标存储体组选择信号以及所述列选择起始信号并进行与运算,生成并输出所述目标列选择起始信号;窗口信号产生电路,被配置为,接收所述目标存储体组同步信号以及触发信号,并基于所述触发信号对所述目标存储体组同步信号进行延迟处理,生成并输出所述目标列选择窗口信号;其中,所述触发信号相对于所述列选择起始信号具有第三延迟量,所述第三延迟量等于所述第二延迟量,所述触发信号处于有效状态的起始时刻开始,直至下一个触发信号的有效状态来到之前,所述目标列选择窗口信号有效;终止信号产生电路,被配置为,接收所述目标列选择窗口信号以及所述列选择终止信号并进行逻辑与运算,生成并输出所述目标列选择终止信号。

5、在一些实施例中,所述同步电路包括:第一d触发器,所述第一d触发器的数据输入端接收所述目标存储体组选择信号,时钟端接收所述列选择起始信号,正相输出端输出所述目标存储体组同步信号。

6、在一些实施例中,所述起始信号产生电路包括:第一与非门,两个输入端分别接收所述目标存储体组同步信号以及所述列选择起始信号;第一反相器,输入端连接所述第一与非门的输出端,输出端输出所述目标列选择起始信号。

7、在一些实施例中,所述窗口信号产生电路包括:第二d触发器,所述第二d触发器的数据输入端接收所述目标存储体组同步信号,所述第二d触发器的时钟端接收所述触发信号,所述第二d触发器的正相输出端输出所述目标列选择窗口信号。

8、在一些实施例中,所述终止信号产生电路包括:第二与非门,一输入端接收所述目标列选择窗口信号,另一输入端接收所述列选择终止信号;第二反相器,输入端连接所述第二与非门的输出端,输出端输出所述目标列选择终止信号。

9、在一些实施例中,所述触发信号为所述列选择起始信号的延迟信号;其中,所述第一延迟量和第三延迟量可调,且所述第三延迟量小于或等于所述第一延迟量的最小值。

10、在一些实施例中,所述延迟控制电路还被配置为,对所述列选择起始信号进行延迟处理,生成并输出所述触发信号。

11、在一些实施例中,所述第一延迟量与所述第二延迟量满足:t2≤tccd_s-2t,t2≤t1≤t2+tccd_s-2t,其中,t1为所述第一延迟量,t2为所述第二延迟量,2t为所述列选择起始信号的有效时长,t为1个时钟周期,tccd_s为所述目标存储体组选择信号的有效时长。

12、在一些实施例中,所述延迟控制电路还被配置为,接收延迟选择信号,并基于所述延迟选择信号,调节所述第一延迟量。

13、在一些实施例中,所述延迟控制电路包括:延迟电路,具有输入节点以及n个输出节点,被配置为,经由所述输入节点接收所述列选择起始信号,并经由n个所述输出节点输出n个延迟信号;其中,n个所述输出节点包括按照自然数递增顺序排布的第1输出节点至第n输出节点,且所述第1输出节点至所述第n输出节点各自输出的n个所述延迟信号相对于所述列选择起始信号的延迟量依次递增,n为大于等于2的自然数;选通电路,连接m个所述输出节点,具有选通输出端,被配置为,响应于所述延迟选择信号,选通m个所述输出节点中的一个与所述选通输出端之间的传输路径,以经由所述选通输出端输出所述列选择终止信号,m为小于等于n的自然数。

14、在一些实施例中,所述延迟电路包括:n个级联的第三d触发器,处于第一级的所述第三d触发器的数据输入端作为所述输入节点,前一级的所述第三d触发器的反相输出端连接后一级的所述第三d触发器的数据输入端;处于奇数位置的所述第三d触发器的时钟端均接收时钟信号,处于偶数位置的所述第三d触发器的时钟端均接收反相时钟信号,所述反相时钟信号与所述时钟信号互为反相信号,n个所述第三d触发器的反相输出端作为n个所述输出节点。

15、在一些实施例中,所述延迟电路还被配置为,响应于读操作命令,生成所述列选择起始信号,并向所述输入节点提供所述列选择起始信号。

16、在一些实施例中,所述延迟电路包括:偶数个级联的第四d触发器,处于第一级的所述第四d触发器的数据输入端接收所述读操作命令,前一级的所述第四d触发器的反相输出端连接后一级的所述第四d触发器的数据输入端;处于奇数位置的所述第四d触发器的时钟端均接收时钟信号,处于偶数位置的所述第四d触发器的时钟端均接收反相时钟信号,所述反相时钟信号为所述时钟信号的反相信号,且最后一级的所述第四d触发器的反相输出端连接所述输入节点并输出所述列选择起始信号。

17、在一些实施例中,所述选通电路包括:至少一个选通单元,所述选通单元连接m个所述输出节点中对应且相邻的两个所述输出节点;每一所述选通单元被配置为,响应于所述延迟选择信号,选通两个所述输出节点中的一个与所述选通单元的输出端之间的传输路径。

18、在一些实施例中,所述延迟选择信号包括p位控制码,每一所述选通单元接收对应且相邻的三个所述控制码,p为大于等于3的自然数,且相邻的两个所述输出节点输出的所述延迟信号的有效电平相反;每一所述选通单元包括:第三与非门,所述第三与非门的两个输入端分别接收三个所述控制码中对应的一个的反相信号;第三反相器,所述第三反相器的输入端连接一所述输出节点;第一与门,所述第一与门的两个输入端分别连接所述第三与非门的输出端以及所述第三反相器的输出端;第二与门,所述第二与门的一输入端接收三个所述控制码中的其余一个,另一输入端连接另一所述输出节点;第四与非门,所述第四与非门的输入端连接所述第一与门的输出端以及所述第二与门的输出端,所述第四与非门的输出端作为所述选通单元的输出端。

19、在一些实施例中,所述选通电路包括至少两个所述选通单元,且不同所述选通单元连接的所述输出节点不同;所述选通电路还包括:或门,所述或门的输入端连接每一所述选通单元的输出端,所述或门的输出端作为所述选通输出端。

20、根据本公开一些实施例,本公开实施例另一方面还提供一种存储装置,包括:多个存储体组,每一所述存储体组包括多个存储单元阵列,每一所述存储单元阵列包括多个存储单元,每一所述存储单元阵列与多个列选择开关管连接;如前述任一实施例提供的列控制电路,所述列选择开关管响应于对应的所述目标列选择起始信号开启,响应于所述目标列选择终止信号关闭。

21、本公开实施例提供的技术方案至少具有以下优点:

22、本公开实施例提供的列控制电路的技术方案中,目标列选择窗口信号相较于列选择起始信号具有第二延迟量,而列选择终止信号相较于列选择起始信号具有第一延迟量,且第二延迟量小于或等于第一延迟量,即目标列选择窗口信号的有效起始时刻早于列选择终止信号的有效起始时刻,或者,目标列选择窗口信号的有效起始时刻与列选择终止信号的有效起始时刻对齐,使得列选择终止信号的有效起始时刻可以被目标列选择窗口信号采样到;此外,目标列选择窗口信号的有效时长大于等于目标存储体组选择信号的有效时长,使得延迟量相对较大的列选择终止信号的有效结束时刻仍可以早于目标列选择窗口信号的有效结束时刻,从而使得列选择终止信号的有效结束时刻也可以被目标列选择窗口信号采样得到。

23、例如,即使存储装置的工作频率发生变化,列选择终止信号始终可以被目标列选择窗口信号采样得到。或者,第一延迟量或者第二延迟量发生变化,以使得目标列选择终止信号与目标列选择起始信号之间的时间间隔变化,本公开实施例提供的技术方案中,列选择终止信号始终可以被目标列选择窗口信号采样得到。

- 还没有人留言评论。精彩留言会获得点赞!