一种薄膜晶体管的制备方法与流程

[0001]

本发明属于集成电路制造和显示领域,具体涉及一种基于原子层淀积工艺的氧化物薄膜晶体管的制备方法。

背景技术:

[0002]

薄膜晶体管作为显示器像素单元的开关和驱动器件,对现代显示具有十分重要的作用。相较于氢化非晶硅和低温多晶硅材料,氧化物半导体材料由于较低的成本,较高的迁移率和较低的制备温度,成为新一代的薄膜晶体管沟道材料。现今显示技术朝着大面积和高分辨率的方向发展,因此需要提高晶体管的性能。采用高k材料作为栅极电介质是一种有效的方法,有利于改善薄膜晶体管的亚阈值摆幅和降低工作电压。对于氧化物薄膜晶体管的沟道层,常见的制备方法主要是基于物理气相淀积工艺,比如射频磁控溅射法、溶液法和脉冲激光淀积,但是物理气相淀积工艺生长的薄膜保型性和可重复性较差。对于氧化物薄膜晶体管的绝缘层,常见的制备方法是在400摄氏度左右通过等离子增强的化学气相淀积工艺,淀积氧化硅或者氮化硅,这超出了pet等柔性衬底的耐受温度,不利于制备柔性显示。

[0003]

原子层淀积工艺能够在较低的制备温度下,制备厚度和成分精确控制、大面积均匀、质量良好的的氧化物,氮化物,金属薄膜,因此和柔性衬底兼容。同时,原子层淀积工艺能够在各种基板和几何形状上沉积保形性良好的薄膜,因此与新兴的三维器件结构兼容。对于薄膜晶体管,其电学特性主要受沟道层,栅极绝缘体以及沟道和绝缘体之间的界面影响。其中,沟道和绝缘体的界面陷阱会引起阈值电压的不稳定和器件亚阈值摆幅的退火。因此,有必要研发基于原子层淀积工艺,具有良好沟道和绝缘体界面的薄膜晶体管。

技术实现要素:

[0004]

本发明目的在于提供一种基于原子层淀积工艺制备具有良好沟道和绝缘体界面的薄膜晶体管的方法。

[0005]

本发明的技术方案是:

[0006]

一种薄膜晶体管的制备方法,该薄膜晶体管淀积的衬底为带有热氧化硅的硅衬底、玻璃或者柔性衬底。薄膜晶体管从下到上依次为底栅电极、栅介质、有源层(沟道区)和源漏电极,栅介质位于底栅电极之上,有源层位于栅介质之上,源漏电极位于有源层之上。所有结构均采用原子层淀积工艺制备,并且淀积完栅介质后,不打开原子层淀积设备的腔室,相同温度下继续淀积有源层。具体包括以下步骤:

[0007]

1)在带有热氧化硅的硅衬底、玻璃或者柔性衬底上光刻栅电极图形,通过原子层淀积工艺淀积导电薄膜材料,然后光刻、刻蚀形成栅电极;

[0008]

2)通过原子层淀积工艺生长一层栅介质层,该栅介质层选自氧化铝和氧化铪等高k绝缘材料一种或者多种的组合,厚度为50-100纳米,原子层淀积绝缘材料过程中的载气为氮气,淀积温度为100℃到250℃;

[0009]

3)不开腔,原子层淀积工艺生长一层有源层,其中淀积温度与制备栅介质层工艺

采用的淀积温度相同;

[0010]

4)光刻源漏电极图形,定义源漏电极,通过原子层淀积工艺淀积导电薄膜材料,然后剥离形成源漏电极;

[0011]

5)光刻有源层图形,有源层和绝缘层共用相同的光刻胶掩膜,然后刻蚀出有源层和绝缘层,得到薄膜晶体管结构;

[0012]

6)对薄膜晶体管结构进行退火处理,最终得到薄膜晶体管器件。

[0013]

其中,步骤1)所生长的栅电极,采用pt、mo、cu、ito、azo等导电材料中的一种或者多种的组合。

[0014]

步骤3)所生长的有源层,采用zno、azo、inox、izo等金属氧化物半导体材料中的一种或者多种的组合。

[0015]

步骤4)所生长的源漏电极,采用pt、mo、cu、ito、azo等导电材料中的一种或者多种的组合。

[0016]

步骤6)中的退火,气氛为氧气或者空气,退火温度为150~250℃,退火时间为1~2小时。

[0017]

本发明的优点:

[0018]

本发明由于薄膜晶体管的有源层和绝缘层共用相同的光刻胶掩膜刻蚀图形化,因此减少了一次光刻,节约了工艺成本。薄膜晶体管全部采用原子层淀积的方法制备,可以在较低的温度下制备出质量良好、成分精确控制和大面积均匀的薄膜,满足柔性显示的需求。薄膜晶体管的栅介质采用高k材料,有利于改善薄膜晶体管的亚阈值摆幅和减少器件功耗。且薄膜晶体管的绝缘层和有源层采用相同的工艺手段,以及淀积温度相同,有利于减少沟道和绝缘体的界面陷阱和界面微变形,提高界面质量。

附图说明

[0019]

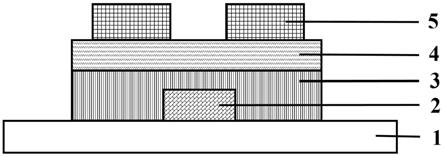

图1为本发明基于全原子层淀积工艺的薄膜晶体管的剖面示意图;

[0020]

图2为本发明基于全原子层淀积工艺的薄膜晶体管制备过程中的工艺步骤。

[0021]

上述图中1—衬底;2—底层栅电极;3—栅介质材料;4—有源区;5—顶层源、漏电极。

具体实施方式

[0022]

下面通过实例对本发明做进一步说明。需要注意的是,公布实例的目的在于帮助进一步理解本发明,但是本领域的技术人员可以理解:在不脱离本发明及所附权利要求的精神范围内,各种替换和修改都是可能的。因此,本发明不应局限于实例所公开的内容,本发明要求保护的范围以权利要求书界定的范围为准。

[0023]

本发明基于全原子层淀积工艺的薄膜晶体管淀积的衬底为带有热氧化硅的硅衬底、玻璃或者柔性衬底,如图1所示。底层栅电极位于衬底之上,栅介质位于栅电极之上,有源区位于栅介质之上,顶层源漏电极位于有源区之上,此结构为底栅薄膜晶体管结构。

[0024]

本发明的基于全原子层淀积工艺的薄膜晶体管的制作方法的具体实例由图2(a)至图2(f)所示,包括以下步骤:

[0025]

1.如图2(a)所示,衬底选用带有热氧化硅的硅衬底、玻璃或者柔性基底。

[0026]

2.如图2(b)所示,采用原子层淀积技术生长一层100纳米厚的pt、mo、cu、ito、azo等导电薄膜一种或者多种的组合,然后光刻、刻蚀形成底层栅电极。

[0027]

3.如图2(c)所示,利用原子层淀积技术生长氧化铝和氧化铪等高k绝缘材料一种或者多种的组合作为栅介质层,厚度为50-100纳米。原子层淀积绝缘材料过程中的载气为氮气,淀积温度为100℃到250℃。

[0028]

4.如图2(d)所示,不开腔利用原子层淀积技术生长一层30~50纳米厚的有源层,材料选择zno、azo、inox、izo等金属氧化物半导体材料中的一种或者多种的组合,淀积温度为100℃到250℃。

[0029]

5.如图2(e)所示,光刻源漏电极图形,定义源漏电极,通过原子层淀积工艺淀积100纳米厚的源漏电极,材料选择pt、mo、cu、ito、azo等导电材料中的一种或者多种的组合,然后剥离形成源漏电极。

[0030]

6.如图2(f)所示,光刻出有源区图形,有源层和绝缘层共用相同的光刻胶掩膜,用湿法刻蚀,一步刻蚀出有源层和绝缘层,得到薄膜晶体管结构。

[0031]

7.对薄膜晶体管结构进行退火处理,气氛为氧气或者空气,退火温度为150~250℃,退火时间为1~2小时,最终得到薄膜晶体管器件。

[0032]

虽然本发明已以较佳实施例披露如上,然而并非用以限定本发明。任何熟悉本领域的技术人员,在不脱离本发明技术方案范围情况下,都可利用上述揭示的方法和技术内容对本发明技术方案作出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1