发光二极管封装结构的制作方法

[0001]

本发明涉及一种发光二极管封装结构,特别是涉及一种可以提升中心照度的发光二极管封装结构。

背景技术:

[0002]

发光二极管(light emitting diode,led)是一种以半导体为发光材料的发光组件。发光二极管的发光效率日益进步,渐渐地扩大发光二极管的可应用范围,led灯具高效率及长寿命之特性,可大幅节省成本与降低耗能。

[0003]

然而,在超高功率户外led灯具的应用,目前仍有许多发展限制,若能利用新型的led灯具设计与研究技术,取代现有市售气体放电式头灯(high-intensity discharge,hid)灯具,将可加速led照明产业进入另一阶段。

[0004]

在现存技术中,有一类型的发光二极管封装结构是固晶、焊线后进行模塑封装,在此制程中,常常有金属线断裂的现象发生。因此,存在一种需求,设计新式的发光二极管封装结构,可以避免金属线断裂,同时又可以调整led的视角,提升led的中心照度。

技术实现要素:

[0005]

本发明所要解决的技术问题在于制程中保护金属线不断裂,又提升现有的发光二极管灯具的中心照度,针对现有技术的不足提供一种发光二极管封装结构及其制造方法。

[0006]

为了解决上述的技术问题,本发明所采用的其中一技术方案是,提供一种发光二极管封装结构,其包括一基板、一发光二极管芯片与一反射组件。基板具有一第一区域与一第二区域,基板包括设置于第二区域的至少一电极接垫。发光二极管芯片设置于基板上,发光二极管芯片具有一芯片上表面,芯片上表面具有一出光区与一打线区,出光区对应于第一区域上,打线区对应于第二区域上,发光二极管芯片包括位于打线区上的至少一电极接点,至少一电极接点通过至少一金属线与至少一电极接垫电连接。反射组件包括一第一部分与一第二部分,第一部分环绕发光二极管芯片,第二部分对应设置于第二区域上,并覆盖部分的第一部分及打线区。其中,第一部分具有一第一表面,且与芯片上表面齐平,更特定而言,是与出光区齐平。第二部分具有一第二表面,高于至少一金属线的最高点。

[0007]

更进一步地,发光二极管封装结构更包括含一透光组件,透光组件覆盖反射组件及出光区。

[0008]

更进一步地,发光二极管封装结构更包括一透光组件,设置第一表面与出光区上方。

[0009]

更进一步地,透光组件的上表面与第二表面齐平或不齐平。

[0010]

更进一步地,发光二极管封装结构更包括一荧光粉层,荧光粉层覆盖发光二极管芯片。

[0011]

更进一步地,荧光粉层覆盖出光区及第一表面。

[0012]

更进一步地,发光二极管封装结构更包括一透光组件,其覆盖荧光粉层。

[0013]

更进一步地,透光组件的上表面与第二表面齐平。

[0014]

更进一步地,发光二极管封装结构更包括一透光组件,覆盖荧光粉层及第二表面。

[0015]

更进一步地,荧光粉层进一步覆盖第二表面。

[0016]

更进一步地,发光二极管封装结构更包括一透光组件,覆盖对应于出光区及第一表面的荧光粉层。

[0017]

更进一步地,透光组件的上表面与对应于第二表面上的荧光粉层的上表面齐平。

[0018]

更进一步地,发光二极管封装结构更包括一透光组件,覆盖整体荧光粉层。透光组件的上表面是一平整面。

[0019]

更进一步地,反射组件包括反射粒子。第一部分与芯片等高而堆栈于其上的第二部分的厚度在50与100毫米之间或在150与200毫米之间。

[0020]

更进一步地,反射组件的侧面为一阶梯结构。第二部分的上表面呈一正方形、一长方形、一梯形或多边形。

[0021]

更进一步地,打线区与出光区的比值介于小于20%。

[0022]

更进一步地,出光区的其中一个侧边与打线区的其中一个侧边等长。

[0023]

更进一步地,发光二极管封装结构更包括一保护组件,设置于第二区域内,反射组件包覆保护组件,发光二极管芯片与保护组件为并联连接。

[0024]

更进一步地,发光二极管封装结构更包括一透镜,位于所述出光区之上。

[0025]

为了解决上述的技术问题,本发明所采用的另外一技术方案是,提供一种发光二极管封装结构的制造方法,其包括:提供一基板,并在基板定义一第一区域与一第二区域,基板包括设置于第二区域的至少一电极接垫;设置一发光二极管芯片于基板上,其中发光二极管芯片的一出光区与一打线区分别对应于第一区域与一第二区域,且所述发光二极管芯片包括至少一电极接点;通过至少一金属线电连接所述至少一电极接点与所述至少一电极接垫;提供一反射组件于基板与发光二极管芯片上,以覆盖至少一金属线,其中,芯片上表面具有一出光区与一打线区,第一部分环绕发光二极管芯片,第二部分对应于第二区域,并覆盖部分的第一部分及打线区;其中,第一部分具有一第一表面,与芯片上表面齐平,更特定而言,是与出光区平;第二部分具有一第二表面,高于至少一金属线的顶点。

[0026]

更进一步地,发光二极管封装结构的制造方法更包括一粘黏程序,利用一胶带粘黏于反射组件与发光二极管芯片上,再撕掉胶带以去除残余的反射组件。

[0027]

更进一步地,发光二极管封装结构的制造方法更包括提供一透光组件在反射组件及出光区上。

[0028]

更进一步地,发光二极管封装结构的制造方法更包括形成一透光组件在位于第一区域的反射组件的第一部分与出光区上方。

[0029]

更进一步地,发光二极管封装结构的制造方法更包括涂布一荧光粉层以覆盖发光二极管芯片及反射组件。

[0030]

更进一步地,发光二极管封装结构的制造方法更包括形成一透光组件以覆盖荧光粉层。

[0031]

更进一步地,发光二极管封装结构的制造方法更包括形成一透光组件在位于第一区域内的荧光粉层上。

[0032]

更进一步地,发光二极管封装结构的制造方法更包括一烘烤步骤以所述反射组

件。

[0033]

更进一步地,发光二极管封装结构的制造方法,反射组件为不透明封胶材料所构成。发光二极管封装结构的制造方法,在设置发光二极管芯片的步骤之后,更包括设置一保护组件于基板上。

[0034]

更进一步地,发光二极管封装结构的制造方法,其中在模塑(molding)反射组件之前,更包括一电浆清洗程序。

[0035]

本发明的其中一有益效果在于,本发明所提供的发光二极管封装结构及其制造方法除了可以有效防止漏光,且利用反射组件包覆金属线,达到保护金属线的效果,避免金属线断裂,更透过反射组件达到缩小视角的目的。

[0036]

为使能更进一步了解本发明的特征及技术内容,请参阅以下有关本发明的详细说明与附图,然而所提供的附图仅用于提供参考与说明,并非用来对本发明加以限制。

附图说明

[0037]

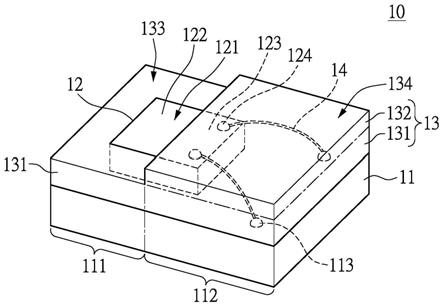

图1a为本发明实施例的发光二极管封装结构的示意图。

[0038]

图1b为本发明实施例的发光二极管封装结构的侧视图。

[0039]

图2a-图2b为本发明实施例的发光二极管封装结构包括透光组件的示意图。

[0040]

图2c-图2h为本发明发光二极管封装结构包括荧光粉层的立体示意图。

[0041]

图3a-图3e显示本发明在不同实施例的发光二极管封装结构的立体示意图。

[0042]

图4为本发明实施例提供一种发光二极管封装结构的制造方法的流程图。

[0043]

图5为本发明实施例的发光二极管封装结构的另一侧视图。

[0044]

图6a-图6k为本发明不同实施例中,发光二极管封装结构安装透镜的侧视图。

具体实施方式

[0045]

以下是通过特定的具体实施例来说明本发明所公开有关“发光二极管装置及其制造方法”的实施方式,本领域技术人员可由本说明书所公开的内容了解本发明的优点与效果。本发明可通过其他不同的具体实施例加以施行或应用,本说明书中的各项细节也可基于不同观点与应用,在不背离本发明的构思下进行各种修改与变更。另外,本发明的附图仅为简单示意说明,并非依实际尺寸的描绘,事先声明。以下的实施方式将进一步详细说明本发明的相关技术内容,但所公开的内容并非用以限制本发明的保护范围。

[0046]

应理解,虽然本文中可能使用术语第一、第二、第三等来描述各种组件或者信号,但这些组件或者信号不应受这些术语的限制。这些术语主要是用以区分一组件与另一组件,或者一信号与另一信号。另外,本文中所使用的术语“或”,应视实际情况可能包括相关联的列出项目中的任一个或者多个的组合。

[0047]

为了解释清楚,在一些情况下,本技术可被呈现为包括包含功能块之独立功能块,包含装置、装置组件、软件中实施之方法中的步骤或路由,或硬件及软件的组合。

[0048]

实施根据这些公开方法之装置可以包括硬件、韧体及/或软件,且可以采取任何各种形体。这种形体的典型例子包括笔记本电脑、智能电话、小型个人计算机、个人数字助理、投影机、建筑照明、娱乐装置等等。本文描述之功能也可以实施于外围设备或内置卡。透过进一步举例,这种功能也可以实施在不同芯片或在单个装置上执行之不同程序之电路板。

[0049]

该指令、用于传送这样的指令之介质、用于执行其之计算资源或用于支持这样的计算资源的其他结构,系为用于提供在这些公开中所述的功能之手段。

[0050]

本发明的实施例

[0051]

图1a为本发明实施例的发光二极管封装结构的示意图,图1b为本发明实施例的发光二极管封装结构的侧视图,如图1a与图1b所示,在本发明实施例中,发光二极管封装结构10主要包括基板11、发光二极管芯片12与反射组件13。

[0052]

进一步来说,基板11具有第一区域111与第二区域112,且包括设置在第二区域112的电极接垫113,电极接垫113的数量可为一或多个。发光二极管芯片12横跨设置在基板11的第一区域111与第二区域112上,详细来说,部分的发光二极管芯片12是设置在基板11的第一区域111内,而部分的发光二极管芯片12设置在第二区域112内。发光二极管芯片12具有芯片上表面121,且芯片上表面121包括出光区122与打线区123,芯片上表面121的出光区122对应于基板11的第一区域111,其打线区123对应于基板11的第二区域112,发光二极管芯片12在第二区域112所发出的光,会因为后续设置在基板11与发光二极管芯片12上方的反射组件13的遮蔽而无法传递至发光二极管封装结构10的表面。

[0053]

另外,发光二极管芯片12包括电极接点124,电极接点124位于芯片上表面121的打线区122上,且电极接点124通过金属线14电连接电极接垫113,电极接点124及金属线14的数量可各自为一或多个,且可对应于电极接垫113的数量,但不限于此。金属线14较佳为纯金线,但在此并不以此为限。

[0054]

反射组件13包括第一部分131与第二部分132,反射组件13的第一部分131环绕发光二极管芯片12,且第一部分131的第一表面133与发光二极管芯片12的芯片上表面121(出光区122)齐平,换句话说,反射组件13第一部分131的厚度与发光二极管芯片12的厚度大致相同,使反射组件13的第一部分131不会过高而遮蔽发光二极管芯片12的发光路径。

[0055]

另外,反射组件13的第一部分131环绕发光二极管芯片12进而防止发光二极管芯片12的侧向漏光,且可以控制发光二极管芯片12的发光视角。反射组件13的第二部分132对应设置于基板11的第二区域112上,反射组件13的第二部分132堆栈在第一部分131上,反射组件13的第二部分132覆盖位于基板11第二区域112的金属线14,反射组件13的第二部分132的第二表面134高于至少一金属线14的最高点,使反射组件13的第二部分132达到保护金属线14的目的。

[0056]

其中,反射组件13较佳是由不透明的封胶材料所构成,且反射组件13包括反射粒子,例如二氧化钛(tio2)或氮化硼(bn),进一步来说,反射组件13较佳是由硅或环氧树脂所构成,但在此并不以此为限。另外,基板11的第一部分131与芯片等高而堆栈于其上的第二部分132的厚度较佳在50与100毫米之间,或者,在不同实施例中,第一部分131与芯片等高而堆栈于其上的第二部分132的厚度在150与200毫米之间,但在此并不以此为限。

[0057]

图2a-图2b为本发明实施例的发光二极管封装结构包括透光组件的示意图,如图2a所示,在本发明的实施例中,发光二极管封装结构10更包括透光组件15,透光组件15设置于反射组件13上,且覆盖发光二极管芯片12的芯片上表面121的出光区122。详细来说,透光组件15覆盖反射组件13位于第一区域111中的第一部分131、位于第二区域112中的第二部分132,以及发光二极管芯片12的芯片上表面121的出光区122。

[0058]

或者,在不同实施例中,如图2b所示,透光组件15仅覆盖位于第一区域111中的第

一表面133与出光区122,且透光组件15的上表面151为一平整面,且可以如图2b所示,与第二部分132的第二表面134齐平。或者,在不同实施例中,透光组件15的上表面151可以与第二部分132的第二表面134不齐平,在此并不以此为限。

[0059]

另外,透光组件15的上表面151可以为一平整面,或者,透光组件15的上表面151可以是一球面以提升发光二极管芯片12的发光效率,但在此并不以此为限。另外,对于具有多个电极接点124的发光二极管芯片12而言,出光区122的一个侧边与打线区123的一个侧边等长,以利提供足够的面积来容纳所有的电极接点124,并且以单个第二部分132还覆盖所有的电极接点124及其等对应的金属线14。更佳地,为确保发光效率,打线区123需小于出光区122。较佳地,打线区123与出光区122的面积比值介于小于20%,过大有浪费发光面积之虞,过小则无法确保提供足够的面积以供电极接点124设置。

[0060]

图2c-图2h为本发明发光二极管封装结构包括荧光粉层的立体示意图。为了让发光二极管封装结构10可以发出不同颜色的光,在本发明的发光二极管封装结构10中,更可以包括一荧光粉(phosphor)层16,设置在发光二极管芯片12上。例如请参阅图2c,荧光粉层16设置在透光组件15及发光二极管芯片12上。或者,如图2d所示,荧光粉层16可设置在发光二极管芯片12芯片上表面121的出光区122以及反射组件13上,在一些实施例中,荧光粉层16可先覆盖在发光二极管芯片12芯片上表面121的出光区122以及反射组件13的第一部分131与第二部分132上方,然后再于荧光粉层16上方设置透光组件15。然在部分未示出的实施例中,荧光粉层16可仅覆盖于第一区域111上,或者甚至仅覆盖出光区122上,随后在第一区域111上或者在第一区域111上及第二区域112上设置透光组件15。

[0061]

或者,如图2e所示,荧光粉层16可先设置在位于第一区域111中的出光区122以及反射组件13上,然后再设置透光组件15在位于基板11第一区域11的荧光粉层16上方。另外,更可以如图2f所示,荧光粉层16覆盖位于基板11第一区域111的透光组件15以及反射组件13的第二部分132上,但在此并不以此为限。另外,在此需要说明的是,发光二极管大都可发出红光、绿光或蓝光,若是要发光二极管发出白光,较佳是以发光二极管配合荧光粉的方式呈现,举例来说,在蓝光发光二极管上涂抹黄色荧光粉层,黄色荧光粉层的材料举例可以是钇铝石榴石荧光粉、硅酸盐荧光粉或氮化物荧光粉,进而使发光二极管封装结构10发出白光。在不同实施例中,荧光粉层16更可以仅设置在位于第一区域111的透光组件15上,如图2g所示,或者荧光粉层16芯片上表面可以仅形成在位于芯片上表面121的出光区122的透光组件15上,如图2h所示,但在此并不以此为限。

[0062]

图3a-图3e显示本发明在不同实施例的发光二极管封装结构的立体示意图。进一步来说,在本发明的不同实施例中,反射组件13的第二部分132并不限于图2a-2f所示的态样,而可具有不同形状与体积。

[0063]

举例来说,如图3a-图3e所示,反射组件13的第二部分132的面积可以小于同样位于第二区域112中的第一部分131的面积,如图3a所示,而且反射组件13的第二部分132可以是梯形,如图3b所示,第二部分132也可以是不规则形状,如图3c所示,或者反射组件13的第二部分132可以是多边形,如图3d所示。

[0064]

需要说明的是,本发明之发光二极管封装结构10的反射组件13的第二部分132可以是任何形状,例如正方形、长方形或多边形等,只要第二表面134高于金属线14的最高点,反射组件13的第二部分132完全覆盖金属线14,都可以是本发明的反射组件13。

[0065]

参阅图4所示,图4为本发明实施例提供一种发光二极管封装结构的制造方法的流程图,并参考上述的发光二极管封装结构的组件标号,其至少包括下列几个步骤:

[0066]

在步骤s401中,提供基板11,并在基板11定义第一区域111与第二区域112,而在步骤s402中,设置发光二极管芯片12于基板11上。基板11包括设置于第二区域112的电极接垫113,基板11较佳可以是铝基板、铜基板或陶瓷电路板,但在此并不以此为限。第一区域111为发光二极管芯片12的发光区,第二区域112为发光二极管芯片12的发光牺牲区,也就是发光二极管芯片12在第二区域112的发光会因其他层级结构的遮蔽而无法传递至发光二极管封装结构10的表面上。

[0067]

另外,基板11包括电极接垫113,电极接垫113是用于与发光二极管芯片12电连接。另外,在设置发光二极管芯片的步骤中,更可以同时设置保护组件,保护组件较佳为齐纳二极管,且发光二极管芯片12与保护组件并联连接,以稳定电压避免突波电流导致发光二极管芯片的损坏。

[0068]

发光二极管芯片12的设置位置会横跨基板11的第一区域111与第二区域112,进一步来说,发光二极管芯片12的设置位置大部分位于基板11的第一区域111内,而一小部分位于基板11的第二区域112,以避免发光二极管芯片12过多区域位于第二区域112内,受到后续设置的层级结构的遮蔽,导致发光二极管封装结构10的发光效率不佳。

[0069]

发光二极管芯片12的芯片上表面121具有出光区122与打线区123,出光区122与打线区123分别对应于基板11的第一区域111与第二区域112,且发光二极管芯片12包括至少一电极接点124,至少一电极接点124对应于基板11的至少一电极接垫113。

[0070]

在步骤s403中,通过至少一金属线14电连接至少一电极接点124与至少一电极接垫113。金属线14可以是纯金线或铜线,任何金属可用于连接电极接点124与电极接垫113都可以是本发明的金属线,在此并不以此为限。在步骤s404中,提供一反射组件13于基板11与发光二极管芯片12上,以覆盖至少一金属线14。

[0071]

在本实施例中,反射组件13可以模塑方式(molding)包覆发光二极管芯片12,反射组件13为不透明封胶材料所构成,且具有反射粒子,以提升发光二极管芯片12的发光效率,并可以达到防止发光二极管芯片12的漏光,进一步缩小视角,使发光二极管芯片12的发光集中。

[0072]

进一步来说,在本发明中,可以利用具有高低落差的模具模塑反射组件13材料于发光二极管芯片12之间的间隙上,如图5所示,使反射组件13的侧表面具一阶梯结构。即上模具在对应于第二部分132的位置具有凹穴,当上模具压合在发光二极管芯片12上时,该凹穴可用来容置金属线14,随后当树脂材料填入时即会填满发光二极管芯片12的周边及凹穴,形成第一部分131及第二部分132。

[0073]

另外,在本发明的实施例中,更可以包括设置保护组件于基板11上,保护组件的设置可以是在基板11上的任何位置,且保护组件可以是齐纳二级体,但在此并不以此为限。而且,在完成设置发光二极管芯片12以及金属线14的制程步骤后,更可以包括一清洗步骤,例如,利用电浆处理(plasma treatment)以去除在基板11或发光二极管芯片12上的污染物。

[0074]

反射组件13包括第一部分131与第二部分132,反射组件13的第一部分131环绕发光二极管芯片12,第二部分132对应于基板11的第二区域112,且堆栈覆盖在第一部分131及打线区123上。反射组件13的第一部分131具有第一表面133,第一部分131的第一表面133与

发光二极管12的芯片上表面121(出光区122)齐平,第二部分132具有第二表面134,反射组件13的第二部分132高于金属线14的最高点,使第二部分132可以包覆金属线14。金属线14可通过打线接合(wire bonding)的方式,将电极接点124与电极接垫113电连接。在一些实施例中,当金属线14以反向打线的方式接合电极接点124与电极接垫113时,第一部分131与芯片等高而堆栈于其上的第二部分132的厚度较佳可在50与100毫米之间。或者,在不同实施例中,当金属线14以正向打线的方式接合电极接点124与电极接垫113时,第一部分131与芯片等高而堆栈于其上的第二部分132的厚度在150与200毫米之间,但在此并不以此为限。

[0075]

在完成步骤s404后,更可以粘黏程序将多余的反射组件13黏贴去除,进一步来说,以封胶形成反射组件13时,会有多余的胶料残留在发光二极管封装结构10的表面,通过将胶带黏贴于发光二极管芯片12上,然后再撕掉该胶带,可去除残余的胶料。

[0076]

而在设置反射组件13的步骤之后,更可将透光组件15设置在反射组件13与发光二极管芯片12上。其中,透光组件15是以模塑方式设置在反射组件13与芯片上表面121的出光区122上方,然后再将荧光粉层16涂布在透光组件15上。

[0077]

或者,在不同实施例中,可以先涂布荧光粉层16在反射组件13与发光二极管芯片12上,然后再将反射组件13设置在荧光粉层16上。另外,更可以提供透光组件15在反射组件的第一部分与发光二极管芯片12之芯片上表面121的出光区122上方,然后再将荧光粉层16涂布在透光组件15上。在一些较佳实施例中,涂布荧光粉层16的方式可包括以喷涂方式将荧光粉层16设置在透光组件15上。或者,可以先涂布荧光粉层16在反射组件13与发光二极管芯片12上,然后再将透光组件15设置在位于基板11第一区域111的荧光粉层16上,在此并不以此为限。

[0078]

另外,在设置反射组件13之后,本发明实施例提供的发光二极管封装结构的制造方法更可包括烘烤步骤,以达到固化反射组件13的目的,也可以在设置透光组件15之后,进行另一烘烤步骤以固化透光组件15。最后,更可以再进行一次电浆清洗程序,以去除在基板11或发光二极管芯片12上的污染物,再将制作完成的多个发光二极管封装结构切割成一个个发光二极管封装结构,完成发光二极管封装结构的制造方法。

[0079]

图6a为本发明又一实施例的发光二极管封装结构的侧视图,如图6a所示,在本发明实施例中,发光二极管封装结构60同样主要包括基板61、发光二极管芯片62与反射组件63,而在本实施例中,基板61、发光二极管芯片62或反射组件63的结构或设置位置都与上述的实施例相似,因此,相同之处在此不再赘述。其中,反射组件63同样包括第一部分631与第二部分632,反射组件63的第一部分631环绕发光二极管芯片62,第二部分632对应于基板61的第二区域612,且堆栈覆盖在第一部分631及发光二极管芯片62的打线区623上,反射组件63的第二部分632高于金属线64的最高点,使第二部分632可以包覆金属线64。在本实施例中,为了提高发光二极管封装结构的整体发光效率,更可以在反射组件63的第一部分631、第二部分632以及发光二极管芯片62的出光区622上,进一步堆栈一透镜67,而该透镜67较佳为一拱顶型(dome type)的透镜67,或者在不同实施例中,透镜67可以是一平面型的透镜67,如图6b所示。其中,透镜67较佳是由高分子材料所构成,高分子材料可以是硅氧树脂(silicone)或环氧树脂(epoxy),但在此并不以此为限。

[0080]

另外,在本实施例中,如图6a或图6b所示,反射组件63的第一部分631的宽度加上发光二极管芯片62的宽度与基板61的宽度相等,但在不同实施例中,反射组件63的第一部

分631的宽度加上发光二极管芯片62的宽度可以小于基板61的宽度,如图6c所示。换句话说,反射组件63的第一部分631环绕发光二极管芯片62的周围,但是在此实施例中,反射组件63的第一部分631并未填满在基板61上设置发光二极管芯片62以外的剩余表面,透镜67是堆栈在反射组件63的第一部分631、第二部分632、发光二极管芯片62的出光区622以及部分的基板61上,在此实施例中,透镜67的宽度同样与基板61的宽度相同。

[0081]

或者,在不同实施例中,可以在发光二极管芯片62的第一发光区622以及反射组件63的第二部分632上先设置透光组件(diffuser)65,然后在透光组件65以及反射组件63的第一部分631上设置透镜67,如图6d所示。或者,在不同实施例中,透光组件65除了覆盖在发光二极管芯片62的第一发光区622以及反射组件63的第一部分631外,更覆盖在反射组件63的第二部分632上,然后再于透光组件65上设置透镜67,如图6e所示。另外,在不同的实施例中,也可以在发光二极管芯片62的第一发光区622以及反射组件63的第二部分632上先设置荧光粉层66,直接在荧光粉层66上设置透镜67,如图6f所示,而无设置透光组件65。或者,在又一实施例中,在设置荧光粉层66之后,可先设置透光组件65于荧光粉层66上,然后再于透光组件65上设置透镜67,如图6g所示。透光组件65可以如图6g所示,覆盖在荧光粉层66的整个表面上,或者透光组件65可以仅覆盖在对应发光二极管芯片62的第一发光区622以及反射组件63的第二部分632的荧光粉层66上,如图6h所示,在此并不以此为限。

[0082]

在不同实施例中,荧光粉层66可以覆盖在反射组件63的第一部分631以及发光二极管芯片62的出光区622上,且荧光粉层66的厚度与反射组件63的第二部分632的厚度相同,使荧光粉层66与反射组件63的第二部分632齐平,再于反射组件63的第二部分632与荧光粉层66上设置透光组件65,最后将透光组件65上设置透镜67,如图6i所示。

[0083]

另外,在此需要说明的是,在图6c至图6i的实施例中,透镜67都是以拱顶型的透镜67作为范例,然而,在不同实施例中,拱顶型的透镜67也可以平面型的透镜67取代,或者也可以其他形状的透镜67取代,在此并不以此为限。举例来说,如图6b所示的发光二极管封装结构60的拱顶型的透镜67可以更改为平面型的透镜67,如图6j所示,其余如图6c至图6i的实施例中,其拱顶型的透镜67同样也可以改为平面型透镜67或其他类型的透镜67,在此不在一一赘述。进一步来说,如图6k所示,透镜67同样设置在反射组件63的第一部分631、第二部分632以及发光二极管芯片62的出光区622上,透镜67具有类似于拱顶型的透镜67的外型,其如同一圆帽状,同样可以达到提升发光二极管封装结构60的发光效率。另外,透镜67也可以是菲涅耳透镜(fresnel lens),其材质可以是玻璃或高分子材料(例如硅氧树脂(silicone)、环氧树脂(epoxy)、聚碳酸酯(polycarbonate,pc)、压克力(pmma)或聚氯乙烯(polyvinyl chloride,pvc))等。

[0084]

通过在本发明的发光二极管封装结构60上进一步安装透镜67,可以大幅度的提升发光二极管封装结构60的中心照度,举例来说,以图6a所示的发光二极管封装结构60为例,相较于无安装透镜67的发光二极管封装结构,图6a所示的发光二极管封装结构60的中心照度可以提升449.2%,或者,以图6k所示的具圆帽型的透镜67的发光二极管封装结构60,透镜67的尺寸大约900um x 900um,其中心照度可以提升435.7%。或者,当发光透镜67的尺寸大约是950um x 950um,发光二极管封装结构60的中心照度更可以略微提升至444.7%。因此,通过本发明的发光二极管封装结构60,除了可以防止漏光,更可以达到提升中心照度的效果。

[0085]

实施例的有益效果

[0086]

本发明的其中一有益效果在于,本发明所提供的发光二极管封装结构及其制造方法除了可以有效防止漏光,且利用反射组件包覆金属线,达到保护金属线的效果,避免金属线断裂,更透过反射组件达到缩小视角的目的。另外,在发光二极管封装结构上进一步安装透镜,可以达到提升中心照度的效果。

[0087]

以上所公开的内容仅为本发明的优选可行实施例,并非因此局限本发明的权利要求书的保护范围,所以凡是运用本发明说明书及附图内容所做的等效技术变化,均包括于本发明的权利要求书的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1