封装芯片电学性能的测试方法与流程

1.本发明一般涉及封装芯片测试技术领域,特别涉及一种封装芯片电学性能测试结构的制作方法、封装芯片电学性能的测试方法。

背景技术:

2.半导体集成电路芯片指内含集成电路的硅片,体积很小,常常是计算机或其他电子设备的一部分。芯片封装是将半导体集成电路芯片用绝缘材料进行打包,封装芯片的引脚通过印刷电路板与其他器件建立连接。为了保证出厂的芯片的可靠性,需要在出厂前对封装芯片进行测试以确保功能完整性等。

3.目前测量封装芯片电学性能的方法是在封装芯片的凸块(bump)区域添加大量的焊料(solder)进行短接,将封装芯片与电路板连接,电路板的另一侧设置测试用的导电结构,然后,用探针与导电结构接触并通过矢量网络分析仪测量封装芯片的电学性能。该测试方法中,由于封装芯片与电路板连接的区域上覆盖有绿油,使得焊料短接的效果差,导致电学性能测试结果存在偏差。

技术实现要素:

4.本发明的目的在于提供一种封装芯片电学性能的测试方法,增强凸块的短接效果,从而增强凸块与探针的接触性能,提高测试的可靠性。

5.本技术的一实施例中公开了一种封装芯片电学性能测试结构的制作方法,包括:

6.提供第一晶圆和第二晶圆;

7.分别在所述第一晶圆和所述第二晶圆上形成顶层金属层;

8.分别在所述第一晶圆和所述第二晶圆的部分所述顶层金属层上形成凸块;

9.去除所述第一晶圆中位于所述凸块下方之外的顶层金属层,完全保留所述第二晶圆中的顶层金属层;

10.分别封装所述第一晶圆和所述第二晶圆形成第一颗粒和第二颗粒,所述第二颗粒作为测试结构,所述第二颗粒的电学性能作为所述第一颗粒电学性能的参考。

11.在一优选例中,在部分所述顶层金属层上形成凸块的步骤,进一步包括:

12.在所述顶层金属层上沉积图案化的光阻,所述图案化的光阻暴露出部分的顶层金属层;

13.采用电镀沉积工艺在所述暴露的部分顶层金属层上生长所述凸块;

14.去除所述图案化的光阻。

15.在一优选例中,所述凸块包括铜、镍、锡、银中的一种或其任意组合。

16.在一优选例中,采用溅射工艺生长所述顶层金属层,所述顶层金属层包括铜、金、银、镍、锡中的一种或其任意组合。

17.在一优选例中,所述第一晶圆内包括有晶体管、互连结构和控制电路。

18.在一优选例中,分别封装所述第一晶圆和所述第二晶圆形成第一颗粒和第二颗粒

的步骤,进一步包括:采用相同的封装工艺封装所述第一晶圆和所述第二晶圆。

19.本技术的另一实施例还公开了一种封装芯片电学性能的测试方法,采用前文所述的制作方法制作的测试结构,包括:

20.将所述测试结构设置于基板上,所述测试结构的凸块与所述基板连接,所述基板相对于所述测试结构的另一侧设置有用于测试的导电结构;

21.采用探针与所述导电结构接触,测试所述测试结构的电学性能。

22.在一优选例中,所述电学性能包括电阻性能和电感性能。

23.在一优选例中,所述基板为印刷电路板、柔性电路板、陶瓷基板或有机基板。

24.在一优选例中,所述导电结构包括锡球。

25.相对于现有技术,本技术至少具有以下有益效果:

26.本技术中,采用第二颗粒作为测试结构,第二颗粒表面具有完整的顶层金属层,顶层金属层与凸块的连接性能更好,使得测试过程中短接良好,从而提高测试的可靠性。

27.此外,本技术的第二颗粒与作为产品的第一颗粒(具有控制电路等)采用相同的金属层工艺和封装工艺,没有额外增加工艺,成本较低。

附图说明

28.参考以下附图描述本技术的非限制性和非穷举性实施例,其中除非另有说明,否则相同的附图标记在各个附图中指代相同的部分。

29.图1示出了本技术一实施例中封装芯片电学性能测试结构的制作方法的流程图。

30.图2示出了本技术一实施例中第一晶圆和第二晶圆的示意图。

31.图3示出了本技术一实施例中形成聚酰亚胺层和顶层金属层的示意图。

32.图4示出了本技术一实施例中形成图案化的光阻和凸块的示意图。

33.图5示出了本技术一实施例中去除图案化的光阻和顶层金属层的示意图。

34.图6示出了本技术一实施例中凸块进行回流焊工艺的示意图。

35.图7示出了本技术一实施例中封装芯片电学性能的测试方法的流程图。

36.图8示出了本技术一实施例中电学性能测试过程的示意图。

具体实施方式

37.现在将描述本技术的各个方面和示例。以下描述提供了用于彻底理解和实现这些示例的描述的具体细节。然而,本领域技术人员将理解,可以在没有许多这些细节的情况下实践本技术。

38.另外,可能未详细示出或描述一些众所周知的结构或功能,以便简明扼要并避免不必要地模糊相关描述。

39.在下面给出的描述中使用的术语旨在以其最广泛的合理方式解释,即使它与本技术的某些特定示例的详细描述一起使用。以下甚至可以强调某些术语,然而,任何旨在以任何受限制的方式解释的术语将在本详细描述部分中明确且具体地定义。

40.本技术的第一实施例中公开了一种封装芯片电学性能测试结构的制作方法,图1示出了测试结构的制作方法的流程图,图2至图6示出了各步骤对应的结构示意图。该方法包括:

41.步骤s101,提供第一晶圆(wafer)100和第二晶圆200,参考图2所示,所述晶圆指的是可以在其中形成器件的衬底,例如,硅衬底、锗硅衬底、砷化镓衬底等等,所述器件可以指的是cmos电路,例如包括一个或多个晶体管、互连结构和控制电路等等,用于实现特定功能的结构。所述晶圆中还可以形成有其他器件结构,例如放大器、数/模转换器、模拟处理电路和/或数字处理电路、接口电路等,形成这些器件结构的方法均可以为cmos工艺。其中,所述第一晶圆100用于形成正常的芯片产品,即在第一晶圆100中形成器件,所述第二晶圆200用于测试,即在第二晶圆200中不形成器件,仅形成需要实现测试的金属层和凸块,根据第二晶圆的测试结果衡量芯片产品的电学性能。所述第一晶圆100和所述第二晶圆200中分别形成焊盘112,212以及钝化层114,214,所述钝化层114,214分别部分覆盖所述焊盘112,212,所述钝化层114,214为氮化硅(sin)。

42.在一实施例中,参考图3所示,分别在所述衬底110,210上形成聚酰亚胺(polyimide)层116,216,所述聚酰亚胺层116,216分别用于释放下方衬底110,210的应力。应当理解,所述聚酰亚胺层116,216是可选的,在其他实施例中,也可以不形成聚酰亚胺层116,216。

43.步骤s103,继续参考图3所示,分别在所述第一晶圆100和第二晶圆200上形成顶层金属层118,218。本领域技术人员应当公知的是,在芯片工艺制程中,需要形成多层金属层,例如,3至5层金属层,以实现电连接。本实施例中,所述顶层金属层指的是工艺制程中的最上层金属层或凸块下方的金属层(under bump metellization)。在一实施例中,采用溅射(sputtering)工艺形成所述顶层金属层。所述顶层金属层118,218可包括铜(cu)、钛(ti)、金(au)、银(ag)、镍(ni)、锡(sn)中的一种或其任意组合,例如,溅射铜或钛形成所述顶层金属层。所述顶层金属层118,218的厚度可以为300nm~600nm,例如300nm、400nm、600nm等。

44.步骤s105,参考图4所示,分别在部分所述顶层金属层118,218上形成凸块(bump)122,222。在一实施例中,步骤s105中,在在部分所述顶层金属层上形成凸块的步骤,进一步包括:

45.参考图4所示,分别在所述顶层金属层118,218上沉积图案化的光阻(pr)120,220,所述图案化的光阻120,220暴露出部分所述顶层金属层118,218,同时暴露出所述焊盘112,212。应当理解,图案化的光阻可以采用本领域已知或未来可知的工艺形成,在此不做赘述。

46.之后,采用电镀沉积(ecd)工艺分别在所述图案化的光阻未覆盖的所述顶层金属层118,218上生长凸块122,222。在一实施例中,所述凸块122,222可包括铜、镍、锡、银中的一种或其任意组合。所述凸块122,222的厚度可以为38μm~95μm,例如,40μm、50μm、60μm、65μm、78μm、86μm、90μm等。例如,凸块122,222包括依次层叠的第一金属层1220,2220、第二金属层1222,2222和第三金属层1224,2224,所述第一金属层1220,2220为铜金属层。所述第二金属层1222,2222为镍金属层。所述第三金属层1224,2224为锡银焊料层。

47.在另一实施例中,所述凸块122,222包括两层金属层,例如,第一金属层和第二金属层,所述第一金属层为镍金属层,所述第二金属层为焊料层,例如,不含铅焊料层(lf solder)。

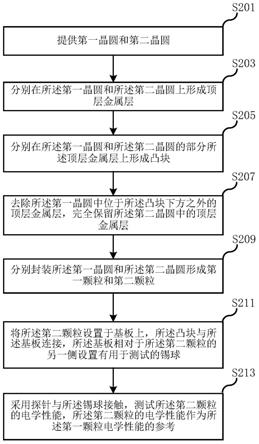

48.接着,参考图5所示,去除所述图案化的光阻120,220,例如,采用等离子体蚀刻工艺或灰化工艺去除所述光阻120,220。

49.步骤s107,继续参考图5所示,去除所述第一晶圆100中位于所述凸块122下方之外

的顶层金属层118,完全保留所述第二晶圆200中的顶层金属层218。本实施例中,去除所述第一晶圆100中位于所述凸块122下方之外的顶层金属层118,第一晶圆100中未去除的顶层金属层118用于实现互连,第二晶圆200中的顶层金属层218不需要实现互连,仅用于电学性能测试,因而不需要去除。本实施例中,可以采用湿法蚀刻工艺去除所述顶层金属层。

50.本实施例中,由于第二晶圆中的顶层金属层是未经蚀刻的金属层,因此第二晶圆中的顶层金属层的表面平整,该顶层金属层与凸块之间的接触性能良好。

51.参考图6所示,在一实施例中,所述制作方法还包括对所述凸块122,222进行回流焊(reflow)工艺。

52.步骤s109,分别封装所述第一晶圆100和所述第二晶圆200形成第一颗粒(die)和第二颗粒,所述第二颗粒作为测试结构,所述第二颗粒的电学性能作为所述第一颗粒电学性能的参考。在一实施例中,在步骤s109中,分别封装所述第一晶圆和所述第二晶圆形成第一颗粒和第二颗粒的步骤,进一步包括:采用相同的封装工艺封装所述第一晶圆和所述第二晶圆。本实施例中,可以采用本领域技术人员公知的技术对晶圆进行封装,在此不做赘述。本实施例中,第二颗粒的结构参考图8中200’所示,第二颗粒200’包括衬底210’、位于所述衬底210’上的顶层金属层218’以及与顶层金属层连接的凸块222’。本实施例中,第二颗粒与作为芯片产品的第一颗粒(具有控制电路等)采用相同的金属层工艺和封装工艺,没有额外增加工艺,实现测试的成本较低。

53.本技术的第二实施例还公开了一种封装芯片电学性能的测试方法,图7示出了封装芯片电学性能的测试方法的流程图,步骤s201至s209与前文所述的s101至s109相似,该方法包括:

54.步骤s201,提供第一晶圆和第二晶圆;

55.步骤s203,分别在所述第一晶圆和所述第二晶圆上形成顶层金属层;

56.步骤s205,分别在所述第一晶圆和所述第二晶圆的部分所述顶层金属层上形成凸块;

57.步骤s207,去除所述第一晶圆中位于所述凸块下方之外的顶层金属层,完全保留所述第二晶圆中的顶层金属层;

58.步骤s209,分别封装所述第一晶圆和所述第二晶圆形成第一颗粒和第二颗粒;

59.步骤s211,将所述第二颗粒设置于基板上,所述凸块与所述基板连接,所述基板相对于所述第二颗粒的另一侧设置有用于测试的导电结构。在一实施例中,所述基板为印刷电路板(pcb)、柔性电路板(fpc)或有机基板,所述基板上设置有用于电气连接的焊盘(pad),所述凸块与所述基板的焊盘连接。在一实施例中,采用封装胶连接所述测试结构与所述基板,用于补强颗粒与基板之间的连接。在一实施例中,所述导电结构为锡球。

60.步骤s213,采用探针与所述导电结构310接触,测试所述第二颗粒200’的电学性能,所述第二颗粒200’的电学性能作为所述第一颗粒电学性能的参考。在一实施例中,所述电学性能包括电阻性能和电感性能。

61.图8示出了一实施例中电学性能测试过程的示意图。第二颗粒200’倒置与基板300上,凸块222’与基板300上的焊盘(图中未示出)电气连接,凸块222’与基板300之间设置有封装胶(图中未示出),基板300相对于所述第二颗粒200’的另一侧设置有锡球310。测试电学性能时,采用两个探针(图中箭头所示)分别与锡球310接触,其中一个探针的一端接地端

(g),另一个探针的一端接信号端(s),采用矢量网络分析仪分别测试颗粒的电阻值和电感值,矢量网络分析仪采用本领域技术人员公知的方法测试电阻值和电感值,在此不做赘述。下表1中给出了本技术与现有的测试方法测量的电阻值(r)与电感值(h)的结果,下表1中仅以信号dac1为例进行列举,分别测试了不同的6个样品,当然本领域技术人员可以测试qaca13等其他的信号。从下表1中可以看出,本技术的测试方法对于电阻值测试的改善非常明显,电阻值的标准差由38.5667降低到0.0568,同时对于电感值的测试也有一定程度的改善。

62.表1电学性能的测试结果

[0063][0064]

需要说明的是,在本专利的申请文件中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。本专利的申请文件中,如果提到根据某要素执行某行为,则是指至少根据该要素执行该行为的意思,其中包括了两种情况:仅根据该要素执行该行为、和根据该要素和其它要素执行该行为。多个、多次、多种等表达包括2个、2次、2种以及2个以上、2次以上、2种以上。

[0065]

在本说明书提及的所有文献都被认为是整体性地包括在本技术的公开内容中,以便在必要时可以作为修改的依据。此外应理解,以上所述仅为本说明书的较佳实施例而已,并非用于限定本说明书的保护范围。凡在本说明书一个或多个实施例的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本说明书一个或多个实施例的保护范围之内。

[0066]

在一些情况下,在权利要求书中记载的动作或步骤可以按照不同于实施例中的顺序来执行并且仍然可以实现期望的结果。另外,在附图中描绘的过程不一定要求示出的特定顺序或者连续顺序才能实现期望的结果。在某些实施方式中,多任务处理和并行处理也

是可以的或者可能是有利的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1