半导体功率器件的制作方法

1.本发明属于半导体功率器件技术领域,特别是涉及一种具有缓变电容的半导体功率器件。

背景技术:

2.半导体功率器件包括n型衬底,位于n型衬底之上的n型外延层,凹陷在n型外延层内的若干个沟槽,位于相邻的沟槽之间的n型外延层部分为半导体功率器件的台面(mesa)结构。现有技术的半导体功率器件中的所有mesa结构的宽度都是相同的,半导体功率器件在开关时,mesa结构会在同一电压下被同时耗尽夹断,这使得电压震荡非常严重。

技术实现要素:

3.有鉴于此,本发明的目的是提供一种半导体功率器件,以解决现有技术的半导体功率器件在开关时电压震荡严重的问题。

4.为达到本发明的上述目的,本发明提供了一种半导体功率器件,包括:

5.n型衬底;

6.位于所述n型衬底之上的n型外延层;

7.凹陷在所述n型外延层内的至少三个沟槽;

8.位于相邻的所述沟槽之间的n型外延层部分为台面结构,所述台面结构的上部设有p型体区,所述p型体区内设有n型源区;

9.所述台面结构中,包括至少一个下部宽度为第一宽度的台面结构和至少一个下部宽度为第二宽度的台面结构,所述第二宽度大于所述第一宽度。

10.可选的,所述下部宽度为第二宽度的台面结构的数量大于所述下部宽度为第一宽度的台面结构的数量。

11.可选的,位于所述下部宽度为第一宽度的台面结构的两侧的所述沟槽,至少有其中一个沟槽的底部设有位于所述n型外延层内的n型注入区。

12.可选的,所述沟槽内设有栅极,所述栅极通过栅氧化层与所述n型外延层隔离。

13.可选的,所述沟槽内还设有导电多晶硅,所述导电多晶硅通过绝缘介质层与所述n型外延层和所述栅极隔离。

14.可选的,所述栅极位于所述沟槽的上部,所述导电多晶硅位于所述沟槽的下部。

15.可选的,所述栅极位于所述沟槽的上部,所述导电多晶硅位于所述沟槽的下部并向上延伸至所述沟槽的上部内。

16.可选的,所述沟槽的上部的宽度大于所述沟槽的下部的宽度。

17.本发明的半导体功率器件具有至少两种不同下部宽度的mesa结构,即本发明的半导体功率器件具有缓变的电容,本发明的半导体功率器件在开关时,随着电压的增加,具有小的下部宽度的mesa结构会先被耗尽夹断,具有大的下部宽度的mesa结构后被耗尽夹断,这可以降低半导体功率器件在开关时的电压震荡;同时,通过在小的下部宽度的mesa结构

的两侧的沟槽底部的n型外延层内形成n型注入区,可以进一步调节电容的缓变程度,从而能够进一步降低半导体功率器件在开关时的电压震荡。

附图说明

18.为了更加清楚地说明本发明示例性实施例的技术方案,下面对描述实施例中所需要用到的附图做一简单介绍。

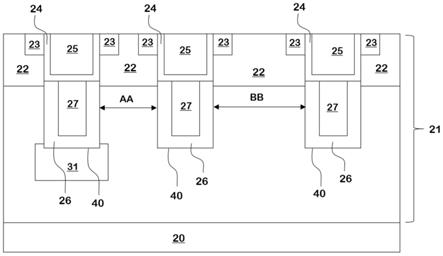

19.图1是本发明提供的半导体功率器件的一个实施例的剖面结构示意图。

具体实施方式

20.以下将结合本发明实施例中的附图,通过具体方式,完整地描述本发明的技术方案。显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。应当理解,本发明所使用的诸如“具有”、“包含”以及“包括”等术语并不配出一个或多个其它元件或其组合的存在或添加。同时,为清楚地说明本发明的具体实施方式,说明书附图中所列示意图,放大了本发明所述的层和区域的厚度,且所列图形大小并不代表实际尺寸。

21.图1是本发明提供的半导体功率器件的一个实施例的剖面结构示意图,如图1所示,本发明的半导体功率器件包括n型衬底20,n型衬底20用于形成半导体功率器件的n型漏区。位于n型衬底20之上的n型外延层21,凹陷在n型外延层21内的至少三个沟槽40,本发明图1所示实施例中仅示出了三个沟槽40结构。

22.位于相邻的沟槽40之间的n型外延层部分为半导体功率器件的台面(mesa)结构,在mesa结构的上部设有p型体区22,在p型体区22内设有n型源区23。本发明的半导体功率器件的mesa结构中,包括至少一个下部宽度为第一宽度aa的台面结构和至少一个下部宽度为第二宽度bb的台面结构,第二宽度bb大于第一宽度aa。保证本发明的半导体功率器件具有缓变的电容,本发明的半导体功率器件在开关时,随着电压的增加,具有小的下部宽度的mesa结构会先被耗尽夹断,具有大的下部宽度的mesa结构后被耗尽夹断,这可以降低半导体功率器件在开关时的电压震荡。

23.需要说明的是,本发明图1所示实施例中仅示出了三个沟槽40结构、一个下部宽度为第一宽度aa的台面结构和一个下部宽度为第二宽度bb的台面结构,可以理解的是,本发明实施例提供的半导体功率器件还可以包括更多个沟槽结构以及更多个台面结构,例如本发明实施例提供的半导体功率器件还可以包括下部宽度为第n宽度的台面结构(图中未示出),n>2且n为整数,并且第n宽度可以与第一宽度和第二宽度不同,如此可以进一步调节电容的缓变程度,进一步降低半导体功率器件在开关时的电压震荡。

24.可选的,下部宽度为第二宽度bb的台面结构的数量大于下部宽度为第一宽度aa的台面结构的数量,如此可以进一步调节电容的缓变程度,保证半导体功率器件的电容变化更加平缓,进一步降低半导体功率器件在开关时的电压震荡。

25.位于下部宽度为第一宽度aa的台面结构的两侧的两个沟槽40,至少有其中一个沟槽40的底部设有位于n型外延层21内的n型注入区,图1所示实施例中仅示出了在下部宽度为第一宽度aa的台面结构的左侧的沟槽40底部的n型外延层21内形成有n型注入区31的结构,如此可以进一步调节电容的缓变程度,保证半导体功率器件的电容变化更加平缓,从而能够进一步降低半导体功率器件在开关时的电压震荡。

26.在沟槽40内设有栅极25,栅极25通过栅氧化层24与n型外延层21隔离,栅极25通常通过栅极电压来控制位于p型体区22内的电流沟道的开启和关断。沟槽40内还设有导电多晶硅27,导电多晶硅27通过绝缘介质层26与n型外延层21隔离,导电多晶硅27通过栅氧化层24与栅极25隔离,导电多晶硅27通常外接源极电压。

27.图1所示实施例中,栅极25位于沟槽40的上部,导电多晶硅27位于沟槽40的下部,由此本发明为上下栅结构的半导体功率器件。

28.可选的,栅极可以位于沟槽的上部,导电多晶硅位于沟槽的下部并向上延伸至沟槽的上部内,由此本发明为左右栅结构的半导体功率器件,同时,在左右栅结构的半导体功率器件中,导电多晶硅可以通过栅氧化层与栅极隔离,也可以通过绝缘介质层与栅极隔离,本发明实施例对此不作限定。

29.进一步的,在左右栅结构的半导体功率器件中,沟槽上部的宽度可以大于沟槽下部的宽度,该结构在本发明实施例中不再具体展示。需要说明的是,在上下栅结构的半导体功率器件中,沟槽上部的宽度同样可以大于沟槽下部的宽度,该结构在本发明实施例中不再具体展示。

30.以上具体实施方式及实施例是对本发明技术思想的具体支持,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在本技术方案基础上所做的任何等同变化或等效的改动,均仍属于本发明技术方案保护的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1