线路末端结构及其形成方法与流程

1.本发明涉及一种线路结构及其形成方法,且特别是涉及一种线路末端结构及其形成方法。

背景技术:

2.在半导体的制作工艺中,导线末端断切(line end cut)的缺陷常会造成线路布局失效(layout failed)。举例而言,若相邻的导线在其末端的附近有不预期的相连,则会因此造成不预期的短路而影响元件的品质。

技术实现要素:

3.本发明提供一种线路末端结构及其形成方法,其具有较佳的品质。

4.本发明的线路末端结构包括基板、多个导线以及第一绝缘图案层。多个导线位于基板上。第一绝缘图案层位于基板上。第一绝缘图案层包括多个第一绝缘部分以及第二绝缘部分。多个第一绝缘部分分别位于多个导线上。第二绝缘部分连接两相邻的多个第一绝缘部分。第二绝缘部分与基板间未形成多个导线。

5.在本发明的一实施例中,多个第一绝缘部分的厚度小于第二绝缘部分的厚度。

6.在本发明的一实施例中,多个第一绝缘部分的厚度与多个导线的厚度的总合相同于第二绝缘部分的厚度。

7.在本发明的一实施例中,多个第一绝缘部分的顶面与第二绝缘部分的顶面共面。

8.在本发明的一实施例中,多个第一绝缘部分覆盖多个导线的顶面,且第二绝缘部分覆盖多个导线的末端的侧表面。

9.在本发明的一实施例中,第二绝缘部分包括向远离多个导线的方向凸出的弧状图案。

10.在本发明的一实施例中,第二绝缘部分的宽度大于或等于多个第一绝缘部分的宽度。

11.在本发明的一实施例中,线路末端结构还包括第二绝缘层。第二绝缘层至少位于多个导线之间。第二绝缘层覆盖导线的相对二侧面。

12.在本发明的一实施例中,第二绝缘层还覆盖第一绝缘图案层的相对二侧面。

13.本发明的线路末端结构的形成方法包括以下步骤:提供基板;形成导电层于基板上;形成第一绝缘层于基板上,且第一绝缘层至少覆盖导电层;移除部分的第一绝缘层,以形成第一绝缘图案层,其中第一绝缘图案层包括多个第一绝缘部分以及第二绝缘部分,第二绝缘部分连接两相邻的多个第一绝缘部分;以及移除部分的第一导电层,以形成多个导线,其中多个导线分别位于多个第一绝缘部分与基板之间,并且第二绝缘部分与基板间未形成多个导线。

14.基于上述,线路末端结构的导线可以具有较佳的品质。

附图说明

15.图1a、图2a、图3a及图4a是本发明的第一实施例的一种线路末端结构的部分形成方法的部分上视示意图;

16.图1b、图2b、图3b及图4b是本发明的第一实施例的一种线路末端结构的部分形成方法的部分剖视示意图;

17.图1c、图2c、图3c、图3d、图4c及图4d是本发明的第一实施例的一种线路末端结构的部分形成方法的部分剖视示意图;

18.图5a是本发明的第二实施例的一种线路末端结构的部分上视示意图;

19.图5b及图5c是本发明的第二实施例的一种线路末端结构的部分剖视示意图。

20.符号说明

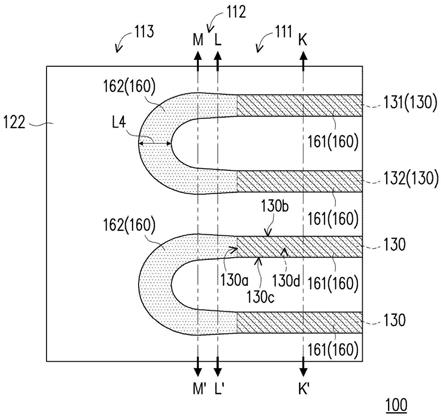

21.100、200:线路末端结构

22.110:基板

23.111:第一区

24.112:第二区

25.113:第三区

26.120:绝缘层

27.121、122:膜层

28.139:导电层

29.130、131、132:导线

30.130h:厚度

31.130a:第一侧面

32.130b:第二侧面

33.130c:第三侧面

34.130d:顶面

35.140:第一绝缘层

36.140d:顶面

37.141:部分第一绝缘层

38.141h:厚度

39.142:部分第一绝缘层

40.142h:厚度

41.151、152、153:膜层

42.155:掩模层

43.160:第一绝缘图案层

44.160b、160c:侧面

45.160d:顶面

46.161:第一绝缘部分

47.161d:顶面

48.161h:厚度

49.162:第二绝缘部分

50.162d:顶面

51.162h:厚度

52.270:第二绝缘层

53.s:间距

54.l1、l2、l3、l4:宽度

具体实施方式

55.下文列举一些实施例并配合所附的附图来进行详细地说明,但所提供的实施例并非用以限制本发明所涵盖的范围。此外,附图仅以说明为目的,并未依照原尺寸作图。为了方便理解,下述说明中相同的元件将以相同的符号标示来说明。另外,关于文中所使用「包括」或「具有」等等用语,均为开放性的用语;也就是指「包括」或「具有」但不限于。

56.关于文中所使用「基本上」或「大致上」等等用语,可以是包含可接受的公差范围(tolerance range)。而且,文中所提到的方向性用语,例如:「上」、「下」、「顶」、「底」等,仅是用以参考附图的方向。因此,使用的方向性用语是用来说明,而并非用来限制本发明。

57.当一元件(如:一膜层、一区域或一其他类似的用语)被称为在「另一元件上」或「连接到另一元件」时,其可以直接在另一元件上或与另一元件连接,或其之间也可存在其他的元件。类似地,当一步骤(如:一制作工艺或一其他类似的用语)被称为在「另一步骤之后」时,其可以直接在另一步骤之后执行,或其之间也可存在其他的步骤。

58.图1a、图2a、图3a及图4a是依照本发明的第一实施例的一种线路末端结构的部分形成方法的部分上视示意图。图1b可以是对应于图1a中a-a’剖线上的剖视示意图。图1c可以是对应于图1a中b-b’剖线或c-c’剖线上的剖视示意图。图2b可以是对应于图2a中d-d’剖线上的剖视示意图。图2c可以是对应于图2a中e-e’剖线或f-f’剖线上的剖视示意图。图3b可以是对应于图3a中g-g’剖线上的剖视示意图。图3c可以是对应于图3a中h-h’剖线上的剖视示意图。图3d可以是对应于图3a中j-j’剖线上的剖视示意图。图4b可以是对应于图4a中k-k’剖线上的剖视示意图。图4c可以是对应于图4a中l-l’剖线上的剖视示意图。图4d可以是对应于图4a中m-m’剖线上的剖视示意图。另外,剖线a-a’、剖线d-d’、剖线g-g’及/或剖线k-k’对应于基板110的位置可以相同或相似,剖线b-b’、剖线e-e’、剖线h-h’及/或剖线l-l’对应于基板110的位置可以相同或相似,剖线c-c’、剖线f-f’、剖线j-j’及/或剖线m-m’对应于基板110的位置可以相同或相似。

59.请参照图1a、图1b及图1c,提供基板110。基板110可以具有第一区111、第二区112以及第三区113。第二区112位于第一区111与第三区113之间。第一区111与第三区113可以分别连接于第二区112的两不同侧。

60.在本实施例中,基板110可以包括硅质基板或其他类似的半导体基板,但本发明不限于此。举例而言,基板110可以包括硅晶片。

61.请参照图1a、图1b及图1c,在基板110的第一区111上形成导电层139。导电层139可以通过溅镀(sputtering)、沉积(deposition)、电镀(plating)及/或其他适宜的制作工艺所形成,但本发明不限于此。在本实施例中,导电层139基本上不覆盖于基板110的第二区112或第三区113上。基于导电性的考虑,导电层139的材质可以包括金属、金属合金、金属硅化物、金属氮化物或上述的堆叠,然而本发明不限于此。

62.在本实施例中,可以于基板110上形成绝缘层120,且导电层139可以形成于绝缘层120上。也就是说,部分的绝缘层120可以位于导电层139与基板110之间。

63.在一实施例中,绝缘层120可以通过沉积制作工艺或其他适宜的制作工艺而形成,但本发明不限于此。在一实施例中,绝缘层120的材质可以包括硅的氧化物、硅的氮化物或上述的组合,但本发明不限于此。

64.在本实施例中,绝缘层120可以包括多个膜层121、122,但本发明不限于此。在一实施例中,绝缘层120可以为单层结构。

65.在一未绘示的实施例中,膜层121或膜层122在基板110上其他未绘示的区域中,可能具有其他相同或不同的用途。举例而言,膜层121可以包括用于将基板110与其上的元件相分离的氧化硅(silicon dioxide;sio

x

)层,但本发明不限于此。又举例而言,膜层122可以包括作为硬掩模(hard mask;hm)层。

66.在一实施例中,绝缘层120可以包括被称为缓冲层(buffer layer)的膜层,但本发明不限于此。

67.请参照图2a、图2b及图2c,至少于基板110的第一区111及第二区112上形成第一绝缘层140。第一绝缘层140覆盖导电层139。

68.在本实施例中,第一绝缘层140可以还位于基板110的第三区113上,但本发明不限于此。

69.在本实施例中,第一绝缘层140的顶面140d可以为一平坦表面,但本发明不限于此。举例而言,可以通过相同或相似于绝缘层120的形成方式,在基板110上形成第一绝缘材料层(未绘示)。然后,可以对前述的第一绝缘材料层实施化学机械平坦化制作工艺(chemical-mechanical polishing process;cmp process)或其他适宜的平坦化制作工艺(planarization process),而形成具有平坦的顶面140d的第一绝缘层140。

70.在本实施例中,覆盖于导电层139上的部分第一绝缘层141的厚度141h可能不同于其他某处(如:未覆盖导电层139之处)的其他部分第一绝缘层142的厚度142h。举例而言,厚度141h可能小于厚度142h。

71.在一实施例中,第一绝缘层140可以包括被称为平坦层(buffer layer)的膜层,但本发明不限于此。

72.请参照图3a、图3b、图3c及图3d,可以于基板110上形成掩模层155。掩模层155可以重叠于部分的导电层139及部分的第一绝缘层140,且掩模层155的材质基本上不同于导电层139及第一绝缘层140。举例而言,掩模层155可以包括通过沉积及光刻蚀刻的方式所形成的图案化非晶硅层,但本发明不限于此。

73.请参照图3a至图4a、图3b至图4b、图3c至图4c及图3d至图4d,在一实施例中,可以通过蚀刻或其他适宜的方式,以移除位于第一绝缘层140上且未被掩模层155覆盖的部分膜层151、152、153。

74.在一未绘示的实施例中,膜层151、膜层152或膜层153在基板110上其他未绘示的区域中,可能具有其他相同或不同的用途。

75.请参照图3a至图4a、图3b至图4b、图3c至图4c及图3d至图4d,移除部分的第一绝缘层140,以形成第一绝缘图案层160。第一绝缘图案层160包括多个第一绝缘部分161以及第二绝缘部分162。多个第一绝缘部分161位于第一区111。第二绝缘部分162位于第二区112。

第二绝缘部分162连接多个第一绝缘部分161。

76.在本实施例中,可以通过蚀刻(如:干蚀刻(dry etching),但不限)或其他适宜的方式移除未被掩模层155覆盖的部分第一绝缘层140,但本发明不限于此。

77.在本实施例中,第一绝缘图案层160的图案可以相同或相似于掩模层155的图案。也就是说,第一绝缘图案层160的图案至少可以依据掩模层155的图案设计而进行调整,于本发明并不加以限制。

78.请参照图3a至图4a、图3b至图4b、图3c至图4c及图3d至图4d,移除部分的第一导电层139,以形成多个导线130。多个导线130位于多个第一绝缘部分161与基板110之间。举例而言,各个导线130位于各个第一绝缘部分161与基板110之间。

79.在本实施例中,可以通过蚀刻(如:干蚀刻(dry etching),但不限)或其他适宜的方式移除未被掩模层155覆盖的部分第一导电层139,但本发明不限于此。

80.在本实施例中,导线130的图案可以相同或相似于掩模层155的部分图案。也就是说,导线130的图案至少可以依据掩模层155的图案设计而进行调整,于本发明并不加以限制。

81.在一实施例中,在形成第一绝缘图案层160及多个导线130之后,可以移除掩模层155。举例而言,可以通过移除第一绝缘图案层160与掩模层155之间的膜层(如:将膜层151图案化后的膜层),以移除掩模层155。

82.在一实施例中,在移除部分的第一导电层139或移除掩模层155的过程(如:将第一绝缘图案层160与掩模层155之间的膜层移除的过程)中,部分的绝缘层120可能被些微地移除,但本发明不限于此。

83.经过上述形成方法后即可大致上完成本实施例的线路末端结构100的制作。

84.请参照图4a、图4b、图4c及图4d,线路末端结构100包括基板110、多个导线130以及第一绝缘图案层160。基板110具有第一区111及第二区112。第二区112相连于第一区111。多个导线130位于基板110的第一区111上。第一绝缘图案层160包括多个第一绝缘部分161以及第二绝缘部分162。第一绝缘部分161位于基板110的第一区111上。多个导线130位于多个第一绝缘部分161与基板110之间。第二绝缘部分162位于基板110的第二区112上。第二绝缘部分162连接多个第一绝缘部分161。

85.在本实施例中,通过上述形成方法所形成的线路末端结构100,可以降低相邻的导线130产生不预期地相接触的可能,因此导线130具有较佳的品质。举例而言,多个导线130可以包括相邻的导线131及导线132,且导线131及导线132可以彼此分离。

86.在本实施例中,通过上述形成方法所形成的线路末端结构100可以用于具有高密度线路的电子元件。举例而言,导线130可以为位线(bit line;bl),且相邻的导线130之间的间距s可以小于或等于70纳米(nanometer;nm),但本发明不限于此。在一实施例中,相邻的导线130之间的间距s可以小于或等于60纳米。

87.在本实施例中,第一绝缘图案层160可以提供导线130良好的保护,或是,可以降低导线130与其他导体产生不预期地相接触的可能。

88.在本实施例中,通过第二绝缘部分162将多个第一绝缘部分161连接,可以降低第一绝缘部分161倾倒或剥离(peeling)的可能。

89.在本实施例中,第二绝缘部分162的宽度可以大于或等于第一绝缘部分161的宽度

l1。举例而言,第二绝缘部分162与第一绝缘部分161相接之处的宽度可以大致上等于第一绝缘部分161的宽度l1,而第二绝缘部分162远离第一绝缘部分161处的宽度(如:宽度l2、宽度l3或宽度l4)可以大于第一绝缘部分161的宽度l1。在本实施例中,第一绝缘部分161的宽度l1大致上等于导线130的宽度。

90.在本实施例中,第二绝缘部分162的宽度可以自与第一绝缘部分161相接之处向远离第一绝缘部分161的延伸方向逐渐增加。举例而言,宽度l4可以大于宽度l3,且宽度l3可以大于宽度l2。如此一来,可以降低第二绝缘部分162倾倒或剥离的可能。

91.在本实施例中,第二绝缘部分162包括向远离所述多个导线的方向凸出的弧状图案。如此一来,还可以降低第二绝缘部分162倾倒或剥离的可能。

92.在本实施例中,基板110可以还具有第三区113。多个导线130及第一绝缘图案层160可以位于第三区113以外的区域上。

93.在本实施例中,第一绝缘部分161的厚度161h小于第二绝缘部分162的厚度162h。

94.在本实施例中,第一绝缘部分161的厚度161h与导线130的厚度130h的总合基本上相同于第二绝缘部分162的厚度162h。举例而言,一导线130的厚度130h以及前述导线130上方的第一绝缘部分161的厚度161h的总合,可以相同于第二绝缘部分162的厚度162h。

95.在本实施例中,第一绝缘部分161的顶面161d基本上与第二绝缘部分162的顶面162d共面。

96.在本实施例中,导线130可以具有顶面130d、第一侧面130a、第二侧面130b以及第三侧面130c。顶面130d可以是在导线130中远离基板110的表面。第一侧面130a可以是导线130末端的侧表面。顶面130d连接第一侧面130a、第二侧面130b以及第三侧面130c。第一侧面130a连接顶面130d、第二侧面130b以及第三侧面130c。第二侧面130b相对于第三侧面130c。第一绝缘部分161可以覆盖对应的导线130的顶面130d。第二绝缘部分162可以覆盖对应的导线130的第一侧面130a。在一实施例中,导线130的第二侧面130b以及第三侧面130c可以不被第一绝缘图案层160所覆盖。

97.图5a是依照本发明的第二实施例的一种线路末端结构的部分上视示意图。图5b可以是对应于图5a中n-n’剖线上的剖视示意图。图5b可以是对应于图5a中p-p’剖线上的剖视示意图。第二实施例的线路末端结构200的形成方法与第一实施例的线路末端结构100的形成方法相似,其类似的构件以相同的标号表示,且具有类似的功能、材质或形成步骤,并省略描述。

98.请参照图5a、图5b及图5c,线路末端结构200包括基板110、多个导线130、第一绝缘图案层160以及第二绝缘层270。第二绝缘层270至少位于多个导线130之间。第二绝缘层270可以覆盖导线130的第二侧面130b及/或第三侧面130c。

99.在本实施例中,可以通过沉积制作工艺或其他适宜的制作工艺,以于基板110上形成第二绝缘层270。

100.在本实施例中,第二绝缘层270可以还位于基板110的第三区113上。

101.在本实施例中,第二绝缘层270可以覆盖第一绝缘图案层160的相对两侧面160b、160c。

102.在本实施例中,第二绝缘层270可以降低第一绝缘图案层160倾倒或剥离(peeling)的可能。

103.在本实施例中,第二绝缘层270与第一绝缘图案层160可以是在不同的步骤中所形成。因此,第二绝缘层270与第一绝缘图案层160之间可以具有对应的界面(interface)。

104.在本实施例中,第二绝缘层270可以更覆盖第一绝缘图案层160的顶面160d。在一实施例中,可以在第二绝缘层270上形成其他的元件或膜层。

105.在一未绘的实施例中,在前述附图中的膜层于基板110的其他未绘示区域上,可以具有相同、相似或不同的图案;或是,不会出现于基板110的其他未绘示区域上。举例而言,导线130在其他未绘示的区域上,可能包括曲线的条纹。

106.在一未绘的实施例中,在两步骤之间可能会有其他未绘示或说明的步骤。举例而言,在完成图2a、图2b及图2c所绘示的结构之后,以及在形成图3a、图3b、图3c及图3d所绘示的结构之前,可能会在基板110上形成、图案化及/或移除其他的膜层。

107.在一未绘的实施例中,在基板110的其他未绘示区域上,可以具有其他的膜层或构件。举例而言,在图4a、图4b、图4c及图4d的基板110的其他未绘示区域上,可以包括由一个或多个的导电层、半导电层及/或绝缘层所构成主动(有源)元件(如:薄膜晶体管)、被动(无源)元件(如:电容)或其他适宜的元件。

108.在前述实施例(包括所绘示的实施例、所描述的实施例或未绘示的实施例)中,导电层可为单层或多层结构。而若为多层结构的导电层,则前述的多层结构之间可以不具有绝缘材质。

109.在前述实施例(包括所绘示的实施例、所描述的实施例或未绘示的实施例)中,绝缘层可为单层或多层结构。而若为多层结构的绝缘层,则前述的多层结构之间可以不具有导电材质。

110.综上所述,本发明的线路末端结构及其形成方法,可以使其导线具有较佳的品质。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1