一种用于整流电路的复合半导体肖特基二极管的制备方法与流程

1.本发明属于半导体领域,具体涉及一种用于整流电路的复合半导体肖特基二极管的制备方法。

背景技术:

2.根据我国环境射频能量分布评估,2.45g wi

‑

fi频段内的射频信号为环境中的主要rf信号源,比如生活中到处可见的wi

‑

fi路由器、笔记本电脑和平板电脑等无线终端,因此收集并应用这些能量成为当前业内研究发展的一个重要方向。

3.但是2.45g wi

‑

fi频段的环境射频功率密度较低,数值小于

‑

20dbm,在如此弱能量密度输入条件下,即使采用整流效率优于mos的肖特基二极管(schottky barrier diode,以下简称sbd)作为整流电路的核心元器件,其整流效率仍然很低,甚至无法开启工作,需要配合外围电路被动开启。

4.现有技术中,在外围电路被动开启配合下,基于安捷伦公司hsms

‑

2850ge半导体肖特基二极管(sbd)的弱能量密度能量收集系统的整流效率最高,当能量密度为

‑

10dbm时,整流效率可达20%,但当能量密度为

‑

20dbm条件时,整流效率不足10%。如此低的整流效率,无法真正实现2.45g弱能量密度射频能量的收集应用,因此对核心元器件

‑

肖特基二极管予以设计优化势在必行。

技术实现要素:

5.为了解决现有技术中存在的上述问题,本发明提供了一种用于整流电路的复合半导体肖特基二极管的制备方法。本发明要解决的技术问题通过以下技术方案实现:

6.本发明实施例提供了一种用于整流电路的复合半导体肖特基二极管的制备方法,包括如下步骤:

7.选取[100]晶向geoi衬底;

[0008]

在所述geoi衬底顶层ge的上表面生长pb层;

[0009]

在所述pb层的上表面淀积sio2保护层;

[0010]

对包括所述geoi衬底、所述pb层、所述sio2保护层的整个材料进行激光再晶化工艺处理,形成dr

‑

ge1‑

x

pb

x

复合层;

[0011]

使用离子注入工艺对所述复合层的第一区域注入n型离子,进行第一掺杂;

[0012]

使用离子注入工艺对所述复合层的第二区域注入n型离子,进行第二掺杂;

[0013]

刻蚀所述复合层形成凹槽,并填充所述凹槽;

[0014]

在所述第一区域上形成al电极;

[0015]

在所述第二区域上形成ti电极。

[0016]

在本发明的一个实施例中,在所述geoi衬底顶层ge的上表面生长pb层,包括:

[0017]

在所述geoi衬底的上表面涂抹光刻胶,并对所述geoi衬底顶层ge的第一区域曝光;

[0018]

利用固态气源mbe工艺,在所述geoi衬底顶层ge上表面生长20nm~25nm的pb层,并去除光刻胶。

[0019]

在本发明的一个实施例中,对包括所述geoi衬底、所述pb层、所述sio2保护层的整个材料进行激光再晶化工艺处理,形成dr

‑

ge1‑

x

pb

x

复合层,包括:

[0020]

将包括所述geoi衬底、所述pb层、所述sio2保护层的整个材料加热至700℃,连续采用激光工艺晶化所述整个衬底材料;其中,激光波长为808nm,激光光斑尺寸10mm

×

1mm,激光功率为1.5kw/cm2,激光移动速度为25mm/s,自然冷却所述整个衬底材料,形成dr

‑

ge1‑

x

pb

x

复合层;

[0021]

利用干法刻蚀工艺刻蚀所述sio2层。

[0022]

在本发明的一个实施例中,所述dr

‑

ge1‑

x

pb

x

中x的范围为3%~5%。

[0023]

在本发明的一个实施例中,使用离子注入工艺对所述复合层的第一区域注入n型离子,进行第一掺杂;包括:

[0024]

在所述复合层的上表面涂抹光刻胶,并对所述第一区域曝光;

[0025]

在温度为200~300℃下,使用离子注入工艺在所述第一区域注入n型离子,进行第一掺杂,所述第一掺杂的浓度为1

×

10

19c

m

‑3,并去除所述光刻胶。

[0026]

在本发明的一个实施例中,使用离子注入工艺对所述复合层的第二区域注入n型离子,进行第二掺杂,包括:

[0027]

在所述复合层的上表面涂抹光刻胶,并对所述第二区域曝光;

[0028]

在温度为200~300℃下,使用离子注入工艺在所述第二区域注入n型离子,进行第二掺杂,所述掺杂浓度为2.0

×

10

17

cm

‑3~3

×

10

17

cm

‑3,并去除所述光刻胶;

[0029]

在600℃温度下,在n2氛围下退火30分钟。

[0030]

在本发明的一个实施例中,刻蚀所述复合层形成凹槽,并填充所述凹槽,包括:

[0031]

在所述复合层的上表面涂抹光刻胶,对所述复合层曝光;

[0032]

使用干法刻蚀工艺对所述曝光区域进行刻蚀,形成深度为50~150nm的所述凹槽,去除所述光刻胶。

[0033]

在750℃~850℃温度下,利用化学气相沉积工艺在所述复合层的上表面淀积sio2,将所述凹槽填满;

[0034]

利用化学机械抛光方法去除所述复合层上表面的sio2。

[0035]

在本发明的一个实施例中,在所述第一区域上形成al电极,包括:

[0036]

在所述复合层的上表面涂抹光刻胶,并对所述第一区域曝光;

[0037]

利用电子束蒸发工艺在所述第一区域的上表面淀积厚度为70~90nm的al金属,以形成欧姆接触,去除所述光刻胶。

[0038]

在本发明的一个实施例中,在所述第二区域上形成ti电极,包括:

[0039]

在所述复合层、所述al电极的上表面涂抹光刻胶,并对所述第二区域曝光;

[0040]

利用电子束蒸发工艺在所述第二区域的上表面淀积厚度为70~90nm的ti金属,以形成肖特基接触,去除光刻胶。

[0041]

在本发明的一个实施例中,所述顶层ge、所述复合层的厚度均为300~500nm。

[0042]

与现有技术相比,本发明的有益效果:

[0043]

本实施例的方案通过pb合金化致晶向消除技术,相比于纯ge半导体,得到的gepb

合金半导体的电子迁移率得到极大提升,因此能够降低串联电阻,提高整流效率;并且,采用金属钛(ti)制备肖特基接触区域的电极,使用[100]晶向的gepb材料,整体上能够增大sbd的零偏电流响应度,提高弱能量密度下sbd的整流效率;并且,通过将纵向空间电荷区进行折叠,减小sbd的结电容,在三者的共同作用,能够保证sbd的整流效率的大幅提高。

附图说明

[0044]

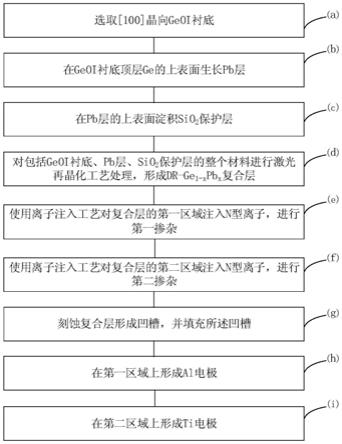

图1为本发明实施例提供的一种用于整流电路的复合半导体肖特基二极管的制备方法的流程示意图;

[0045]

图2a~2r为本发明实施例提供的另一种用于整流电路的复合半导体肖特基二极管的工艺示意图。

具体实施方式

[0046]

本发明肖特基二极管的制备方法、具体结构及效果详见下面实施例。

[0047]

下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

[0048]

实施例一

[0049]

请参见图1,图1为本发明实施例提供的一种用于整流电路的肖特基二极管的制备方法的流程示意图。该制备方法包括如下步骤:

[0050]

步骤a、选取[100]晶向geoi衬底;

[0051]

步骤b、在所述geoi衬底顶层ge的上表面生长pb层;

[0052]

步骤c、在所述pb层的上表面淀积sio2保护层;

[0053]

步骤d、对包括所述geoi衬底、所述pb层、所述sio2保护层的整个材料进行激光再晶化工艺处理,形成dr

‑

ge1‑

x

pb

x

复合层;

[0054]

步骤e、使用离子注入工艺对所述复合层的第一区域注入n型离子,进行第一掺杂;

[0055]

步骤f、使用离子注入工艺对所述复合层的第二区域注入n型离子,进行第二掺杂;

[0056]

步骤g、刻蚀所述复合层形成凹槽,并填充所述凹槽;

[0057]

步骤h、在所述第一区域上形成al电极;

[0058]

步骤i、在所述第二区域上形成ti电极。

[0059]

本实施例通过pb合金化致晶向消除技术,相比于纯ge半导体,得到的gepb合金半导体的电子迁移率得到极大提升,因此能够降低串联电阻,提高整流效率;同时,采用金属钛(ti)制备肖特基接触区域的电极,使用[100]晶向的gepb材料,整体上能够增大sbd的零偏电流响应度,提高弱能量密度下sbd的整流效率;并且,通过将纵向空间电荷区进行折叠,减小sbd的结电容,在三者的共同作用,能够保证sbd的整流效率的大幅提高。

[0060]

实施例二

[0061]

请再次参见图1并参考图2a~2r,图2a~2r为本发明实施例提供的一种用于整流电路的复合半导体肖特基二极管的工艺示意图。本实施例在上述实施例的基础上,重点对该制备方法进行详细描述。具体地,该工艺还包括:

[0062]

s01、如图2a所示,选取[100]晶向geoi衬底001。

[0063]

具体地,所述geoi衬底顶层ge的厚度为300~500nm。

[0064]

发明人研究发现,电子亲合能越大,越有利于sbd的整流效率的提升。由于[100]晶向ge半导体电子亲合能(4.272ev)明显大于[110]晶向ge半导体电子亲合能(4.163ev)。因此,本实施例通过采用[100]晶向ge半导体形成geoi衬底,有利于提升整流效率。

[0065]

s02、如图2b~2c所示,在所述geoi衬底001顶层ge的上表面生长pb层007;

[0066]

s021、如图2b所示,在所述geoi衬底001顶层ge的上表面涂抹光刻胶006,并对所述geoi衬底001顶层ge曝光;

[0067]

s022、如图2c所示,利用固态气源mbe工艺,在所述geoi衬底001顶层ge上表面生长20nm~25nm的pb层007,并去除光刻胶006。

[0068]

所述mbe工艺为分子束外延(molecular beam epitaxy,简称mbe)工艺。

[0069]

s03、如图2d所示,在所述pb层007的上表面淀积sio2保护层008。

[0070]

具体地,利用cvd工艺在所述pb层的上表面淀积厚度为100~150nm的sio2层008。

[0071]

s04、如图2e~2f所示,对包括所述geoi衬底001、所述pb层007、所述sio2保护层008的整个材料进行激光再晶化工艺处理,形成dr

‑

ge1‑

x

pb

x

复合层002。

[0072]

s041、如图2e所示,将所述包括geoi衬底001、所述pb层007及所述sio2层008的整个材料加热至700℃,连续采用激光再晶化工艺处理所述整个衬底材料;其中,激光波长为808nm,激光光斑尺寸10mm

×

1mm,激光功率为1.5kw/cm2,激光移动速度为25mm/s,自然冷却所述整个衬底材料,形成dr

‑

ge1‑

x

pb

x

复合层002。

[0073]

s042、如图2f所示,利用干法刻蚀工艺刻蚀所述sio2层008。

[0074]

发明人研究发现,提高电子迁移率能够降低sbd串联电阻,从而提高sbd的整流效率。因此,本实施例通过采用pb合金化致晶向消除技术,相比于纯ge半导体,得到的gepb合金半导体的电子迁移率得到极大提升,因此能够降低串联电阻,提高整流效率。

[0075]

进一步地,发明人还发现,在ge半导体材料的改性过程中,为了将ge由间接带隙型半导体转变为直接带隙型半导体,pb合金化的比例范围控制在3~5%之间就可以达到目的,即所述dr

‑

ge1‑

x

pb

x

中x的范围为3%~5%,因此本实施例就选用该范围制作复合层;优先地,所述pb合金化的比例为3.125%。

[0076]

s05、如图2g~2h所示,使用离子注入工艺对所述复合层002的第一区域0021注入n型离子,进行第一掺杂。

[0077]

s051、如图2g所示,在所述复合层002的上表面涂抹光刻胶009,并对所述第一区域0021曝光。

[0078]

在一种可选的实施方式中,所述第一区域0021是指所述geoi衬底的左侧区域。

[0079]

s052、如图2h所示,在温度为200~300℃下,使用离子注入工艺在所述第一区域0021注入n型离子,进行第一掺杂,所述第一掺杂的浓度为1

×

10

19

cm

‑3,并去除所述光刻胶009。

[0080]

s06、如图2i~2j所示,使用离子注入工艺对所述复合层002的第二区域0022注入n型离子,进行第二掺杂。

[0081]

s061、如图2i所示,在所述复合层002的上表面涂抹光刻胶0010,并对所述第二区域0022曝光。

[0082]

在一种可选的实施方式中,所述第二区域0022是指所述geoi衬底的右侧区域。

[0083]

s062、如图2j所示,在温度为200~300℃下,使用离子注入工艺在所述第二区域

0022注入n型离子,进行第二掺杂,所述掺杂浓度为2.0

×

10

17

cm

‑3~3

×

10

17

cm

‑3,并去除所述光刻胶0010。

[0084]

s063、在600℃温度下,在n2氛围下退火30分钟。

[0085]

可以理解的是,步骤s05和步骤s06可以互换,只要使所述第一区域0021和所述al电极003接触,形成欧姆接触;相应地,使所述第二区域0022和所述ti电极004接触,形成肖特基接触即可。

[0086]

s07、如图2k~2n所示,刻蚀所述复合层002形成凹槽005,并填充所述凹槽005。

[0087]

s071、如图2k所示,在所述复合层002的上表面涂抹光刻胶0011,对所述复合层002曝光。

[0088]

s072、如图2l所示,使用干法刻蚀工艺对所述曝光区域进行刻蚀,形成深度为50~150nm的所述凹槽005,去除所述光刻胶0011。

[0089]

s073、如图2m所示,在750℃~850℃温度下,利用化学气相沉积工艺在复合层002的上表面淀积sio20012,将所述凹槽005填满。

[0090]

s074、如图2n所示,利用化学机械抛光方法去除所述复合层002上表面的sio20012。

[0091]

s08、如图2o~2p所示,在所述第一区域0021上形成al电极003。

[0092]

s081、如图2o所示,在所述复合层002的上表面涂抹光刻胶0013,并对所述第一区域0021曝光。

[0093]

s082、如图2p所示,利用电子束蒸发工艺在所述第一区域0021的上表面淀积厚度为70~90nm的al金属,以形成欧姆接触,去除所述光刻胶0013。

[0094]

s09、如图2q~2r所示,在所述第二区域0022上形成ti电极004。

[0095]

s091、如图2q所示,在所述复合层002、所述al电极003的上表面涂抹光刻胶0014,并对所述第二区域0022曝光。

[0096]

s092、如图2r所示,利用电子束蒸发工艺在所述第二区域0022的上表面淀积厚度为70~90nm的ti金属,以形成肖特基接触,去除光刻胶0014。

[0097]

为了便于理解复合半导体肖特基二极管的结构和有益效果,在此,对本申请的发明构思、涉及原理进行详细描述。

[0098]

发明人对整流效率进行研究,得知整流效率的公式为:

[0099][0100]

式(1)中,p

dc

为整流后输出的直流电对应功率,p

rf

为整流前输入的环境中射频信号功率,η

m

为匹配效率,η

p

是与寄生参数相关的效率,η0是在非线性器件中的转换效率,η

dc_transfer

是直流电从电路转移到负载的效率。

[0101]

公式(1)中,

[0102]

q为品质因数,q

c

为匹配网络元件的品质因数,为了使得匹配效率η

m

最大化,通常q[[q

c

。

[0103]

公式(1)中,

[0104]

r

j

是结电阻,r

s

是串联电阻,c

j

是结电容,f是频率。

[0105]

公式(1)中,

[0106]

p

in

是进入整流器的功率,是零偏电流响应度,r

l

是负载电阻。

[0107]

公式(1)中,

[0108]

因此,综合(1)、(2)、(3)、(4)、(5)式可以得到整流效率η的表达式为:

[0109][0110]

其中,ω=2

·

π

·

f。

[0111]

从公式(6)可以看出,在高频情况下,降低结电容c

j

、串联电阻r

s

、结电阻r

j

可以提高整流效率。同时,增大器件的零偏电流响应度也可以提高整流效率。

[0112]

因此,一方面,发明人考虑从降低结电容c

j

、串联电阻r

s

、结电阻r

j

的角度提高弱能量密度下sbd的整流效率。另一方面,发明人期望从增大器件的零偏电流响应度方向着手,提高弱能量密度下sbd的整流效率。

[0113]

因此,发明人进一步对sbd零偏电流响应度进行研究,得知零偏电流响应度的公式如下式(7):

[0114][0115]

其中,i

(1)

(v)和i

(2)

(v)分别是电流对电压的一阶导函数和二阶导函数。电流公式如下(8)所示(考虑镜像力和隧道效应的影响):

[0116][0117]

由式(8)得到电流对电压的一阶导函数和二阶导函数分别为下式(9)和(10)所示:

[0118]

[0119][0120]

将(9)和(10)带入公式(7),则sbd零偏电流响应度为:

[0121][0122]

式(11)中,其他符号物理意义详见文献《半导体器件物理》。由于在正偏或者零偏的时候,式(11)中的修正项,即第三项很小,所以sbd零偏电流响应度可以简化为式(12):

[0123][0124]

由式(12)可以看出,sbd零偏电流响应度主要由sbd理想因子n来决定。n的值越小,零偏电流响应度就越大,那么sbd的整流效率就越大。其中,理想因子n是电压v关于电流j的一阶偏导数,其公式为:

[0125][0126]

因为lni

‑

v曲线的斜率可以表征为因此式(13)表明,当lni

‑

v曲线的斜率越陡峭,即斜率越大,则越小,则n值越小,那么sbd零偏电流响应度就越大,则sbd的整流效率就越大。也就是说,增大可以提高零偏电流响应度,提高弱能量密度下的电路整流效率。在此需要强调的是,式(13)中的n值并不是从sbd i

‑

v曲线正常工作状态下提取的理想因子,而是从弱能量整流区域提取出来的理想因子。

[0127]

发明人研究发现,sbd弱能量整流区域lni

‑

v曲线斜率与有效理查逊常数金属一侧的势垒高度φ

ns

密切相关,见下式(14),其中

∝

表示正比关系。

[0128][0129]

从式(14)可见,φ

ns

位于式(14)的指数项,可以理解的是,减小φ

ns

可以显著增大因此,发明人对φ

ns

进一步研究,发现有:

[0130]

φ

ns

=w

m

‑

χ

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(15)

[0131]

其中,w

m

为金属功函数,χ为半导体电子亲和能。根据式(15)可知,减小w

m

或者增大χ可以减小φ

ns

,从而实现增大弱能量密度下零偏电流响应度提高弱能量密度下sbd整流效率的目的。

[0132]

具体的,一方面中:

[0133]

现有技术通常采用金属w作为肖特基接触区域的电极,w的金属功函数为4.55ev,并且,业内常用[110]晶向ge,其电子亲和能χ为4.163ev,那么根据式(15)φ

ns

=w

m

‑

χ=4.55

‑

4.163=0.387ev。

[0134]

而本发明实施例采用金属钛(ti)制备肖特基接触区域的电极,其金属功函数为4.33ev,并且采用[100]晶向的pb含量为3.125%的gepb,其电子亲和能为3.968ev。那么根据式(15)φ

ns

=w

m

‑

χ=4.33

‑

3.968=0.362ev。可见,本发明实施例通过使用金属钛(ti)替换金属钨(w)作为肖特基接触区域的电极材料,并且将主体材料从业内常用[110]晶向ge改变为[100]晶向的pb含量为3.125%的gepb,金属一侧的势垒高度φ

ns

变小,则零偏电流响应度增大,因此,整体上能够增大sbd的零偏电流响应度,提高弱能量密度下sbd的整流效率。

[0135]

另一方面,通过采用pb合金化致晶向消除技术,相比于纯ge半导体,得到的gepb合金半导体的电子迁移率得到极大提升,因此能够降低串联电阻,提高整流效率。

[0136]

以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1