静电放电(ESD)保护电路及其操作方法与流程

文档序号:26840303发布日期:2021-10-08 22:12阅读:1671来源:国知局

导航: X技术> 最新专利>电气元件制品的制造及其应用技术

静电放电(esd)保护电路及其操作方法

技术领域

1.本发明的实施例设计静电放电保护电路及其操作方法。

背景技术:

2.小型化集成电路(ic)的最新趋势已导致更小的器件消耗更少的功率, 但比以前提供了更高的速度。由于各种因素,例如更薄的介电层厚度和相 关的降低的介电击穿电压,小型化工艺还增加了器件对静电放电(esd) 事件的敏感性。esd是电子电路损坏的原因之一,也是半导体先进技术中 的考虑因素之一。

技术实现要素:

3.根据本发明的一个方面,提供了一种静电放电(esd)保护电路,包 括:第一二极管,位于半导体晶圆中,并且耦接到输入输出(io)焊盘; 第二二极管,位于半导体晶圆中,并且耦接到第一二极管和io焊盘;和 esd钳位电路,位于半导体晶圆中,耦接到第一二极管和第二二极管,esd 钳位电路包括半导体晶圆中的第一信号抽头区域,第一信号抽头区域耦接 到第一电压源,第一二极管耦接到第一信号抽头区域并且被配置为与esd 钳位电路共享第一信号抽头区域。

4.根据本发明的另一个方面,提供了静电放电保护电路,包括:第一二 极管,位于半导体晶圆中,并且耦接到第一焊盘;第二二极管,位于半导 体晶圆中,并且耦接到第一二极管和第一焊盘;内部电路,耦接到第一二 极管和第二二极管;以及esd钳位电路,位于半导体晶圆中,通过第一节 点耦接到第一二极管并通过第二节点耦接到第二二极管,esd钳位电路包 括耦接到电压源的第一信号抽头区域和耦接到参考电压源的第二信号抽头 区域,其中,第一二极管耦接到第一信号抽头区域并被配置为与esd钳位 电路共享第一信号抽头区域;以及第二二极管耦接到第二信号抽头区域并 被配置为与esd钳位电路共享第二信号抽头区域。

5.根据本发明的又一个方面,提供了一种操作静电放电(esd)保护电 路的方法,方法包括:在第一节点上接收第一esd电压,第一esd电压 大于电压源的电源电压,第一esd电压对应于第一esd事件;导通第一 二极管,从而将第一esd电流从第一二极管的第一阳极传导到第一二极管 的第一阴极;将第一esd电流从第一二极管的第一阴极传导到esd钳位 电路的第一信号抽头;以及通过esd钳位电路放电第一esd事件的第一 esd电流。

附图说明

6.当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方 面。应该强调,根据工业中的标准实践,各个部件未按比例绘制并且仅用 于说明的目的。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增 大或减小。

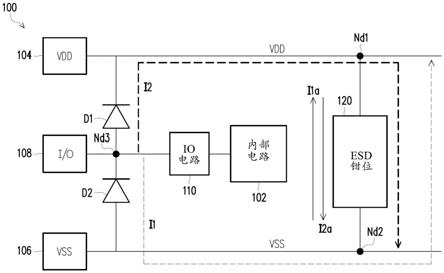

7.图1是根据一些实施例的集成电路的示意框图。

8.图2是根据一些实施例的集成电路的示意框图。

9.图3a是根据一些实施例的集成电路的截面图。

10.图3b是根据一些实施例的集成电路的截面图。

11.图4是根据一些实施例的集成电路的截面图。

12.图5是根据一些实施例的操作esd电路的方法的流程图。

13.图6是根据一些实施例的制造esd电路的方法的流程图。

14.图7a

‑

图7e是根据一个或多个实施例的集成电路的截面图。

具体实施方式

15.以下公开内容提供了许多用于实现本发明的不同特征不同的实施例或 实例。下面描述了组件和布置的具体实施例或实例以简化本发明。当然, 这些仅是实例而不旨在限制。例如,在以下描述中,在第二部件上方或者 上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并 且也可以包括在第一部件和第二部件之间可以形成额外的部件,从而使得 第一部件和第二部件可以不直接接触的实施例。此外,本发明可以在各个 示例中重复参考数字和/或字母。该重复是为了简单和清楚的目的,并且其 本身不指示讨论的各个实施例和/或配置之间的关系。

16.此外,为了便于描述,本文中可以使用诸如“在

…

下方”、“在

…

下 面”、“下部”、“在

…

上面”、“上部”等的间隔关系术语,以描述如 图中所示的一个元件或部件与另一元件或部件的关系。除了图中所示的方 位外,间隔关系术语旨在包括器件在使用或操作工艺中的不同方位。器件 可以以其它方式定位(旋转90度或在其它方位),并且在本文中使用的间 隔关系描述符可以同样地作相应地解释。

17.在一些实施例中,esd保护电路包括第一二极管、第二二极管和esd 钳位电路。第一二极管在半导体晶圆中,并且耦接到输入输出(io)焊盘。 第二二极管在半导体晶圆中,并且耦接到第一二极管和io焊盘。esd钳位 电路在半导体晶圆中,并且耦接到第一二极管和第二二极管。esd钳位电 路在半导体晶圆中包括第一信号抽头区域和第二信号抽头区域。第一信号 抽头区域耦接到第一电压源。第二信号抽头区域耦接到与第一电压源不同 的第二电压源。

18.第一二极管耦接到esd钳位电路并被配置为与esd钳位电路共享第 一信号抽头区域。第二二极管耦接到esd钳位电路并被配置为与esd钳 位电路共享第二信号抽头区域。在一些实施例中,通过第一二极管与esd 钳位电路共享第一信号抽头区域,以及第二二极管与esd钳位电路共享第 二信号抽头区域,本公开的esd保护电路所占面积小于其他方法。

19.在一些实施例中,通过第一二极管与esd钳位电路共享第一信号抽头 区域,以及通过第二二极管与esd钳位电路共享第二信号抽头区域,本公 开的esd保护电路具有比其他方法更少的信号抽头,导致本公开的esd 保护电路具有比其他方法小的电阻。在一些实施例中,通过具有比其他方 法小的电阻,本公开的esd保护电路具有较低的钳位电压,并且在操作上 比其他方法更快。

20.图1是根据一些实施例的集成电路100的示意框图。

21.集成电路100包括内部电路102、电压源节点104、参考电压源节点 106、输入/输出(io)焊盘108、二极管d1、二极管d2、io电路110和 esd钳位电路120。在一些实施例中,至少集成电路100、200(图2)或 300a

‑

300b(图3a

‑

图3b)被并入单个集成电路(ic)或单个半导体

衬底 上。在一些实施例中,至少集成电路100、200(图2)或300a

‑

300b(图 3a

‑

图3b)包括结合在一个或多个单个半导体衬底上的一个或多个ic。

22.内部电路102耦接到io电路110。在一些实施例中,内部电路102还 耦接到io焊盘108、二极管d1和二极管d2。内部电路102被配置为通过 io电路110从io焊盘108接收io信号。在一些实施例中,内部电路102 耦接到电压源节点104(例如,vdd)和参考电压源节点106(例如,vss)。 在一些实施例中,内部电路102被配置为接收来自电压源节点104的电源 电压vdd(例如,vdd),以及来自参考电压源节点106的参考电压vss (例如,vss)。

23.内部电路102包括被配置为生成或处理由io焊盘108接收或输出到io 焊盘108的io信号的电路。在一些实施例中,内部电路102包括被配置为 以低于电压源节点104的电源电压vdd的电压工作的核心电路。在一些实 施例中,内部电路102包括至少一个n型或p型晶体管器件。在一些实施 例中,内部电路102至少包括逻辑门单元。在一些实施例中,逻辑门单元 包括与(and)、或(or)、与非(nand)、或非(nor)、异或(xor)、 inv(反相)、与或反相(aoi)、或与反相(oai)、mux(复用器)、 触发器、buff(缓存)、锁存器、延迟或时钟单元。在一些实施例中,内 部电路102至少包括存储器单元。在一些实施例中,存储器单元包括静态 随机存取存储器(sram)、动态ram(dram)、电阻式ram(rram)、 磁阻式ram(mram)或只读存储器(rom)。在一些实施例中,内部 电路102包括一个或多个有源或无源元件。有源元件的示例包括但不限于 晶体管和二极管。晶体管的示例包括但不限于金属氧化物半导体场效应晶 体管(mosfet)、互补金属氧化物半导体(cmos)晶体管、双极结型晶 体管(bjt)、高压晶体管、高频晶体管、p沟道和/或或n沟道场效应晶体 管(pfet/nfet)等)、finfet和源/漏电压升高的平面mos晶体管。 无源元件的示例包括但不限于电容器、电感器、熔断器和电阻器。

24.电压源节点104在节点nd1处耦接到二极管d1和esd钳位电路120。 参考电压源节点106在节点nd2处耦接到二极管d2和esd钳位电路120。 电压源节点104被配置为接收用于内部电路102的正常操作的电源电压 vdd。类似地,参考电压源节点106被配置为接收用于内部电路102的正 常操作的参考电源电压vss。节点104是电压源焊盘。在一些实施例中, 至少参考电压源节点106是参考电压源焊盘。在一些实施例中,焊盘至少 是导电表面、引脚、节点或总线。电压源节点104或参考电压源节点106 也被称为电源电压总线或电源电压轨。在图1、图2或图3a

‑

图3b的示例 配置中,电源电压vdd是正电源电压,电压电源节点104是正电源电压, 参考电源电压vss是接地电源电压,参考电压电源节点106是接地电压端 子。其他电源布置在本公开的范围内。

25.io焊盘108通过节点nd3耦接到io电路110。io焊盘108通过io电 路110耦接到内部电路102。在一些实施例中,io电路110不包括在集成 电路100中,并且io焊盘直接耦接到内部电路102。io焊盘108配置为从 io电路110接收io信号,或配置为将io信号输出到io电路110。焊盘 108至少是耦接到io电路110或内部电路102的引脚。io焊盘108是连 接到io电路110或内部电路102的节点、总线或导电表面。

26.二极管d1耦接在电压源节点104和io焊盘108之间。二极管d1耦 接在节点nd1和节点nd3之间。二极管d1的阳极耦接到节点nd3、io电 路110、io焊盘108和二极管d2的阴极。二极管d1的阴极耦接到电压源 节点104、esd钳位电路120和节点nd1。在一些实施例中,二极管d1的 阴极通过节点nd1耦接到esd钳位电路120。在一些实施例中,二极管 d1是上拉二极

管或称为p+二极管。例如,在这些实施例中,在p阱区域 (例如,图3a

‑

图3b的阱322)和n阱区域(未示出)之间形成p+二极 管,并且n阱区域被连接至vdd(参见图3a

‑

图3b)。在一些实施例中, 二极管d1是垂直阱二极管。二极管d1的其他二极管类型在本公开的范围 内。

27.二极管d2耦接在参考电压源节点106和io焊盘108之间。二极管d2 耦接在节点nd3和节点nd2之间。二极管d2的阳极耦接到参考电压源节 点106、esd钳位电路120和节点nd2。二极管d2的阴极耦接到节点nd3、 io电路110、io焊盘108和二极管d1的阳极。在一些实施例中,二极管 d2是下拉二极管或称为n+二极管。例如,在这些实施例中,在n阱区(例 如,图3a

‑

图3b的阱332)和p阱(未示出)之间形成n+二极管,并且p 衬底连接到地或vss。在一些实施例中,二极管d2是垂直阱二极管。二 极管d2的其他二极管类型在本公开的范围内。

28.二极管d1和d2配置为对内部电路102或集成电路100的正常行为(例 如,没有esd条件或事件)具有最小的影响。在一些实施例中,当esd 电压或esd电流发生时发生esd事件,将高于内部电路102的正常操作 期间电压或电流水平的电压或电流施加到至少电压源节点104、参考电压 源节点106或io焊盘108。

29.当没有esd事件发生时,二极管d1和d2不影响集成电路100的操 作。在esd事件期间,二极管d1被配置为取决于二极管d1是否被正向 偏置或反向偏置以及电压源节点104和io焊盘108的电压电平,而在电压 源节点104和io焊盘108之间传递电压或电流。

30.例如,在esd应力或事件的正至vdd(pd)模式期间,二极管d1 正向偏置,并配置为将电压或电流从io焊盘108传输到电压源节点104。 当电压源节点104(例如,vdd)接地并且参考电压源节点106(例如, vss)浮置时,将正esd应力或esd电压(至少大于电源电压vdd)施 加到io焊盘108。

31.例如,在esd应力或esd事件的负至vdd(nd)模式期间,二极管 d1被反向偏置,并且被配置为将电压或电流从电压源节点104传递到io 焊盘108。当电压源节点104(例如,vdd)接地并且参考电压源节点106 (例如,vss)浮置时,io焊盘108接收到负的esd应力。

32.在esd事件期间,二极管d2被配置为根据二极管d2是正向偏置还 是反向偏置以及参考电压源节点106的电压电平在参考电压源节点106和 io焊盘108之间传输电压或电流。

33.例如,在esd应力或esd事件的正向vss(ps)模式期间,二极管d2反向偏置,并配置为将电压或电流从io焊盘108传输到参考电压源节 点106。正的esd应力或esd电压(至少大于参考电源电压vss)被施加 到io焊盘108,而电压电源节点104(例如vdd)浮置且参考电压电源节 点106(例如vss)接地。

34.例如,在esd应力或事件的负极至vss(ns)模式期间,二极管d2 正向偏置,并配置为将电压或电流从参考电压源节点106传递到io焊盘 108。在ns模式下,io焊盘108接收到负的esd应力,而电压源节点104 (例如,vdd)浮置且参考电压源节点106(例如,vss)接地。

35.其他类型的二极管、至少二极管d1或d2的配置和布置在本公开的范 围内。

36.io电路110耦接到io焊盘108、内部电路102、二极管dl和d2以 及节点nd3。io电路耦接在节点nd3与内部电路102之间。在一些实施例 中,io电路是被配置为缓冲发送到内部电路102或来自内部电路102的信 号的io缓冲器。在一些实施例中,io电路110至少包括上述逻辑门单元。 io电路110的其他类型的电路、配置和布置在本公开的范围内。

37.esd钳位电路120耦接在电压源节点104(例如,电源电压vdd) 和参考电压源节点106(例如,vss)之间。esd钳位电路120耦接在节点 nd1和节点nd2之间。esd钳位电路120通

过节点nd1耦接到二极管d1。 esd钳位电路120通过节点nd2耦接到二极管d2。

38.当没有esd事件发生时,esd钳位电路120被关闭。例如,当没有 esd事件发生时,esd钳位电路120被关闭,并且因此在内部电路102的 正常操作期间是不导电的器件或电路。换句话说,在没有esd事件的情况 下,esd钳位电路120被关闭或不导电。

39.如果发生esd事件,则esd钳位电路120被配置为感测esd事件, 并且被配置为导通并在电压源节点104(例如,电源电压vdd)或节点ndl 与参考电源节点106(例如,vss)或节点nd2之间提供电流分流路径, 从而放电esd电流。例如,当发生esd事件时,esd钳位电路120两端 的电压差等于或大于esd钳位电路120的阈值电压,并且esd钳位电路 120导通,从而在电压源节点104(例如vdd)和参考电压源节点106(例 如vss)之间传导电流。

40.在esd事件期间,esd钳位电路120被配置为导通并且在从参考电压 源节点106(例如,vss)到电压源节点104(例如vdd)的正向esd方 向上放电esd电流(例如,电流i1a)。为了简单起见,在图1中示出了 电流i1a在节点nd2至节点nd1之间,但是应当理解,电流i1a是从参考 电压源节点106(例如,vss)到电压源节点104(例如,vdd)。

41.在esd事件期间,esd钳位电路120被配置为导通并且在(例如,电 流i2a)从电压源节点104(例如vdd)到参考电压源节点106(例如vss) 的esd反向方向上放电esd电流。为了简单起见,在图1中示出了电流 i2a在节点nd1至节点nd2之间,但是应当理解,电流i2a是从电压源节 点104(例如,vdd)到参考电压源节点106(例如,vss)。

42.在参考电压源节点106上的正esd浪涌期间,esd钳位电路120被配 置为导通并且在从参考电压源节点106(例如,vss)到电压源节点节点 104(例如vdd)的正向esd方向上放电esd电流i1a。在一些实施例中, esd钳位电路120被配置为在esd的ps模式(如上所述)之后导通,并 且在从节点nd3到节点nd2以及从节点nd1到电压源节点104(例如vdd) 的正向esd方向上放电esd电流i1。

43.在电压源节点104上的正esd浪涌期间,esd钳位电路120被配置为 导通并且在从电压源节点104(例如vdd)到参考电压源节点106(例如 vss)的esd反向方向上放电esd电流i2a。在一些实施例中,esd钳位 电路120被配置为在esd的pd模式(如上所述)之后导通,并且在从节 点nd3到节点nd1以及从节点nd2到参考电压源节点106(例如,vss) 的反向esd方向上放电esd电流i2。

44.在一些实施例中,esd钳位电路120是瞬态钳位。例如,在一些实施 例中,esd钳位电路120被配置为处理瞬态或esd事件,例如,来自esd 事件的电压和/或电流的快速变化。在瞬态或esd期间,esd钳位电路120 被配置为在esd事件可引起集成电路100中的一个或多个元件损坏之前导 通,以在电压源节点104(例如,电源电压vdd)和参考电压源节点106 (例如,vss)之间提供分流路径。在一些实施例中,esd钳位电路120 被配置为关闭比导通慢。

45.在一些实施例中,esd钳位电路120是静态钳位器。在一些实施例中, 静态钳位器被配置为提供静态或稳态电压和电流响应。例如,静态钳位器 通过固定电压电平导通。

46.在一些实施例中,esd钳位电路120包括大nmos晶体管,其被配置 为在不进入esd钳位电路120的雪崩击穿区域的情况下承载esd电流。 在一些实施例中,实现了esd钳位电路120而内部没有雪崩结。esd钳 位电路120,也被称为“非骤回保护方案”。

47.其他类型的钳位电路、esd钳位电路120的配置和布置也在本公开的 范围内。

48.集成电路100中的其他电路配置或数量在本公开的范围内。

49.图2是根据一些实施例的集成电路200的示意框图。

50.集成电路200是集成电路100的实施例,因此省略类似的详细描述。 例如,集成电路200包括集成电路100的至少部分,集成电路100被包括 为衬底202的部分。尽管图2示出了集成电路100的部分,但是应当理解, 集成电路200可以被修改为包括集成电路100的每个部件,并且因此为简 洁起见,省略了类似的详细描述。

51.与图1、图2、图3a

‑

图3b及图4中的一个或多个相同或相似的部件 被赋予相同的附图标记,并省略其详细说明。

52.集成电路200包括参考电压源节点104、参考电压源节点106、io焊 盘108、二极管d1、二极管d2、衬底202和钳位电路220。

53.集成电路200是图1的集成电路100的变体,并且因此省略类似的详 细描述。与集成电路100相比,esd钳位电路220代替了图1的esd钳位 电路120,并且因此省略类似的详细描述。

54.esd钳位电路220形成在衬底202上。衬底202在第一方向x上延伸。 衬底202具有前侧203和在第二方向y上与前侧203相对的背侧205。第 二方向y不同于第一方向x。在一些实施例中,在晶圆减薄期间已经去除 了衬底202的块(bulk)。在一些实施例中,衬底202是超功率导轨(spr) 技术或工艺的部分。在一些实施例中,衬底202是绝缘体上硅(soi)技术 或工艺。在一些实施例中,至少二极管d1或d2形成在衬底202上。其他 类型的衬底技术或用于衬底202的工艺在本公开的范围内。

55.esd钳位电路220包括信号抽头250和信号抽头252。

56.在一些实施例中,至少信号抽头252对应于阱抽头。在一些实施例中, 阱抽头是将衬底202的阱区域(如图3a

‑

图3b所示)耦接到电压源节点104 (例如,电源电压vdd)的导电引线。例如,在一些实施例中,阱区在p 型衬底上的n型阱中包括重掺杂的n区。在一些实施例中,重掺杂的n区 域通过阱抽头耦接到电压源节点104(例如,电源电压vdd),从而设置 n型阱的电势以防止从相邻的源极/漏极区域泄漏到阱中。

57.在一些实施例中,至少信号抽头250对应于衬底抽头。在一些实施例 中,衬底抽头是将衬底202的区域耦接到参考电压源节点106(例如,电 源电压vss)的导电引线。例如,在一些实施例中,衬底202的区域包括 形成在p型衬底中的重掺杂p区域。在一些实施例中,重掺杂的p区域通 过衬底抽头耦接到参考电压源节点106(例如,参考电源电压vss),从 而设置衬底202的电势以防止从相邻的源极/漏极区域泄漏。

58.通过使用信号抽头250和252,减小了衬底202的电阻和集成电路200 中不希望有的正反馈。在一些实施例中,至少信号抽头250或252被配置 为限制电源或接地连接到衬底202的阱(在图3a

‑

图3b中示出)之间的电 阻。在一些实施例中,至少信号抽头250或252的使用导致衬底202中较 少的漂移,从而防止闩锁效应。

59.信号抽头250耦接到衬底202的背侧203上的电压源节点104(例如 电压vdd)。信号抽头250还耦接到二极管d1的阴极。

60.信号抽头252耦接到衬底202的背侧203上的参考电压源节点106(例 如,电压vss)。信号抽头252还耦接到二极管d2的阳极。

61.io焊盘108在衬底202的背侧203上,并且耦接到二极管d1的阳极 和二极管d2的阴

极。在一些实施例中,集成电路200电连接到衬底202 的背侧203上的一个或多个其他封装结构(未示出)。

62.在一些实施例中,二极管d1配置成与esd钳位电路220共享信号抽 头250,并且二极管d2配置成与esd钳位电路220共享信号抽头252。在 一些实施例中,通过与esd钳位器共享信号抽头250在电路220中,二极 管d1不包括信号抽头,从而导致集成电路200比其他方法占据更少的面积。 在一些实施例中,通过与esd钳位电路220共享信号抽头252,二极管d2 不包括信号抽头,导致集成电路200比其他方法占据更少的面积。

63.通过至少二极管d1或d2不包括对应的信号抽头,集成电路200具有 较小的电阻,因为集成电路200包括比其他方法更少的信号抽头。

64.其他类型的钳位电路、esd钳位电路120的配置和布置也在本公开的 范围内。

65.集成电路200中的电路的其他配置或数量在本公开的范围内。

66.图3a是根据一些实施例的集成电路300a的截面图。

67.集成电路300a是图1的至少集成电路100或图2的集成电路200的实 施例,因此省略类似的详细描述。

68.虽然图关于图1的集成电路100或图2的集成电路200的部分描述图 3a

‑

图3b,但是图3a至图3b的教导也可应用于集成电路100或200的其 他部分(至少关于图3a至图3b未描述),因此为简洁起见,省略了类似 的详细描述。

69.集成电路300a包括二极管302、二极管304、esd钳位电路310和衬 底320。

70.二极管302是图1

‑

图2的二极管d1的实施例,二极管304是图1

‑

图2 的二极管d2的实施例。参照图1

‑

图2,esd钳位电路310是图1的esd 钳位电路120的实施例。衬底320是图2的衬底202的实施例,因此省略 类似的详细描述。

71.在衬底320上至少形成二极管302、二极管d2或esd钳位电路310。 在一些实施例中,在衬底320的前侧205上至少形成二极管302、二极管 d2或esd钳位电路310。

72.衬底320具有在第二方向y上与前侧205相对的前侧305和背侧303。 衬底320在第一方向x上具有与侧面326205相对的侧面326和侧面336。 因此,在晶圆减薄期间已经去除了衬底320的块。在一些实施例中,衬底 320是超功率导轨(spr)技术或过程的部分。在一些实施例中,衬底320 是绝缘体上硅(soi)技术或工艺。在一些实施例中,衬底320也被称为晶 圆。在一些实施例中,衬底320包括绝缘层321。绝缘层321在衬底320 的背侧303和前侧305之间。在一些实施例中,绝缘层321是非导电氧化 物材料。在一些实施例中,在晶圆减薄和氧化物再生之后,在衬底320的 背侧303上形成绝缘层321。在一些实施例中,前侧305和303背侧通过 至少绝缘层321彼此电隔离。在一些实施例中,绝缘层321包括介电材料, 介电材料包括氧化物或另一种合适的绝缘材料。

73.衬底320是p型衬底。在一些实施例中,衬底320是n型衬底。在一 些实施例中,衬底320包括元素半导体,包括晶体、多晶或非晶结构中的 硅或锗;化合物半导体,包括碳化硅,砷化镓,磷化镓,磷化铟,砷化铟 和锑化铟;合金半导体,包括sige,gaasp,alinas,algaas,gainas, gainp和gainasp;任何其他合适的材料;或其组合。在一些实施例中,合 金半导体衬底具有梯度sige部件,其中si和ge组成从梯度sige部件的 一个位置处的一个比率改变为另一位置处的另一比率。在一些实施例中, 合金sige形成在硅衬底上方。在一些实施例中,衬底320是应变sige衬 底。在一些实施例中,半导体衬底具有绝缘体上半导体结构,例

如绝缘体 上硅(soi)结构。在一些实施例中,半导体衬底包括掺杂的外延层或掩埋 层。在一些实施例中,化合物半导体衬底具有多层结构,或者衬底包括多 层化合物半导体结构。

74.二极管302包括阳极302a、栅极结构302b、阴极302c、阴极302d、 沟道区302e和阱322。二极管302是垂直阱二极管。在一些实施例中,二 极管302是纳米片垂直阱二极管。在一些实施例中,二极管302形成在衬 底320的前侧305上。二极管302的其他二极管类型在本公开的范围内。

75.二极管302对应于图1

‑

图2的二极管d1,省略了类似的详细描述。阳 极302a对应于图1

‑

图2的二极管d1的阳极,阴极302c和302d对应于图 1

‑

图2的二极管d1的阴极,沟道区域302e与二极管d1的沟道区域对应, 因此省略相同的详细说明。

76.阱322形成在衬底320中。阱322具有p型掺杂剂杂质,并且被称为 p型阱。在一些实施例中,阱322具有n型掺杂剂杂质,并且被称为n型 阱。

77.阱322包括区域324。区域324嵌入在阱322中。区域324是重掺杂 的p区域。在一些实施例中,区域324是重掺杂的n区域。

78.阳极302a包括阱322和区域324。阳极302a是在阱322中具有p型掺 杂剂的p型有源区域。

79.阴极302c是具有n型掺杂剂的n型有源区,并且位于阱322上。阴 极302d是具有n型掺杂剂的n型有源区,并且位于阱322上。至少阴极 302c或302d是具有p型掺杂剂的p型有源区。阴极302c和阴极302d在 第一方向x上彼此分开。在一些实施例中,阴极302c和阴极302d是并联 耦接在一起的两个二极管的对应阴极。示出了具有两个阴极(例如,阴极 302c和302d)和单个阳极(例如,阳极302a)的集成电路300a

‑

300b。其 他数量的阴极302c或302d和/或阳极302a在本公开的范围内。

80.阳极302a和阴极302c一起形成pn结,阳极302a和阴极302d一起形 成另一个pn结。在一些实施例中,至少阴极302c或阴极302d在衬底320 上方延伸。在一些实施例中,阴极302c的至少顶表面或阴极302d的顶表 面与衬底320的前侧305齐平。

81.栅极结构302b至少部分在阱322上方,并且在阴极302c和阴极302d 之间。在一些实施例中,栅极结构302b是电浮置的。在一些实施例中,栅 极结构302b电耦接到阴极302c和302d。沟道区302e耦接阴极302c和阴 极302d。在一些实施例中,沟道区302e在阱322中。

82.在一些实施例中,二极管302不包括信号抽头区域。在一些实施例中, 二极管302被配置为与esd钳位电路310共享信号抽头区域350。例如, 在一些实施例中,二极管302通过至少导电结构电耦接到esd钳位电路310 的信号抽头区域350。在一些实施例中,通过与esd钳位电路310共享信 号抽头区域350,集成电路300a或300b比其他方法占用更少的面积。在 一些实施例中,通过与esd钳位电路310共享信号抽头区域350,集成电 路300a或300b具有比其他方法更少的信号抽头,导致集成电路300a或 300b具有比其他方法更少的电阻并且更简单的布线。

83.其他类型的电路、配置和布置二极管302在本公开的范围内。

84.二极管304包括阳极304a、栅极结构304b、阴极304c、阴极304d、 沟道区304e和阱332。二极管304是垂直阱二极管。在一些实施例中,二 极管304是纳米片垂直阱二极管。在一些实施例中,二极管304形成在衬 底320的前侧305上。用于二极管304的其他二极管类型在本公开的范围 内。

85.二极管304对应于图1

‑

图2的二极管d2,省略了类似的详细描述。阳 极304a对应于图1

‑

图2的二极管d2的阳极,阴极304c和304d对应于图 1

‑

图2的二极管d2的阴极,沟道区域304e对应于二极管d2的沟道区域, 因此省略相同的详细说明。

86.阱332形成在衬底320中。阱332具有n型掺杂剂杂质,并且被称为 n型阱。在一些实施例中,阱332具有p型掺杂剂杂质,并且被称为p型 阱。

87.阱332包括区域334。区域334嵌入在阱332中。区域334是重掺杂 的n区域。在一些实施例中,区域334是重掺杂的p区域。

88.阳极304a包括阱332和区域334。阳极304a是在阱332中具有n型 掺杂剂的n型有源区域。

89.阴极304c是具有p型掺杂剂的p型有源区,并且位于阱332上。阴极 304d是具有p型掺杂剂的p型有源区,并且位于阱332上。至少阴极304c 或304d是具有n型掺杂剂的n型有源区。阴极304c和阴极304d在第一 方向x上彼此分离。在一些实施例中,阴极304c和阴极304d是并联耦接 在一起的两个二极管的对应阴极。示出了具有两个阴极(例如,阴极304c 和304d)和单个阳极(例如,阳极304a)的集成电路300a

‑

300b。其他数 量的阴极304c或304d和/或阳极304a在本公开的范围内。

90.阳极304a和阴极304c一起形成pn结,并且阳极304a和阴极304d一 起形成另一个pn结。在一些实施例中,至少阴极304c或阴极304d在衬底 320上方延伸。在一些实施例中,阴极304c的顶表面或阴极304d的顶表面 至少与衬底320的前侧305齐平。

91.栅极结构304b至少部分在阱332上方,并且在阴极304c和阴极304d 之间。在一些实施例中,栅极结构304b是电浮置的。在一些实施例中,栅 极结构304b电耦接到阴极304c和304d。沟道区304e耦接阴极304c和阴 极304d。在一些实施例中,沟道区304e在阱332中。

92.在一些实施例中,二极管304不包括信号抽头区域。在一些实施例中, 二极管304被配置为与esd钳位电路310共享信号抽头区域352。例如, 在一些实施例中,二极管304通过至少导电结构电耦接到esd钳位电路310 的信号抽头区域352。在一些实施例中,通过与esd钳位电路310共享信 号抽头区域352,集成电路300a或300b比其他方法占用更少的面积。在 一些实施例中,通过与esd钳位电路310共享信号抽头区域352,集成电 路300a或300b具有比其他方法更少的信号抽头,从而导致集成电路300a 或300b具有比其他方法更少的电阻并且更简单的布线。

93.其他类型的电路、配置和布置二极管304在本公开的范围内。

94.esd钳位电路310包括n型金属氧化物半导体(nmos)晶体管n1、 nmos晶体管n2、信号抽头区域250和信号抽头区域252。nmos晶体管 n1与nmos晶体管n2串联耦接。为了便于说明,在图3a

‑

图3b中未将 nmos晶体管n1和nmos晶体管n2示出为耦接到其他元件。在一些实 施例中,至少nmos晶体管n1或n2是p型金属氧化物半导体(pmos) 晶体管。

95.nmos晶体管n1包括漏极区310a、栅极结构310b、源极区310c、 沟道区310d和阱区360。

96.阱区360形成在衬底320中。阱区360具有p型掺杂剂杂质,并且被 称为p型阱。在一些实施例中,阱区360具有n型掺杂剂杂质,并且被称 为n型阱。

97.栅极结构310b在阱区360上方。漏极区310a是具有注入在阱区360 中的n型掺杂剂的n型有源区。源极区310c是具有注入阱区310a中的n 型掺杂剂的n型有源区。在一些实施

例中,至少源极区310c或漏极区310a 在衬底320上方延伸。沟道区310d在阱区360中并且耦接漏极区310a和 源极区310c。

98.nmos晶体管n2包括漏极区312a、栅极结构312b、源极区312c、沟 道区312d和阱区362。

99.阱区362形成在衬底320中。阱区362具有p型掺杂剂杂质,并且被 称为p型阱。在一些实施例中,阱区362具有n型掺杂剂杂质,并且被称 为n型阱。

100.栅极结构312b在阱区362上方。漏极区312a是具有注入在阱区362 中的n型掺杂剂的n型有源区。源极区312c是具有n型有源区的n型有 源区。在阱区312a中注入的掺杂剂。在一些实施例中,至少源极区312c 或漏极区312a在衬底320上方延伸。沟道区312d在阱区362中,并且耦 接漏极区312a和源极区312c。

101.信号抽头区域350是图2的信号抽头区域250的实施例。信号抽头区 域352是图2的信号抽头区域252的实施例,因此省略类似的详细描述。

102.信号抽头区域350在阱区域360中。信号抽头区域350耦接到导电结 构344。信号抽头区域350和导电结构344中的每一个都耦接到对应于电 压源端子的节点nd1(例如,电压vdd)。信号抽头区域350通过导线390 还耦接到二极管d1的阴极302c和二极管d1的阴极302d。在一些实施例 中,esd钳位电路310的信号抽头区域350与二极管302共享。

103.在一些实施例中,信号抽头区域350是阱抽头,并且将衬底320的阱 区域360电耦接到电压源节点104(例如,电源电压vdd)。在一些实施 例中,信号抽头区域350在衬底320上的阱区域360中包括重掺杂的n区 域(例如,p型)。在一些实施例中,重掺杂的n区域通过阱抽头耦接到 电压源节点104(例如,电源电压vdd),从而设置阱区域360的电势(例 如,n型)以防止从相邻漏极区域进入阱区域360。在一些实施例中,信号 抽头区域350在衬底320上的阱区域360中包括重掺杂的p区域。

104.信号抽头区域352在阱区域362中。在一些实施例中,阱区域362和 360是同一连续阱的部分。在一些实施例中,阱区362和360是分开的不 连续阱。信号抽头区域352耦接到导电结构346。信号抽头区域352和导 电结构346中的每一个都耦接到与参考电压源端子(例如,电压vss)相 对应的节点nd2。信号抽头区域352还通过导线392耦接到二极管d2的阴 极304c和二极管d2的阴极304d。在一些实施例中,esd钳位电路310的 信号抽头区域352与二极管304共享。

105.在一些实施例中,信号抽头区域352是衬底抽头,并且将衬底320的 阱区域362电耦接到参考电压源节点106(例如,电源电压vss)。在一 些实施例中,信号抽头区域352在衬底320上的阱区域362中包括重掺杂 的p区域(例如,p型)。在一些实施例中,重掺杂的p区域通过衬底抽 头耦接到参考电压源节点106(例如,电源电压vss),从而设置衬底320 的电势(例如,p型)以防止从相邻源/漏极泄漏。在一些实施例中,信号 抽头区域352在衬底320上的阱区域362中包括重掺杂的n区域。

106.二极管d1的阴极302c、二极管d1的阴极302d和信号抽头区域350 中的每一个都通过导线390耦接在一起,导线390对应于图1

‑

图2的节点 nd1。

107.二极管d2的阴极304c、二极管d2的阴极304d和信号抽头区域352 中的每一个都通过导线392耦接在一起,导线392对应于图1

‑

图2的节点 nd2。

108.在一些实施例中,图3a

‑

图3b的esd钳位电路310的漏极区域310a 和源极区域310c

或漏极区域312a和源极区域312c被去除。图3a至图3b 中的氧化物定义区域被称为氧化物定义(od)区域,氧化物定义区域限定 了图3a

‑

图3b的nmos晶体管n1或n2的源极或漏极扩散区域。

109.在一些实施例中,至少漏极区310a或312a是延伸的漏极区,并且具 有比至少源极区310c或312c更大的尺寸。在至少一个实施例中,硅化物 层(未示出)覆盖至少漏极区310a或312a的部分而不是全部。漏极区310c 的这种部分硅化的配置改善了esd钳位电路310的nmos晶体管n1或 n2免受esd事件的自保护。在至少一个实施例中,至少漏极区310a或312a 被完全硅化。

110.栅极结构310b布置在漏极区310a和源极区310c之间。栅极结构312b 布置在漏极区312a和源极区312c之间。在一些实施例中,栅极结构310b 和栅极结构312b被电耦接在一起。

111.在一些实施例中,至少栅极结构302b、304b、310b或312b是金属栅 极,并且包括诸如金属的导电材料。在一些实施例中,至少栅极结构302b、 304b、310b或312b包括多晶硅(在本文中也称为“poly”)。

112.在一些实施例中,至少沟道区302e,304e,310d或312d包括根据鳍 式场效应晶体管(finfet)互补金属

‑

氧化物

‑

半导体(cmos)技术的鳍。 在一些实施例中,至少沟道区302e、304e、310d或312d包括纳米片晶体 管的纳米片。在一些实施例中,至少沟道区302e、304e、310d或312d包 括纳米线晶体管的纳米线。在一些实施例中,根据平面cmos技术,至少 沟道区302e、304e、310d或312d没有鳍。其他类型的晶体管在本公开的 范围内。

113.esd钳位电路310的其他类型的电路、配置和布置在本公开的范围内。

114.集成电路300a还包括一个或多个浅沟槽隔离(sti)区域328a、328b、 328c或328d。

115.sti区域328a与二极管304的阳极304a相邻。sti区域328b在二极 管302与esd钳位电路310之间。sti区域328c在二极管304与esd钳 位电路310之间。sti区域328d与二极管302的阴极302d相邻。

116.sti区域328a被配置为将二极管304的部分与集成电路300a或300b 的其他部分(未示出)电隔离。sti区域328b被配置为将二极管304的部 分和esd钳位电路310的部分彼此电隔离。在一些实施例中,sti区域328c 被配置为将二极管302的至少部分和esd钳位电路310的部分彼此电隔离。 sti区域328d被配置为将二极管302的部分与集成电路300a或300b的其 他部分(未示出)电隔离。

117.在一些实施例中,至少sti区域328a、328b、328c或328d不包括在 集成电路300a或300b中。在一些实施例中,在至少集成电路300a或300b 中,至少sti 328a、328b、328c或328d被对应的伪单元代替。在一些实施 例中,伪单元是伪器件。在一些实施例中,伪器件是非功能晶体管或非功 能二极管器件。

118.在一些实施例中,阱区322和阱区360是同一连续阱的部分。在一些 实施例中,阱区域322和360是分开的不连续阱,并且sti区域328位于 它们之间。

119.在一些实施例中,阱区332和阱区362是同一连续阱的部分。在一些 实施例中,阱区域322和362是分开的不连续阱,并且sti区域338位于 它们之间。

120.在一些实施例中,阱区360位于阱区362和阱区322之间。在一些实 施例中,阱区360至少与阱区362或阱区322相邻。在一些实施例中,第 一元件相邻“第二元件”对应于“第

一元件”紧挨第二元件。在一些实施 例中,第一元件与第二元件相邻,对应于第一元件不直接紧邻第二元件。 在一些实施例中,二极管302与esd钳位电路310相邻。在一些实施例中, 信号抽头区域350与阴极302c相邻。

121.在一些实施例中,阱区362位于阱区360和阱区332之间。在一些实 施例中,阱区362至少与阱区360或阱区332相邻。在一些实施例中,二 极管304与esd钳位电路310相邻。在一些实施例中,信号抽头区域352 与阴极304c相邻。

122.esd钳位电路310的其他类型的电路、配置和布置在本公开的范围内。

123.集成电路300a

‑

300b还包括导电结构340、导电结构342、导电结构 344和导电结构346。导电结构340、导电结构342、导电结构344和导电 结构346形成在导电结构340的背侧203上。在一些实施例中,至少导电 结构340、导电结构342、导电结构344或导电结构346嵌入衬底320中。 在一些实施例中,至少导电结构340、导电结构342、导电结构344或导电 结构346被配置为在集成电路300a

‑

300b的一个或多个电路元件与集成电 路300a

‑

300b的其他一个或多个电路元件或其他封装结构(未示出)之间 提供电连接。

124.在一些实施例中,导电结构340、导电结构342和导电结构344以及 导电结构346中的每一个是对应的通孔。在一些实施例中,导电结构340、 导电结构342和导电结构344、导电结构346或信号抽头550中的一个或 多个用于将信号从衬底320的前侧305电耦接到衬底320的后侧303。前 侧305和背侧303通过至少绝缘层321彼此电隔离。在一些实施例中,至 少导电结构340、342、344或346直接与相应的源极/漏极区域310a、310c 或312c耦接。

125.在一些实施例中,集成电路300a通过至少导电结构340、导电结构342、 导电结构344或导电结构346电连接到衬底320的背侧203上的一个或多 个其他封装结构(未示出)。

126.在一些实施例中,至少导电结构340、导电结构342、导电结构344或 导电结构346对应于铜柱结构,铜柱结构至少包括诸如铜等的导电材料。

127.在一些实施例中,至少导电结构340、导电结构342、导电结构344或 导电结构346对应于焊料凸块结构,焊料凸块结构包括具有低电阻率的导 电材料,诸如焊料或焊料合金。在一些实施例中,焊料合金包括sn、pb、 ag、cu、ni、bi或其组合。至少导电结构340、导电结构342、导电结构 344或导电结构346的其他配置、布置和材料在本公开的预期范围内。

128.导电结构340耦接到二极管302的阳极区域302a。导电结构340耦接 到二极管302的阱区322和区域324。在一些实施例中,导电结构340对 应于图1

‑

图2的节点nd3。在一些实施例中,导电结构340电耦接到图1

‑ꢀ

图2的节点nd3。在一些实施例中,导电结构340电耦接到图1

‑

图2的io 焊盘108。

129.导电结构342被耦接到二极管304的阳极区域304a。导电结构342被 耦接到二极管304的阱区域332和区域334。在一些实施例中,导电结构 342对应于图1

‑

图2的节点nd3。在一些实施例中,导电结构342电耦接 到图1

‑

图2的节点nd3。在一些实施例中,导电结构342电耦接到图1

‑

图 2的io焊盘108。

130.在一些实施例中,导电结构340和导电结构342彼此耦接。为了便于 说明,导电结构340和导电结构342未示出为彼此耦接。

131.导电结构344被耦接到信号抽头区域350。导电结构344被配置为向 信号抽头区域350提供电压vdd。在一些实施例中,导电结构344被电耦 接到电压源节点104(例如,电压vdd)。在一些实施例中,导电结构344 对应于图1

‑

图2的节点nd1。在一些实施例中,导电结

构344对应于焊盘 或引脚。在一些实施例中,导电结构344电耦接到图1

‑

图2的节点nd1。 在一些实施例中,导电结构344对应于图1

‑

图2的节点nd1。

132.导电结构346被耦接到信号抽头区域352。导电结构346被配置为向 信号抽头区域352提供电压vss。在一些实施例中,导电结构346被电耦 接到参考电压源节点106(例如,电压vss)。在一些实施例中,导电结 构346对应于图1

‑

图2的节点nd2。在一些实施例中,导电结构346对应 于焊盘或引脚。在一些实施例中,导电结构346电耦接到图1

‑

图2的节点 nd2。在一些实施例中,导电结构346对应于图1

‑

图2的节点nd2。

133.在一些实施例中,至少导电结构340、342、344、346、390或392包 括一层或多层导电材料。在一些实施例中,导电材料包括钨、钴、钌、铜 等或其组合。

134.340、342、344、346、390或392的其他配置、布置和材料在本公开 的预期范围内。

135.集成电路300a中的其他电路配置或数量在本公开的范围内。

136.在esd应力或事件的pd模式期间,二极管302被正向偏置,并且电 流i2从阳极302a流到阴极302c和阴极302d流过二极管302。二极管302 被配置为将电流i2或esd电压从io焊盘108(节点nd3)传输到节点nd1。 电流i2直接从阴极302c和阴极302d流到esd钳位电路302的信号抽头区 域350。响应于节点nd1处的电流i2和esd电压,esd钳位电路310中 的nmos晶体管n1和n2被配置为导通,并且通过信号抽头区域352和 节点nd2将esd电流i2从信号抽头区域350或节点nd1通过沟道区域310d 和312d放电到参考电压源节点106(例如,vss)。

137.在一些实施例中,通过与esd钳位电路310共享信号抽头区域350, 集成电路300a具有比其他方式更少的信号抽头,导致电流i2流过比其他 方式更少的信号抽头,并且直接从阴极302c和阴极302d流动到到esd钳 位电路320的信号抽头区域350,从而与其他方法相比减小了集成电路300a 的信号抽头电阻。

138.图3b是根据一些实施例的集成电路300b的截面图。

139.集成电路300b是至少esd钳位电路120或130的实施例,因此省略 类似的详细描述。集成电路300b是集成电路400b的实施例,因此省略类 似的详细描述。

140.集成电路300b是图1的至少集成电路100或图2的集成电路200的实 施例,因此省略类似的详细描述。

141.集成电路300b是图3的集成电路300a的变体。在图3a中,省略了 类似的详细描述。与集成电路300a相比,电流i1代替了电流i2,因此省 略了类似的详细描述。换句话说,集成电路300b被配置为示出在esd应 力的ps模式期间的esd电流流动。

142.在esd应力或事件的ps模式期间,二极管304被反向偏置,并且电 流i1流过二极管304从阳极304a流向阴极304c和阴极304d。二极管304 被配置为将电流i1或esd电压从io焊盘108(节点nd3)传输到节点nd2。 电流i1直接从阴极304c和阴极304d流向esd钳位电路302的信号抽头区 域352。响应于节点id2处的电流i1和esd电压,esd钳位电路310中的 nmos晶体管n2和n1被配置为导通,并且通过信号抽头区域350和节点 nd1将esd电流i1从信号抽头区域352或节点nd2经过沟道区域312d和 310d放电到电压源节点104(例如,vdd)。

143.在一些实施例中,通过与esd钳位电路310共享信号抽头区域352, 集成电路300b具有比其他方法更少的信号抽头,导致电流i1流过比其他 方法更少的信号抽头,并且直接从阴极304c流动阴极304d和阴极304d连 接到esd钳位电路320的信号抽头区域352,从而与其他方法相比减小了 集成电路300b的信号抽头电阻。

144.集成电路300b中的电路的其他配置或数量在本公开的范围内。

145.图4是根据一些实施例的集成电路400的电路图。

146.集成电路400是图1的至少esd钳位器120的实施例,因此省略类似 的详细描述。在一些实施例中,集成电路400是图3a

‑

图3b的esd钳位 电路310的等效电路。在一些实施例中,图1的nmos晶体管n1为nmos 晶体管n1。图4对应于图1和2的nmos晶体管n1。在图3a

‑

图3b中 示出了nmos晶体管n2。图4对应于图3a

‑

图3b的nmos晶体管n2。

147.集成电路400包括电阻器r1、电容器c1、反相器i1、nmos晶体管 n1和nmos晶体管n2。在一些实施例中,nmos晶体管n1和nmos晶 体管n2被称为esd放电电路,其被配置为在节点nd1或节点nd2的esd 事件期间耦接节点nd1和nd2,从而在节点nd1和nd2之间提供esd放 电路径。

148.电阻器r1的第一端、节点nd1、反相器i1的第一电源电压节点(未 标记)和nmos晶体管n1的漏极中的每一个耦接在一起。电阻器r1的第 二端、电容器c1的第一端、反相器i1的输入端子和节点nd4中的每一个 耦接在一起。

149.电容器c1的第二端、节点nd2、nmos晶体管n2的源极、nmos晶 体管n1的体(body)、nmos晶体管n2的体和反相器i1的第二电源电 压节点(未标记)分别耦接一起。

150.反相器i1的输出端子耦接到nmos晶体管n1的栅极和nmos晶体 管n2的栅极。

151.在一些实施例中,电容器c1是晶体管耦接电容器。例如,在一些实施 例中,电容器c1是其漏极和源极耦接在一起的晶体管,从而形成晶体管耦 接的电容器。

152.电阻器r1和电容器c1被配置为rc网络。根据rc网络输出的位置, rc网络被配置为低通滤波器或高通滤波器。

153.在一些实施例中,反相器i1包括耦接在一起作为反相器电路的nmos 晶体管(未示出)和pmos晶体管(未示出)。因此,节点nd4处的缓慢 上升的电压将被反相器i1反相,从而使节点nd3迅速上升。此外,节点 nd4处的快速上升的电压将被反相器i1反相,从而使节点nd3缓慢地上升。 在一些实施例中,反相器i1被配置为响应于输入信号(未示出)而产生反 相的输入信号(未示出)。

154.当节点nd1上发生esd事件时(例如,esd反向的esd电流i2a), 节点nd1上的esd电流或电压迅速上升,导致节点nd4的电压(例如, 电容器c1两端)由于节点nd4上的电压对应于低通滤波器的输出电压(例 如,电容器c1上相对于节点nd2的电压)而缓慢上升(例如,比迅速慢)。 换句话说,电容器c1被配置为低通滤波器,并且来自esd事件的快速变 化的电压或电流被电容器c1滤波。响应于节点nd4处缓慢上升的电压, 反相器i1中的pmos晶体管(未显示)将导通,从而将节点nd3耦接到 节点nd1并使节点nd3从节点nd1处的esd事件迅速上升。因此,通过 节点nd1处的esd事件,节点nd3以及nmos晶体管n1和n2的栅极被 充电。响应于节点nd3处的esd事件充电,nmos晶体管n1和n2导通 并将节点nd1耦接到节点nd2。通过导通并且将节点nd1耦接到节点nd2, nmos晶体管n1和n2的沟道在从节点nd1到nd2的反esd方向上放电 esd电流i2a。

155.当在节点nd2发生esd事件时(例如,esd电流i1a在正向esd方 向上流动),节点nd2上的esd电流或电压迅速上升,导致节点nd4的 电压(例如,电容器c1两端)上升。但是,节点nd4处的上升电压将由 反相器i1反相,从而使节点nd3不会因节点nd2处的esd事件而上升, 从而导致nmos晶体管n1和n2无法导通,并且nmos晶体管n1和n2 对节点nd2上的esd事件的

影响最小。

156.集成电路400中的电路的其他配置或数量在本公开的范围内。

157.图5是根据一些实施例的操作esd电路的方法500的流程图。在一些 实施例中,方法500的电路至少包括集成电路100、200或300a

‑

300b(图 1、图2或图3a

‑

图3b)。应当理解,可以在图5所示的方法500之前、之 中和/或之后执行附加的操作。在图5中仅示出了一些其他过程,并且这里 仅简要描述一些其他过程。应当理解,方法500利用集成电路100、200或 300a

‑

300b中的一个或多个的特征。

158.方法500至少适用于集成电路300a或300b。首先关于集成电路300a 和电流路径i2描述方法500。然而,方法500也适用于集成电路300b和 电流路径i1,并且在描述集成电路300a之后在下面进行描述。方法500 对集成电路300a或300b的其他操作顺序在本公开的范围内。

159.在方法500的操作502中,在第一节点上接收到esd事件的esd电 压。在一些实施例中,esd电压大于电压源的电源电压vdd。在一些实施 例中,方法500的第一节点包括节点nd3。在一些实施例中,方法500的 第一节点至少包括io焊盘108、导电结构340或导电结构342。

160.在操作504,二极管被导通,从而将esd电流从二极管的阳极传导到 二极管的阴极。在一些实施例中,方法500的二极管至少包括二极管d1 或302。在一些实施例中,方法500的阳极至少包括二极管d1的阳极或阳 极302a。在一些实施例中,方法500的阴极至少包括二极管d1的阴极, 阴极302c或302d。在一些实施例中,方法500的esd电流包括电流i2。

161.在操作506处,esd电流从二极管的阴极传导到钳位电路的第一信号 抽头。在一些实施例中,方法500的第一信号抽头至少包括信号抽头250 或350。在一些实施例中,方法500的钳位电路至少包括esd钳位电路120、 220或310。

162.在操作508处,esd事件的esd电流由esd钳位电路放电。在一些 实施例中,esd事件的esd电流由第一晶体管的沟道或第二晶体管的沟道 放电。在一些实施例中,方法500的第一晶体管包括nmos晶体管n1, 并且沟道包括沟道区域310d。在一些实施例中,方法500的第二晶体管包 括nmos晶体管n2,并且沟道包括沟道区域312d。

163.在一些实施例中,操作508至少包括操作510、512、514或516。

164.在操作510处,响应于在esd钳位电路的第一信号抽头或第二节点处 接收到esd电流,esd钳位电路被接通。在一些实施例中,方法500的第 二节点包括节点nd1。在一些实施例中,方法500的第二节点对应于导电 结构390。

165.在操作512处,响应于esd钳位电路导通,第二节点耦接到第三节点。 在一些实施例中,方法500的第三节点包括节点nd2。在一些实施例中, 方法500的第三节点对应于导电结构392。在一些实施例中,响应于esd 钳位电路的nmos晶体管n1和nmos晶体管n2导通,第二节点耦接到 第三节点。

166.在操作514处,将esd电流从esd钳位电路的第一信号抽头或第二 节点传导到第二信号抽头。在一些实施例中,方法500的第二信号抽头至 少包括信号抽头252或352。

167.在操作516处,将esd电流从钳位电路的第二信号抽头传导到第四节 点。在一些实施例中,方法500的第四节点至少包括参考电压源节点106 (例如,电压vss)或导电结构346。

168.虽然关于集成电路300a和电流路径i2描述了方法500,但是方法500 也适用于集成电路300b和电流路径i1,并且下面以类似的操作进行描述。

169.例如,在操作502处,在第一节点上接收esd事件的esd电压。在 一些实施例中,esd电压大于参考电压源节点106的参考电源电压vss。 在一些实施例中,方法500的第一节点至少包括io焊盘108或导电结构 342。

170.在操作504处,二极管导通,从而将esd电流从二极管的阳极传导到 二极管的阴极。在一些实施例中,方法500的二极管至少包括二极管d2 或304。在一些实施例中,方法500的阳极至少包括二极管d2的阳极或阳 极304a。在一些实施例中,方法500的阴极至少包括二极管d2的阴极, 阴极304c或304d。在一些实施例中,方法500的esd电流包括电流i1。

171.在操作506处,esd电流从二极管的阴极传导到钳位电路的第一信号 抽头。在一些实施例中,方法500的第一信号抽头至少包括信号抽头252 或352。

172.在操作508处,esd事件的esd电流由esd钳位电路放电。在一些 实施例中,esd事件的esd电流由nmos n2的沟道区312d和nmos晶 体管n1的沟道区310d放电。

173.在操作510处,响应于在esd钳位电路或第二节点的第一信号抽头处 接收到esd电流,esd钳位电路被导通。在一些实施例中,方法500的第 二节点包括节点nd2。在一些实施例中,方法500的第二节点对应于导电 结构392。

174.在操作512处,响应于esd钳位电路导通,第二节点耦接到第三节点。 在一些实施例中,方法500的第三节点包括节点ndl。在一些实施例中, 方法500的第三节点对应于导电结构390。在一些实施例中,响应于esd 钳位电路的nmos晶体管n1和nmos晶体管n2导通,第二节点耦接到 第三节点。

175.在操作514处,将esd电流从esd钳位电路的第一信号抽头或第二 节点传导到第二信号抽头。在一些实施例中,方法500的第二信号抽头至 少包括信号抽头250或350。

176.在操作516处,将esd电流从钳位电路的第二信号抽头传导到第四节 点。在一些实施例中,方法500的第四节点至少包括电压源节点104(例 如,电压vdd)或导电结构344。

177.在一些实施例中,不执行方法500的一个或多个操作。在一些实施例 中,重复方法500的一个或多个操作。在一些实施例中,方法500被重复。

178.图6是根据一些实施例的制造集成电路的方法的流程图。在一些实施 例中,方法600可用于制造或制造至少集成电路100、200或300a

‑

300b(图 1、图2或图3a

‑

图3b)。应当理解,可以在图6所示的方法600之前,之 中和/或之后执行附加的操作。在图6中仅示出了一些其他过程,并且这里 仅简要描述一些其他过程。应当理解,方法600利用集成电路100、200或 300a

‑

300b中的一个或多个的特征。

179.方法600至少适用于集成电路300a或300b。关于集成电路300a描 述了方法600。但是,方法600也适用于集成电路300b。方法600对集成 电路300a或300b的其他操作顺序在本公开的范围内。

180.在方法600的操作602中,在晶圆的前侧上制造第一二极管。在一些 实施例中,方法600的晶圆包括衬底320。在一些实施例中,方法600的 晶圆的前侧至少包括衬底320的前侧305。在一些实施例中,方法600的 第一二极管至少包括二极管302。

181.在一些实施例中,操作602至少包括操作602a或602b。在一些实施例 中,操作602a包括在衬底320的前侧305上沉积氧化物层704(图7a

‑

7e), 并且在图6中示出。

182.在一些实施例中,操作602b包括在氧化物层704中形成开口,然后用 导电材料填充氧化物层中的开口,从而形成通孔706(图7b),以及生长 外延层708(图7b)生长在开口的未填充部分中,并且在图6中示出。在 一些实施例中,外延层708(图7b)对应于阴极区域302c和302d。

183.在一些实施例中,操作602还包括在衬底320中制造阱322,在阱322 中制造重掺杂区324,从而形成第一二极管的阳极区302a,在阱322中制 造阴极区302c和302d,以及制造栅极结构302b。

184.在一些实施例中,至少阱322、阱360或362(例如,esd钳位电路 310)包括p型掺杂剂。在一些实施例中,p型掺杂剂包括硼、铝或其他合 适的p型掺杂剂。在一些实施例中,至少阱322、阱360或362包括在衬 底320上方生长的外延层。在一些实施例中,通过在外延工艺期间添加掺 杂剂来掺杂外延层。在一些实施例中,在形成外延层之后,通过离子注入 来掺杂外延层。在一些实施例中,通过掺杂衬底320形成至少阱322,阱 360或362。在一些实施例中,通过离子注入来执行掺杂。在一些实施例中, 至少阱322,阱360或362具有在1

×

10

12

原子/cm3至1

×

10

14

原子/cm3范围内的掺杂剂浓度。在一些实施例中,通过类似于阱322的形成的工艺 来形成区域324。在一些实施例中,区域324是重掺杂的p区域。

185.在一些实施例中,至少制造操作602的阴极区域302c和302d或制造 操作604的阴极区域304c和304d(如下所述)包括在衬底中形成阴极部件。 在一些实施例中,阴极部件的形成包括去除衬底的部分以在阱322或332 的边缘处形成凹部,然后通过将凹部填充在衬底中来执行填充工艺。在一 些实施例中,在去除垫氧化物层或牺牲氧化物层之后,蚀刻(例如,湿蚀 刻或干蚀刻)凹部。在一些实施例中,执行蚀刻工艺以去除与隔离区域(例 如,sti区域328a、328b、328c或328d)相邻的有源区域的顶表面部分。 在一些实施例中,通过外延或外延(epi)工艺执行填充工艺。在一些实施 例中,使用与蚀刻工艺同时进行的生长工艺来填充凹部,其中蚀刻工艺的 生长速率大于蚀刻工艺的蚀刻速率。在一些实施例中,使用生长工艺和蚀 刻工艺的组合来填充凹部。例如,在凹部中生长材料层,然后对生长的材 料进行蚀刻工艺以去除部分材料。然后,对蚀刻的材料执行后续的生长工 艺,直到在凹部中达到所需的材料厚度为止。在一些实施例中,生长过程 持续到材料的顶表面在衬底的顶表面上方为止。在一些实施例中,生长过 程持续到材料的顶表面与衬底的顶表面共面。在一些实施例中,通过各向 同性或各向异性蚀刻工艺去除阱322或332的部分。蚀刻工艺选择性地蚀 刻阱322或332而不蚀刻栅极结构302b或304b。在一些实施例中,使用 反应离子蚀刻(rie),湿蚀刻或其他合适的技术来执行蚀刻工艺。在一些 实施例中,半导体材料沉积在凹部中以形成类似于源极/漏极部件的阴极部 件。在一些实施例中,执行外延工艺以将半导体材料沉积在凹部中。在一 些实施例中,外延工艺包括选择性外延生长(seg)工艺、cvd工艺、分 子束外延(mbe)、其他合适的工艺和/或其组合。外延工艺使用与衬底320 的成分相互作用的气态和/或液态前体。在一些实施例中,阴极部件包括外 延生长的硅(epi si),碳化硅或硅锗。在一些实例中,在外延工艺期间, 与栅极结构302b或304b相关联的ic器件的阴极部件是原位掺杂或不掺杂 的。当在epi工艺期间不掺杂阴极部件时,在一些情况下,在随后的工艺 期间对阴极部件进行掺杂。通过离子注入、等离子体浸没离子注入、气体 和/或固体源扩散、其他合适的过程和/或它们的组合来实现随后的掺杂过程。 在一些实施例中,在形成阴极部件之后和/或在随后的掺杂过程之后,将阴 极部件还暴露于退火过程。

186.在一些实施例中,至少制造操作602、604或606的栅极区域(如下所 述)包括执行一种或多种沉积工艺以形成一个或多个介电材料层。在一些 实施例中,沉积工艺包括化学气相沉积(cvd)、等离子体增强cvd (pecvd)、原子层沉积(ald)或其他适合于沉积一个或多个材料层的 工艺。在一些实施例中,制造栅极区域包括执行一个或多个沉积工艺以形 成一个或多个导电材料层。在一些实施例中,制造栅区包括形成栅电极或 伪栅电极。在一些实施例中,制造栅极区域包括沉积或生长至少一个介电 层,例如栅极介电层。在一些实施例中,使用掺杂或非掺杂的多晶硅(或 多晶硅)形成栅极区域。在一些实施例中,栅极区域包括金属,诸如al、 cu、w、ti、ta、tin、tan、nisi、cosi、其他合适的导电材料或其组合。

187.在方法600的操作604中,在晶圆的前侧上制造了第二二极管。在一 些实施例中,方法600的晶圆的背侧至少包括衬底320的背侧303。在一 些实施例中,方法600的第二二极管至少包括二极管304。

188.在一些实施例中,操作604至少包括操作604a或604b。在一些实施例 中,操作604a包括在衬底320的前侧305上沉积氧化物层704(图7a

‑

图 7e),并且在图7a中示出。

189.在一些实施例中,操作604b包括在氧化物层704中形成开口,然后用 导电材料填充氧化物层中的开口,从而形成通孔706(图7b),以及生长 外延层708(图7b)生长在开口的未填充部分中,并且在图7b中示出。 在一些实施例中,外延层708(图7b)对应于阴极区域304c和304d。

190.在一些实施例中,操作604还包括在衬底320中制造阱332,在阱332 中制造重掺杂区334,从而形成第二二极管的阳极区304a,在阱332上方 制造阴极区304c和304d,以及制造栅极结构304b。

191.在一些实施例中,阱332包括n型掺杂剂。在一些实施例中,n型掺 杂剂包括磷,砷或其他合适的n型掺杂剂。在一些实施例中,n型掺杂剂 浓度在约1

×

10

12

原子/cm2至约1

×

10

14

原子/cm2的范围内。在一些实施 例中,阱332通过离子注入形成。离子注入的功率范围从大约1500k电子 伏特(ev)到大约8000k ev。在一些实施例中,外延生长阱332。在一些 实施例中,阱332包括在表面上方生长的外延层。在一些实施例中,通过 在外延工艺期间添加掺杂剂来掺杂外延层。在一些实施例中,在形成外延 层之后,通过离子注入对外延层进行掺杂,并具有上述掺杂剂浓度。在一 些实施例中,通过类似于阱332的形成的过程来形成区域334。在一些实 施例中,区域334是重掺杂的n区域。

192.在方法600的操作606中,在晶圆的前侧上制造esd钳位电路。在一 些实施例中,方法600的esd钳位电路至少包括esd钳位电路310。

193.在一些实施例中,操作606至少包括操作606a或606b。在一些实施例 中,操作606a包括在衬底320的前侧305上沉积氧化物层704(图7a

‑

7e), 并且在图7a中示出。

194.在一些实施例中,操作606b包括在氧化物层704中形成开口,然后用 导电材料填充氧化物层中的开口,从而形成通孔706(图7b),以及生长 外延层708(图7b)在开口的未填充部分中,并且在图7b中示出。在一 些实施例中,外延层708(图7b)对应于源极310a 312c和漏极310c或312a。

195.在一些实施例中,操作606还包括在衬底320中制造阱360和362, 在阱360中制造源极/漏极区域(例如,源极310a和漏极310c),以及制 造源极/漏极区域(例如,源极312c和320c)阱362中的漏极312a),以 及制造栅极结构310b和312b。

196.在一些实施例中,在操作606的阱360中制造源极/漏极区域(例如, 源极310a和漏极310c)包括操作608,并且制造栅极结构310b和312b包 括操作610。

197.在方法600的操作608中,在晶圆的前侧上制造第一信号抽头区域。 在一些实施例中,方法600的第一信号抽头区域至少包括信号抽头区域350。 在一些实施例中,信号抽头区域350对应于esd钳位电路310的漏极310a。 在一些实施例中,操作608对应于操作606b。

198.在方法600的操作610中,在晶圆的前侧上制造第二信号抽头。在一 些实施例中,方法600的第二信号抽头区域至少包括信号抽头区域352。 在一些实施例中,信号抽头区域352对应于esd钳位电路310的源极312c。 在一些实施例中,操作608对应于操作606b。

199.在一些实施例中,至少信号抽头区域350或352包括p型掺杂剂。在 一些实施例中,p型掺杂剂包括硼、铝或其他合适的p型掺杂剂。在一些 实施例中,至少信号抽头区域350或352是通过类似于形成相应的阱360 或362的过程来形成的。在一些实施例中,至少信号抽头区域350或352 是重掺杂的p区域。

200.在一些实施例中,至少信号抽头区域350或352包括n型掺杂剂。在 一些实施例中,n型掺杂剂包括磷、砷或其他合适的n型掺杂剂。在一些 实施例中,n型掺杂剂浓度在约1

×

10

12

原子/cm2至约1

×

10

14

原子/cm2的范围内。在一些实施例中,至少信号抽头区域350或352通过离子注入 形成。离子注入的功率范围从大约1500k电子伏特(ev)到大约8000k ev。 在一些实施例中,至少信号抽头区域350或352是重掺杂的n区域。

201.在一些实施例中,至少信号抽头区域350或352被外延生长。在一些 实施例中,至少信号抽头区域350或352包括在衬底320上方生长的外延 层。在一些实施例中,通过在外延工艺期间添加掺杂剂来掺杂外延层。在 一些实施例中,在形成外延层之后,通过离子注入来掺杂外延层。在一些 实施例中,至少信号抽头区域350或352通过掺杂衬底320形成。在一些 实施例中,通过离子注入来执行掺杂。在一些实施例中,至少信号抽头区 域350或352具有在1

×

10

12

原子/cm3至1

×

10

14

原子/cm3范围内的掺杂 剂浓度。

202.在方法600的操作612中,在晶圆320的前侧305上制造了第一组导 电结构710(图7c)。图7c是根据一个或多个实施例的至少在步骤612 之后制造在晶圆320的前侧305上的第一组导电结构710的截面图。

203.在一些实施例中,操作612包括在晶圆320的前侧305上沉积第一组 导电结构710。在一些实施例中,方法600的第一组导电结构710至少包 括导电结构390和导电结构392。

204.在一些实施例中,操作612包括在晶圆320的前侧305上沉积绝缘层 712(图7c),从晶圆320的前侧305去除绝缘层712的部分,以及在晶 圆320的前侧305上的绝缘层712的去除的部分中沉积第一组导电结构710。 在一些实施例中,方法600的第一组导电结构是使用光刻和材料的组合形 成的去除工艺以在衬底上方的绝缘层(未示出)中形成开口。在一些实施 例中,光刻工艺包括图案化光致抗蚀剂,例如正性光致抗蚀剂或负性光致 抗蚀剂。在一些实施例中,光刻工艺包括形成硬掩模、抗反射结构或另一 种合适的光刻结构。在一些实施例中,材料去除工艺包括湿蚀刻工艺、干 蚀刻工艺、rie工艺、激光钻孔或其他合适的蚀刻工艺。然后用导电材料 例如铜、铝、钛、镍、钨或其他合适的导电材料填充开口。在一些实施例 中,使用cvd、pvd、溅射、ald或其他合适的形成工艺来填充开口。

205.在方法600的操作614中,在晶圆的背侧303上进行晶圆减薄。图7d 是根据一个或多个实施例的在晶圆减薄操作614之前的晶圆320的截面图。

206.在一些实施例中,操作614包括将晶圆320翻转过来,并在半导体晶 圆或衬底的背侧303上执行减薄工艺。在一些实施例中,减薄工艺包括研 磨操作和抛光操作(例如化学机械抛光(cmp))或其他合适的工艺。在 一些实施例中,在减薄工艺之后,执行湿法蚀刻操作以去除形成在半导体 晶圆320或衬底的背侧303上的缺陷。

207.在方法600的操作616中,将绝缘层722(图7e)沉积在晶圆的背侧 上。在一些实施例中,方法600的绝缘层722包括绝缘层321。在一些实 施例中,绝缘层321包括介电材料,介电材料包括氧化物或另一种合适的 绝缘材料。在一些实施例中,绝缘层321通过cvd、旋涂聚合物介电、原 子层沉积(ald)或其他工艺形成。

208.在方法600的操作618中,从晶圆的背侧去除绝缘层722的部分。在 一些实施例中,方法600的操作618使用光刻和材料去除工艺的组合以在 晶圆320上方的绝缘层722中形成开口。在一些实施例中,光刻工艺包括 图案化光刻胶,例如正光刻胶或负光刻胶。在一些实施例中,光刻工艺包 括形成硬掩模、抗反射结构或另一种合适的光刻结构。在一些实施例中, 材料去除工艺包括湿蚀刻工艺、干蚀刻工艺、rie工艺、激光钻孔或其他 合适的蚀刻工艺。

209.在方法600的操作620中,第二组导电结构720(图7e)沉积在绝缘 层的至少被去除的部分中。图7e是根据一个或多个实施例的至少在操作 620之后的晶圆320的截面图。

210.在一些实施例中,操作620包括在晶圆的背侧上沉积第二组导电结构 720。在一些实施例中,方法600的第二组导电结构720至少包括导电结构 340,导电结构342,导电结构344或导电结构346。

211.在一些实施例中,操作620包括用导电材料例如铜、铝、钛、镍、钨 或其他合适的导电材料填充绝缘层722中的开口。在一些实施例中,使用 cvd、pvd、溅射、ald或其他合适的形成工艺来填充开口。

212.在一些实施例中,不执行方法600的一个或多个操作。在一些实施例 中,重复方法600的一个或多个操作。在一些实施例中,方法600被重复。

213.图7a

‑

图7e是根据一个或多个实施例的集成电路的截面图。

214.图7a是根据一个或多个实施例的集成电路700a的截面图。在一些实 施例中,至少在操作602a、604a或606a之后,集成电路700a对应于诸如 集成电路300a或300b的集成电路。在一些实施例中,集成电路700a包 括衬底320上的氧化物层704。

215.图7b是根据一个或多个实施例的集成电路700b的截面图。在一些实 施例中,集成电路700b至少在操作602b、604b或606b之后对应于集成电 路,诸如集成电路300a或300b。在一些实施例中,集成电路700b包括 形成在至少氧化物层704或衬底320的开口中的通孔706。在一些实施例 中,集成电路700b还包括在通孔706、氧化物层704和衬底上的外延层708。 320.在一些实施例中,外延层708生长在氧化物层704的开口的未填充部 分中。

216.图7c是根据一个或多个实施例的集成电路700c的截面图。在一些实 施例中,集成电路700c对应于至少执行操作612之后的集成电路,例如集 成电路300a或300b。在一些实施例中,集成电路700c包括第一组导电 结构710、绝缘层712和集成电路700b。在一些实施例中,集成电路700c 包括制造在晶圆320的前侧305上的绝缘层712的去除的部分中的第一组 导电结构710。

217.图7d是根据一个或多个实施例的集成电路700d的截面图。在一些实 施例中,集成

电路700d对应于在操作减薄晶圆614之前的集成电路,诸如 集成电路300a或300b。在一些实施例中,集成电路700d包括翻转的集 成电路700c。

218.图7e是根据一个或多个实施例的集成电路700e的截面图。在一些实 施例中,集成电路700e至少在操作620之后对应于诸如集成电路300a或 300b的集成电路。在一些实施例中,集成电路700e包括第二组导电结构 720、绝缘层722和集成电路700d(没有晶圆320的去除部分)。在一些 实施例中,集成电路700e包括制造在晶圆320的绝缘层722的去除部分中 的第二组导电结构720。

219.在相应附图的至少集成电路100、200和300a

‑

300b(图1、图2和图 3a

‑

图3b)中,其他二极管类型或二极管数量、或晶体管类型或晶体管数 量在本公开的范围内。

220.此外,图3a

‑

图3b所示的各种nmos或pmos晶体管具有特定的掺 杂剂类型(例如,n型或p型),并且仅用于说明目的。本公开的实施例 不限于特定的晶体管类型,并且图3a

‑

图3b所示的pmos或nmos晶体 管中的一个或多个可以被不同晶体管/掺杂剂类型的对应晶体管代替。类似 地,以上描述中使用的各种信号的低或高逻辑值也用于说明。当信号被激 活和/或去激活时,本公开的实施例不限于特定的逻辑值。选择不同的逻辑 值在各种实施例的范围内。在3a

‑

图3b中选择不同数量的pmos晶体管在 各种实施例的范围内。

221.本说明书的一个方面涉及一种esd保护电路。esd保护电路包括第 一二极管、第二二极管和esd钳位电路。第一二极管在半导体晶圆中,并 且耦接到io焊盘。第二二极管在半导体晶圆中,并且耦接到第一二极管和 io焊盘。esd钳位电路在半导体晶圆中,并且耦接到第一二极管和第二二 极管。esd钳位电路在半导体晶圆中包括第一信号抽头区域。第一信号抽 头区域耦接到第一电压源。第一二极管耦接到esd钳位电路并被配置为与esd钳位电路共享第一信号抽头区域。

222.在上述esd保护电路中,esd钳位电路还包括半导体晶圆中的第二信 号抽头区域,第二信号抽头区域耦接到与第一电压源不同的第二电压源, 第二二极管耦接到esd钳位电路并且被配置为与esd钳位电路共享第二 信号抽头区域。

223.在上述esd保护电路中,还包括:第一导电结构,耦接在第一电压源 和第一信号抽头区域之间;以及第二导电结构,耦接在第二电压源和第二 信号抽头区域之间,第一导电结构和第二导电结构位于半导体晶圆的背侧 上。

224.在上述esd保护电路中,第一导电结构被配置为向第一信号抽头区域 提供第一电压源的第一电压;以及第二导电结构被配置为向第二信号抽头 区域提供第二电压源的第二电压。

225.在上述esd保护电路中,还包括:io电路,位于半导体晶圆中,耦接 到第一二极管、第二二极管和io焊盘。

226.在上述esd保护电路中,io焊盘包括:第一导电结构,耦接到第一二 极管的第一阳极;以及第二导电结构,耦接到第二二极管的第二阳极,第 一导电结构和第二导电结构位于半导体晶圆的背侧上。

227.在上述esd保护电路中,至少第一二极管或第二二极管不具有信号抽 头区域。

228.在上述esd保护电路中,第一二极管是第一纳米片垂直阱二极管;第 二二极管是第二纳米片垂直阱二极管;以及esd钳位电路是至少一个纳米 片晶体管器件。

229.本说明书的另一方面涉及一种esd保护电路。esd保护电路包括第一 二极管、第二

二极管、内部电路和esd钳位电路。第一二极管在半导体晶 圆中,并且耦接到第一焊盘。第二二极管在半导体晶圆中,并且耦接到第 一二极管和第一焊盘。内部电路耦接到第一二极管和第二二极管。esd钳 位电路在半导体晶圆中,通过第一节点耦接到第一二极管,并且通过第二 节点耦接到第二二极管。esd钳位电路包括耦接到电压源的第一信号抽头 区域和耦接到参考电压源的第二信号抽头区域。第一二极管耦接到esd钳 位电路并被配置为与esd钳位电路共享第一信号抽头区域。第二二极管耦 接到esd钳位电路并被配置为与esd钳位电路共享第二信号抽头区域。

230.在上述esd保护电路中,第一二极管包括:第一阳极,位于半导体晶 圆中;以及第一阴极,位于半导体晶圆中,在第一阳极上方并且通过第一 节点耦接到第一信号抽头区域。

231.在上述esd保护电路中,第一二极管还包括:第二阴极,位于半导体 晶圆中,在第一阳极上方并且通过第一节点耦接到第一信号抽头区域和第 一阴极。

232.在上述esd保护电路中,第二二极管包括:第二阳极,位于半导体晶 圆中;以及第三阴极,位于半导体晶圆中,在第二阳极上方并且通过第二 节点耦接到第二信号抽头区域。

233.在上述esd保护电路中,第二二极管还包括:第四阴极,位于半导体 晶圆中,在第二阳极上方并且通过第二节点耦接到第二信号抽头区域和第 三阴极。

234.在上述esd保护电路中,还包括:第一导电结构,耦接在电压源和第 一信号抽头区域之间;以及第二导电结构,耦接在参考电压源和第二信号 抽头区域之间,第一导电结构和第二导电结构位于半导体晶圆的背侧上。

235.在上述esd保护电路中,第一焊盘包括:第三导电结构,耦接到第一 二极管的第一阳极;第四导电结构,耦接到第二二极管的第二阳极,第三 导电结构和第四导电结构位于半导体晶圆的背侧上。

236.在上述esd保护电路中,esd钳位电路在第一二极管和第二二极管之 间。

237.然而,本说明书的另一方面涉及一种操作esd保护电路的方法。该方 法包括在第一节点上接收第一esd电压,该第一esd电压大于电压源的 电源电压,该第一esd电压对应于第一esd事件。该方法还包括导通第 一二极管,从而将第一esd电流从第一二极管的第一阳极传导到第一二极 管的第一阴极。该方法还包括将第一esd电流从第一二极管的第一阴极传 导到esd钳位电路的第一信号抽头。该方法还包括通过esd钳位电路放 电第一esd事件的第一esd电流。

238.在上述方法中,通过esd钳位电路放电第一esd事件的第一esd电 流包括:响应于在esd钳位电路的第一信号抽头处或第二节点处接收到第 一esd电流,导通esd钳位电路;响应于esd钳位电路导通,将第二节 点耦接到第三节点;将第一esd电流从esd钳位电路的第一信号抽头传 导到第二信号抽头;以及将第一esd电流从esd钳位电路的第二信号抽 头传导到第四节点。

239.在上述方法中,还包括:在第一节点上接收第二esd电压,第二esd 电压大于参考电压源的参考电源电压,第二esd电压对应于第二esd事 件;导通第二二极管,从而将第二esd电流从第二二极管的第二阳极传导 到第二二极管的第二阴极;将第二esd电流从第二二极管的第二阴极传导 到esd钳位电路的第二信号抽头;以及通过esd钳位电路放电第二

esd 事件的第二esd电流。

240.在上述方法中,通过esd钳位电路放电第二esd事件的第二esd电 流包括:响应于在esd钳位电路的第二信号抽头处或第三节点处接收到第 二esd电流,导通esd钳位电路;响应于esd钳位电路导通,将第三节 点耦接到第二节点;将第二esd电流从esd钳位电路的第二信号抽头传 导到第一信号抽头;以及将第二esd电流从esd钳位电路的第一信号抽 头传导到第五节点。

241.已经描述了多个实施例。然而,将理解的是,可以在不脱离本公开的 精神和范围的情况下进行各种修改。例如,示出为特定掺杂剂类型的各种 晶体管(例如,n型或p型金属氧化物半导体(nmos或pmos))是出 于说明的目的。本公开的实施例不限于特定类型。为特定晶体管选择不同 的掺杂剂类型在各种实施例的范围内。在以上描述中使用的各种信号的低 或高逻辑值也用于说明。当信号被激活和/或去激活时,各种实施例不限于 特定的逻辑值。选择不同的逻辑值在各种实施例的范围内。在各种实施例 中,晶体管用作开关。代替晶体管使用的开关电路在各种实施例的范围内。 在各种实施例中,晶体管的源极可以被配置为漏极,并且漏极可以被配置 为源极。这样,术语源极和漏极可互换使用。各种信号由相应的电路生成, 但是为简单起见,未示出电路。

242.各种图示出了使用分立电容器进行说明的电容性电路。可以使用等效 电路。例如,可以使用电容性器件,电路或网络(例如,电容器,电容性 元件,器件,电路等的组合)代替分立电容器。上面的图示包括示例性步 骤,但是步骤不一定按所示顺序执行。根据所公开的实施例的精神和范围, 可以适当地添加,替换,改变顺序和/或消除步骤。

243.上述概述了几个实施例的特征,以便本领域技术人员可以更好地理解 本公开的各个方面。本领域技术人员应当理解,他们可以容易地使用本公 开作为设计或修改用于实现本文所介绍的实施例的相同目的和/或实现其 相同优点的其它过程和结构的基础。本领域技术人员还应当认识到,此类 等效结构不背离本发明的精神和范围,并且它们可以在不背离本发明的精 神和范围的情况下在本发明中进行各种改变、替换以及改变。

- 该技术已申请专利。仅供学习研究,如用于商业用途,请联系技术所有人。

- 技术研发人员:叶昱宏;林文杰;李介文

- 技术所有人:台湾积体电路制造股份有限公司

- 我是此专利的发明人

- 该领域下的技术专家

- 如您需求助技术专家,请点此查看客服电话进行咨询。

- 1、贺老师:氮化物陶瓷、光功能晶体材料及燃烧合成制备科学及工程应用

- 2、杨老师:工程电磁场与磁技术,无线电能传输技术

- 3、许老师:1.气动光学成像用于精确制导 2.人工智能方法用于数据处理、预测 3.故障诊断和健康管理

- 4、王老师:智能控制理论及应用;机器人控制技术

- 5、李老师:1.自旋电子学 2.铁磁共振、电磁场理论

- 如您是高校老师,可以点此联系我们加入专家库。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1

精彩留言,会给你点赞!

专利分类正在加载中....