有机中介层及其制造方法与流程

1.本发明实施例是关于一种半导体制造技术,特别是有关于一种用于半导体封装的有机中介层及其制造方法。

背景技术:

2.扇出晶圆级封装(fan-out wafer-level package,fowlp)可在半导体晶粒和封装基板之间使用中介层(interposer)。可接受的中介层具有足够的机械强度,以承受用于连接半导体晶粒和封装基板的接合(bonding)制程。

技术实现要素:

3.本公开一些实施例提供一种有机中介层(organic interposer)。所述有机中介层包括多个介电材料层、多个封装侧凸块结构、多个晶粒侧凸块结构以及多个应力减轻(stress-relief)线路结构。所述介电材料层内埋多个重分布互连结构(redistribution interconnect structures)。所述封装侧凸块结构位于所述介电材料层的第一侧,并连接到所述重分布互连结构中的封装侧子集(package-side subset)。所述晶粒侧凸块结构位于所述介电材料层的第二侧,并连接到所述重分布互连结构中的晶粒侧子集(die-side subset)。其中,所述晶粒侧凸块结构包括位于一第一区域中的多个第一晶粒侧凸块结构和位于一第二区域中的多个第二晶粒侧凸块结构。在平面图中,第二区域与第一区域横向地间隔开一间隙区域,在间隙区域中没有任何晶粒侧凸块结构。所述应力减轻线路结构位于在平面图中在间隙区域的范围内的所述介电材料层之上或之内。其中,所述应力减轻线路结构与所述封装侧凸块结构、所述重分布互连结构和所述晶粒侧凸块结构中的一者包括相同的材料且位于相同的水平高度。

4.本公开另一些实施例提供一种有机中介层。所述有机中介层包括多个介电材料层、多个封装侧凸块结构、多个晶粒侧凸块结构以及多个应力减轻线路结构。所述介电材料层内埋多个重分布互连结构。所述封装侧凸块结构位于所述介电材料层的第一侧,并连接到所述重分布互连结构中的封装侧子集。所述晶粒侧凸块结构位于所述介电材料层的第二侧,并连接到所述重分布互连结构中的晶粒侧子集。其中,所述晶粒侧凸块结构包括位于一第一区域中的多个第一晶粒侧凸块结构和位于一第二区域中的多个第二晶粒侧凸块结构。在平面图中,第二区域与第一区域横向地间隔开一间隙区域,在间隙区域中没有任何晶粒侧凸块结构。所述应力减轻线路结构位于在平面图中在间隙区域的范围内的所述介电材料层之上或之内。其中,所述应力减轻线路结构与从所述封装侧凸块结构、所述重分布互连结构和所述晶粒侧凸块结构中选择的一金属部件位于相同的水平高度。其中,所述应力减轻线路结构包括与金属部件不同的材料。

5.本公开又另一些实施例提供一种形成有机中介层的方法。所述方法包括在载体基板上方形成内埋在封装侧介电材料层内的多个封装侧凸块结构。所述方法也包括在所述封装侧凸块结构上方形成多个互连级(interconnect-level)介电材料层和多个重分布互连

结构。所述方法还包括在所述互连级介电材料层上方形成晶粒侧介电材料层。所述方法还包括在晶粒侧介电材料层上方形成多个晶粒侧凸块结构。其中,所述晶粒侧凸块结构包括位于一第一区域中的多个第一晶粒侧凸块结构和位于一第二区域中的多个第二晶粒侧凸块结构。在平面图中,第二区域与第一区域横向地间隔开一间隙区域,在间隙区域中没有任何晶粒侧凸块结构。此外,所述方法包括在平面图中在间隙区域的范围内的封装侧介电材料层、所述互连级介电材料层或晶粒侧介电材料层中的一者之内或之上形成多个应力减轻线路结构。其中,所述应力减轻线路结构中的每一者包括沿各自的水平方向横向地延伸的多个直线段部,并且所述应力减轻线路结构具有选自以下的至少一特征:所述应力减轻线路结构不电性连接到所述重分布互连结构;以及所述应力减轻线路结构与所述封装侧凸块结构或所述晶粒侧凸块结构位于相同的水平高度。

附图说明

6.图1a是根据本公开一些实施例的包括形成在载体基板上方的有机中介层的示例性结构的垂直截面图。

7.图1b是位于图1a的区域b内的应力减轻线路结构的第一构造的放大图。

8.图1c是位于图1a的区域b内的应力减轻线路结构的第二构造的放大图。

9.图1d是位于图1a的区域b内的应力减轻线路结构的第三构造的放大图。

10.图1e是位于图1a的区域b内的应力减轻线路结构的第四构造的放大图。

11.图1f是位于图1a的区域b内的应力减轻线路结构的第五构造的放大图。

12.图1g是位于图1a的区域b内的应力减轻线路结构的第六构造的放大图。

13.图1h是位于图1a的区域b内的应力减轻线路结构的第七构造的放大图。

14.图1i是图1a的示例性结构的平面图。

15.图2是根据本公开一些实施例的在将半导体晶粒附接到有机中介层之后的示例性结构的垂直截面图。

16.图3是根据本公开一些实施例的在形成扇出晶圆级封装之后的示例性结构的垂直截面图。

17.图4是根据本公开一些实施例的在切割扇出晶圆级封装之后的示例性结构的垂直截面图。

18.图5是根据本公开一些实施例的在将封装基板附接到扇出晶圆级封装之后的示例性结构的垂直截面图。

19.图6是根据本公开一些实施例的在将封装基板附接到印刷电路板(printed circuit board,pcb)之后的示例性结构的垂直截面图。

20.图7a是示出根据本公开一些实施例的用于形成有机中介层的第一种处理步骤顺序的第一流程图。

21.图7b是示出根据本公开一些实施例的用于形成有机中介层的第二种处理步骤顺序的第二流程图。

22.图7c是示出根据本公开一些实施例的用于形成有机中介层的第三种处理步骤顺序的第三流程图。

23.其中,附图标记说明如下:

24.12:(封装侧)介电材料层

25.18:封装侧凸块结构

26.20:(互连级)介电材料层

27.22:(第一)介电材料层

28.24:(第二)介电材料层

29.26:(第三)介电材料层

30.28:(第四)介电材料层

31.40:重分布互连结构

32.42:第一重分布互连结构

33.44:第二重分布互连结构

34.46:第三重分布互连结构/金属基板

35.48:金属焊垫结构

36.60:(晶粒侧)介电材料层

37.80:晶粒侧凸块结构

38.80a:第一晶粒侧凸块结构

39.80b:第二晶粒侧凸块结构

40.100:印刷电路板

41.110:pcb基板

42.118:(封装侧)应力减轻线路结构

43.140:(互连级)应力减轻线路结构

44.180:(晶粒侧)应力减轻线路结构

45.188:pcb接合焊垫

46.190:焊料接点

47.192:底部填充材料部分

48.200:封装基板

49.210:核心基板

50.212:介电衬层

51.214:贯穿核心导孔结构

52.240:板侧表面增层电路

53.242:板侧绝缘层

54.244:内埋板侧布线互连

55.248:板侧接合焊垫

56.260:晶片侧表面增层电路

57.262:晶片侧绝缘层

58.264:内埋晶片侧布线互连

59.268:晶片侧接合焊垫

60.292,780:底部填充材料部分

61.294:稳定结构

62.300:载体基板

63.301:粘合剂层

64.400:有机中介层

65.450,788:焊料部分

66.701:(第一)半导体晶粒

67.702:(第二)半导体晶粒

68.708:晶粒凸块结构

69.790:emc晶粒框架

70.710,712,720,722,730,740,742:步骤

71.b:区域

72.da1:第一区域

73.da2:第二区域

74.gr:间隙区域

75.uia:单元中介层区域

76.α:第一角度

77.β:第二角度

78.ls1:第一直线段部

79.ls2:第二直线段部

80.hd1:第一水平方向

81.hd2:第二水平方向

具体实施方式

82.以下的公开内容提供许多不同的实施例或范例以实施本案的不同特征。以下描述具体的构件及其排列方式的实施例以阐述本公开。当然,这些实施例仅作为范例,而不该以此限定本公开的范围。例如,在说明书中叙述了一第一特征形成于一第二特征之上或上方,其可能包含第一特征与第二特征是直接接触的实施例,亦可能包含了有附加特征形成于第一特征与第二特征之间,而使得第一特征与第二特征可能未直接接触的实施例。另外,在本公开不同范例中可能使用重复的参考符号及/或标记,此重复是为了简化与清晰的目的,并非用以限定所讨论的各个实施例及/或结构之间有特定的关系。

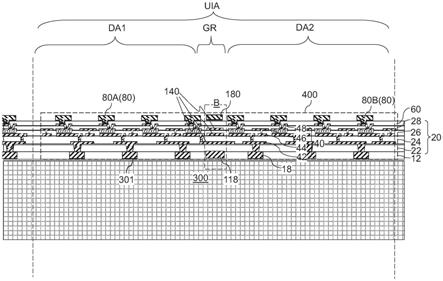

83.再者,空间相关用语,例如「在

…

下方」、「下方」、「较低的」、「上方」、「较高的」及类似的用语,是为了便于描述图示中一个元件或特征与另一个(些)元件或特征之间的关系。除了在图式中绘示的方位外,这些空间相关用语意欲包含使用中或操作中的装置之不同方位。设备可能被转向不同方位(旋转90度或其他方位),则在此使用的空间相关词也可依此相同解释。除非另有明确说明,否则假定具有相同参考符号的每个元件具有相同的材料组成及具有相同厚度范围内的厚度。

84.本公开实施例涉及半导体装置,特别是涉及包含有机中介层(organic interposer)的晶片封装结构及其形成方法,所述有机中介层包括耐应力的接合结构(stress-resistant bonding structure),其各个方面将在后面做详细描述。

85.总的来说,本公开实施例的方法和结构可用于提供一种有机中介层,其可以抵抗(resistant to)在将至少一半导体晶粒附接到其上的期间可能发生的应力引起的结构破

坏。具体地,在有机中介层与半导体晶粒之间施加底部填充材料部分(underfill material portion)通常会在有机中介层上引起机械应力。这样的施加和引起的应力可能导致有机中介层中的重分布互连结构的变形或破裂。根据本公开一些实施例,应力减轻线路结构(stress-relief line structures)可以形成在有机中介层的用于附接半导体晶粒的相邻区域之间的间隙区域中。应力减轻线路结构可以包括与重分布互连结构或凸块(bump)结构相同的材料,或者可以包括与重分布互连结构或凸块结构不同的材料。应力减轻线路结构的机械强度可小于重分布互连结构的机械强度,使得应力减轻线路结构的变形在重分布互连结构变形之前发生。换句话说,应力减轻线路结构在机械应力作用下可变形,从而保护重分布互连结构不变形,并防止重分布互连结构的有害变形。

86.在应力减轻线路结构包括与重分布互连结构相同的材料的实施例中,可以选择应力减轻线路结构的尺寸(例如,宽度)(举例来说,通过使用比重分布互连结构的平均宽度小的宽度),使得应力减轻线路结构在重分布互连结构变形之前先变形。在应力减轻线路结构包括与重分布互连结构不同的材料的实施例中,应力减轻线路结构的材料可以具有较小的杨氏模数(young’smodules),因此可变形并吸收外部的应力,同时避免重分布互连结构的变形。

87.应力减轻线路结构可以是导电的,并可电性连接到位于与晶粒侧(die-side)凸块结构的区域重叠的区域内的重分布互连结构。或者,应力减轻线路结构可以与位于与晶粒侧凸块结构的区域重叠的区域内的重分布互连结构和凸块结构电性隔离。应力减轻线路结构可以设置成许多不同的图案。应力减轻线路结构可以具有包括多个直线段部的曲折线路的构造、可以包括通过曲线段部连接的多个直线段部、或者可以具有形成网格结构的网(mesh)的构造。以下参考附图描述本公开实施例的方法和结构的各个方面。

88.图1a是根据本公开一些实施例的包括形成在载体基板上方的有机中介层的示例性结构的垂直截面图。图1b是位于图1a的区域b内的应力减轻线路结构的第一构造的放大图。图1c是位于图1a的区域b内的应力减轻线路结构的第二构造的放大图。图1d是位于图1a的区域b内的应力减轻线路结构的第三构造的放大图。图1e是位于图1a的区域b内的应力减轻线路结构的第四构造的放大图。图1f是位于图1a的区域b内的应力减轻线路结构的第五构造的放大图。图1g是位于图1a的区域b内的应力减轻线路结构的第六构造的放大图。图1h是位于图1a的区域b内的应力减轻线路结构的第七构造的放大图。图1i是图1a的示例性结构的平面图。

89.参照图1a,根据本公开一些实施例的示例性结构可以包括形成在载体基板300上方的多个有机中介层400。有机中介层指的是包括至少一有机绝缘材料(例如,有机聚合物基质材料)的中介层。每个有机中介层400可以形成在个别的单元中介层区域(unit interposer area,uia)内。可以在载体基板300上形成有机中介层400的二维阵列。载体基板300可以是圆形晶圆或矩形晶圆。载体基板300的横向尺寸(例如,圆形晶圆的直径或矩形晶圆的边长)可以在100毫米(mm)到500毫米的范围内(例如,200毫米到400毫米),尽管也可以使用较小或较大的横向尺寸。载体基板300可以包括半导体基板、绝缘基板或导电基板。载体基板300可以是透明或不透明的。载体基板300的厚度可以足以为随后在其上形成的有机中介层400的阵列提供机械支撑。举例来说,载体基板300的厚度可以在60微米(microns)到1毫米的范围内,尽管也可以使用较小或较大的厚度。

90.可以将粘合剂层301施加到载体基板300的顶表面上。在一些实施例中,载体基板300可以包括例如玻璃或蓝宝石的光透明材料。在本实施例中,粘合剂层301可以包括光热转换(light-to-heat-conversion,lthc)层。光热转换层是使用旋转涂布方法施加的溶剂型涂层。光热转换层可以形成将紫外线光转换成热的层,从而使光热转换层失去粘附力。或者,粘合剂层301可以包括热分解的粘合剂材料。举例来说,粘合剂层301可以包括在高温下分解的丙烯酸压敏粘合剂(acrylic pressure-sensitive adhesive)。热分解的粘合剂材料的脱胶(debonding)温度可以在150度到400度的范围内。可在其他温度下分解的其他合适的热分解的粘合剂材料也在本公开的发明范围内。

91.随后可以在粘合剂层301上方形成凸块结构。这些凸块结构是后续用于提供与封装基板的接合,因此在本文中被称为封装侧(package-side)凸块结构18。封装侧凸块结构18可以包括可接合到焊料的任何金属材料。举例来说,可以在粘合剂层301上方沉积凸块下金属(underbump metallurgy,ubm)层堆叠(layer stack)。可以选择ubm层堆叠内的材料层的顺序,使得后续可以将焊料部分接合到ubm层堆叠的底表面的部分。可用于ubm层堆叠的层堆叠包括但不限于cr/cr-cu/cu/au、cr/cr-cu/cu、tiw/cr/cu、ti/ni/au和cr/cu/au的堆叠。其他合适的材料也在本公开的发明范围内。ubm层堆叠的厚度可以在5微米到60微米的范围内(例如,10微米到30微米),尽管也可以使用较小或较大的厚度。

92.可以在ubm层堆叠上方施加光阻层,并且可以对光阻层进行微影图案化以形成离散的图案化光阻材料部分的阵列。可以执行蚀刻制程以去除ubm层堆叠的未遮蔽的(unmasked)部分。蚀刻制程可以是等向性蚀刻制程或非等向性蚀刻制程。ubm层堆叠的留下部分包括封装侧凸块结构18。在一些实施例中,封装侧凸块结构18可以布置为二维阵列,其可以是二维周期阵列,例如矩形周期阵列。在一些实施例中,封装侧凸块结构18可形成为可控塌陷晶片连接(controlled collapse chip connection,c4)凸块结构。

93.根据本公开一些实施例,可以在封装侧凸块结构18的水平高度处形成应力减轻线路结构。在应力减轻线路结构形成在与封装侧凸块结构18相同的水平高度的实施例中,这样的应力减轻线路结构被称为封装侧应力减轻线路结构118。如本文中所使用的,线路结构是指以具有均匀的宽度或大致上均匀的宽度(即,宽度具有相对于结构的平均宽度小于50%的宽度变化)横向地延伸的结构。线路结构可以具有均匀的高度,并且可以是直线的、弯曲的、或者可以具有彼此邻接的多个线路段部,其中每个线路段部是直线的或弯曲的。如本文中所使用的,ㄍ路结构是指为了减轻对包括应力减轻线路结构的组件的应力的目的而使用的线路结构,使得组件内的另一结构在外部机械应力的作用下不会变形,而应力减轻线路结构则响应于外部机械应力而变形。

94.在一些实施例中,每个有机中介层400可以形成在一单元中介层区域uia内。每个单元中介层区域uia可以包括第一区域da1(也称为第一晶粒区域),其中第一半导体晶粒将被附接到有机中介层400,以及第二区域da2(也称为第二晶粒区域),其中第二半导体晶粒将被附接到有机中介层400。间隙区域gr位于第一区域da1与第二区域da2之间。通常,可以在每个单元中介层区域uia中设置多个不重叠区域,使得随后可以在每个不重叠区域内将半导体晶粒附接到有机中介层400。可以在每个单元中介层区域uia内的多个不重叠区域的每个相邻对之间设置间隙区域gr。尽管在此描述的各种实施例中使用了包括一第一区域da1和一第二区域da2的单元中介层区域uia,但是本公开的发明范围明确涵盖在单元中介

层区域uia内可包括用于接合半导体晶粒的三个或更多个区域以及在单元中介层区域uia内设置两个或更多个间隙区域gr的实施例。

95.封装侧应力减轻线路结构118可以形成在一个或多个及/或每个间隙区域gr中。在一些实施例中,可以通过图案化用于形成封装侧凸块结构18(例如,ubm层堆叠)的至少一金属材料,使得封装侧应力减轻线路结构118可与封装侧凸块结构18的形成同时形成。换句话说,所述至少一金属材料的图案化部分可包括封装侧凸块结构18和封装侧应力减轻线路结构118。在一些实施例中,可以在载体基板300上方沉积包括至少一金属材料(例如,ubm层堆叠)的原胚(blanket)材料层,并且可以在原胚材料层上方施加光阻层且对光阻层进行图案化。光阻层中的图案可以通过例如非等向性蚀刻制程的蚀刻制程转移到原胚材料层。原胚材料层的图案化部分可包括封装侧应力减轻线路结构118和封装侧凸块结构18。在本实施例中,封装侧应力减轻线路结构118可以包括与封装侧凸块结构18相同的材料,并可具有与封装侧凸块结构18相同的厚度。可以选择封装侧应力减轻线路结构118的图案和尺寸,使得封装侧应力减轻线路结构118可在封装侧凸块结构18或随后要形成的重分布线路结构的变形之前变形。

96.在另一些实施例中,可以通过沉积包括与封装侧凸块结构18的材料不同的材料的原胚材料层,使得封装侧应力减轻线路结构118可在封装侧凸块结构18的形成之前或之后形成。原胚材料层可以包括金属材料、半导体材料或介电材料。原胚材料层可以包括具有杨氏模数比随后要形成的重分布线路结构的材料的杨氏模数低的材料。举例来说,如果随后要形成的重分布线路结构包括铜(杨氏模数约为128gpa),则原胚材料层可以包括杨氏模数在1gpa到120gpa的范围内(例如,5gpa到100gpa)的材料。可用于原胚材料层的示例性材料包括但不限于铝、银、金、镓、铟、铅及氧化硅。可以在原胚材料层上方施加光阻层,并对光阻层进行图案化。光阻层中的图案可以通过例如非等向性蚀刻制程的蚀刻制程转移到原胚材料层。原胚材料层的图案化部分可包括封装侧应力减轻线路结构118。在本实施例中,封装侧应力减轻线路结构118可以包括与封装侧凸块结构18不同的材料,并可具有与封装侧凸块结构18不同的厚度。在一些实施例中,可以选择封装侧应力减轻线路结构118的图案和尺寸,使得封装侧应力减轻线路结构118容易在封装侧凸块结构18或随后要形成的重分布线路结构的变形之前变形。

97.可以在封装侧凸块结构18上方沉积介电材料层,在此称为封装侧介电材料层12。封装侧介电材料层12可以包括介电聚合物材料,例如聚酰亚胺(polyimide,pi)、苯并环丁烯(benzocyclobutene,bcb)或聚苯恶唑(polybenzobisoxazole,pbo)。其他合适的材料也在本公开的发明范围内。封装侧介电材料层12的厚度可以在4微米到60微米的范围内,尽管也可以使用较小或较大的厚度。封装侧凸块结构18内埋在载体基板300上方的封装侧介电材料层12内

98.随后可以在封装侧凸块结构18和封装侧介电材料层12上方形成多个重分布互连结构40和多个额外的介电材料层。所述额外的介电材料层在本文中统称为互连级(interconnect-level)介电材料层20。互连级介电材料层20可以包括多个介电材料层(22、24、26、28),例如第一介电材料层22、第二介电材料层24、第三介电材料层26以及第四介电材料层28。尽管在此描述的各种实施例中使用了四个介电材料层(22、24、26、28)内埋重分布互连结构40,但是本公开的发明范围明确涵盖互连级介电材料层20可包括两个、四个、五

个或更多个介电材料层的实施例。

99.通常,介电材料层(22、24、26、28)中的至少一者可以包括有机聚合物基质层,即,包括及/或基本上由有机聚合物组成的连续材料层。在一些实施例中,介电材料层(22、24、26、28)中的每一个可以包括有机聚合物基质层。因此,随后要形成的有机中介层包括至少一有机聚合物基质层。

100.重分布互连结构40包括多层重分布互连结构40,其分别形成为穿过介电材料层(22、24、26、28)中的一相应者。重分布互连结构40可以包括金属导孔(via)结构、金属线路结构、及/或整合式(integrated)线路和导孔结构。每个整合式线路和导孔结构包括包含一金属线路结构和至少一金属导孔结构的整体结构(unitary structure)。整体结构是指单个连续结构,其中结构内的每个点可以通过仅在结构内延伸的连续线(可以是直线,也可以不是直线)连接

101.在一说明性示例中,重分布互连结构40可以包括第一重分布互连结构42,其穿过第一介电材料层22及/或在第一介电材料层22的顶表面上而形成;第二重分布互连结构44,其穿过第二介电材料层24及/或在第二介电材料层24的顶表面上而形成;以及第三重分布互连结构46,其穿过第三介电材料层26及/或在第三介电材料层26的顶表面上而形成。尽管在此描述的各种实施例中重分布互连结构40是内埋在三个介电材料层(22、24、26)内,但是本公开的发明范围明确涵盖重分布互连结构40内埋在一个、两个、四个或更多个介电材料层内的实施例。

102.互连级介电材料层20中的每一者可以包括介电聚合物材料,例如聚酰亚胺(pi)、苯并环丁烯(bcb)或聚苯恶唑(pbo)。其他合适的材料也在本公开的发明范围内。每个互连级聚合物基质层20的厚度可以在4微米到20微米的范围内,尽管也可以使用较小或较大的厚度。重分布互连结构40中的每一者包括至少一金属材料,例如cu、mo、co、ru、w、tin、tan、wn、或其组合或堆叠。其他合适的材料也在本公开的发明范围内。举例来说,重分布互连结构40中的每一者可以包括tin层和cu层的层堆叠。在重分布互连结构40包括金属线路结构的实施例中,金属线路结构的厚度可以在2微米到20微米的范围内,尽管也可以使用较小或较大的厚度。

103.位于最顶部的金属互连级(level)的重分布互连结构40可以包括金属焊垫结构48。金属焊垫结构48可以形成在随后要形成晶粒侧凸块结构80的区域中。在一些实施例中,金属焊垫结构48可以形成为二维阵列。

104.在一些实施例中,金属焊垫结构48可以形成为包括一金属焊垫结构48和一金属导孔结构的个别的整体结构的焊垫部分。举例来说,金属焊垫结构48可以位于第三介电材料层26的顶表面上,并且金属导孔结构可以垂直地延伸穿过第三介电材料层26。连接到上方的金属焊垫结构48的每个金属导孔结构可以与相应的下面的重分布互连结构(可以是第二重分布互连结构44中的一者)的顶表面接触。

105.根据本公开一些实施例,可以在重分布互连结构40中的一或多者的水平高度(一或多级)处形成应力减轻线路结构。在应力减轻线路结构形成在与重分布互连结构40中的任一者(任一级)相同的水平高度的实施例中,这样的应力减轻线路结构被称为互连级应力减轻线路结构140。在一些实施例中,每个有机中介层400可以形成在一单元中介层区域uia内。每个单元中介层区域uia可以包括第一区域da1(也称为第一晶粒区域),其中第一半导

体晶粒将被附接到有机中介层400,以及第二区域da2(也称为第二晶粒区域),其中第二半导体晶粒将被附接到有机中介层400。间隙区域gr位于第一区域da1与第二区域da2之间及/或随后用于附接半导体晶粒的每个相邻区域之间。

106.互连级应力减轻线路结构140可以形成在一个或多个及/或每个间隙区域gr中。在一些实施例中,可以通过图案化用于形成重分布互连结构40的至少一金属材料,使得互连级应力减轻线路结构140可与重分布互连结构40的形成同时形成。换句话说,所述至少一金属材料的图案化部分可包括重分布互连结构40和互连级应力减轻线路结构140。在一些实施例中,可以在封装侧介电材料层12或互连级介电材料层20中的一者上方沉积包括至少一金属材料(例如,金属障蔽层和铜层的层堆叠)的原胚材料层,并且可以在原胚材料层上方施加光阻层且对光阻层进行图案化。光阻层中的图案可以通过例如非等向性蚀刻制程的蚀刻制程转移到原胚材料层。原胚材料层的图案化部分可包括互连级应力减轻线路结构140和重分布互连结构40。在本实施例中,互连级应力减轻线路结构140可以包括与重分布互连结构40相同的材料,并可具有与重分布互连结构40相同的厚度。可以选择互连级应力减轻线路结构140的图案和尺寸,使得互连级应力减轻线路结构140可在封装侧凸块结构18或重分布互连结构40的变形之前变形。

107.在另一些实施例中,可以通过沉积包括与重分布互连结构40中的一级的材料不同的材料的原胚材料层,使得互连级应力减轻线路结构140可在重分布互连结构40中的该级的形成之前或之后形成。原胚材料层可以包括金属材料、半导体材料或介电材料。原胚材料层可以包括具有杨氏模数比重分布互连结构40的材料的杨氏模数低的材料。举例来说,如果重分布互连结构40包括铜(杨氏模数约为128gpa),则原胚材料层可以包括杨氏模数在1gpa到120gpa的范围内(例如,5gpa到100gpa)的材料。可用于原胚材料层的示例性材料包括但不限于铝、银、金、镓、铟、铅及氧化硅。可以在原胚材料层上方施加光阻层,并对光阻层进行图案化。光阻层中的图案可以通过例如非等向性蚀刻制程的蚀刻制程转移到原胚材料层。原胚材料层的图案化部分可包括互连级应力减轻线路结构140。在本实施例中,互连级应力减轻线路结构140可以包括与重分布互连结构40不同的材料,并可具有与重分布互连结构40不同的厚度。在一些实施例中,可以选择互连级应力减轻线路结构140的图案和尺寸,使得在机械应力(其例如在接合制程中可能产生)的作用下,互连级应力减轻线路结构140容易在封装侧凸块结构18或重分布互连结构40的变形之前变形。

108.可以在每个有机中介层400的金属焊垫结构48和至少一金属基板46上方沉积额外的介电材料层。此额外的介电材料层在本文中被称为晶粒侧介电材料层60。晶粒侧介电材料层60包括介电聚合物材料,例如聚酰亚胺(pi)、苯并环丁烯(bcb)或聚苯恶唑(pbo)。其他合适的材料也在本公开的发明范围内。晶粒侧介电材料层60的厚度可以在4微米到60微米的范围内(例如,8微米到30微米),尽管也可以使用较小或较大的厚度。在本文中,封装侧介电材料层12、互连级介电材料层20和晶粒侧介电材料层60统称为介电材料层(12、20、60)。

109.可以在晶粒侧介电材料层60上方施加光阻层,并且可以对光阻层进行微影图案化以形成穿过其中的离散的开口。光阻层中的开口包括上覆于金属焊垫结构48中的一相应者的第一开口以及上覆于所述至少一金属基板46的第二开口。可以执行非等向性蚀刻,以将光阻层中的开口的图案转移到晶粒侧介电材料层60。由此,形成穿过晶粒侧介电材料层60的第一导孔孔穴和第二导孔孔穴。第一导孔孔穴延伸到金属焊垫结构48中的一相应者的顶

表面,而第二导孔孔穴延伸到所述至少一金属基板46的顶表面。

110.可以在凸块导孔孔穴中以及在晶粒侧介电材料层60的顶表面上方沉积至少一金属材料。所述至少一金属材料可以包括金属衬层和铜层。金属衬层可以包括例如ti、ta、w、tin、tan、wn或其组合的材料,并且可以具有在30纳米(nm)到300纳米的范围内的厚度。铜层可以具有在10微米到60微米的范围内的厚度,尽管也可以使用较小或较大的厚度。

111.可以在所述至少一金属材料上方施加光阻层,并且可对其进行微影图案化以覆盖离散的区域。可以执行蚀刻制程以去除所述至少一金属材料的未遮蔽的部分。所述至少一金属材料的每个图案化部分包括一凸块结构,其在本文中称为晶粒侧凸块结构80。晶粒侧凸块结构80可以包括形成在第一区域da1内的第一晶粒侧凸块结构80a以及形成在第二区域da2内的第二晶粒侧凸块结构80b。在一些实施例中,每个晶粒侧凸块结构80可以包括金属衬层和铜部分。结构上,每个晶粒侧凸块结构80可以包括延伸穿过晶粒侧介电材料层60并接触金属焊垫结构的凸块导孔部分、以及上覆于晶粒侧介电材料层60的接合凸块部分。在一些实施例中,每个接合凸块部分可以具有圆柱形状,即,具有圆形的水平截面的圆柱形状。每个接合凸块部分可以具有侧壁,其具有圆柱表面的形状。

112.根据本公开一些实施例,可以在晶粒侧凸块结构80的水平高度处形成应力减轻线路结构。在应力减轻线路结构形成在与晶粒侧凸块结构80相同的水平高度的实施例中,这样的应力减轻线路结构被称为晶粒侧应力减轻线路结构180。在一些实施例中,每个有机中介层400可以形成在一单元中介层区域uia内。每个单元中介层区域uia可以包括第一区域da1(也称为第一晶粒区域),其中第一半导体晶粒将被附接到有机中介层400,以及第二区域da2(也称为第二晶粒区域),其中第二半导体晶粒将被附接到有机中介层400。间隙区域gr位于第一区域da1与第二区域da2之间及/或随后用于附接半导体晶粒的每个相邻区域之间。

113.晶粒侧应力减轻线路结构180可以形成在一个或多个及/或每个间隙区域gr中。在一些实施例中,可以通过图案化用于形成晶粒侧凸块结构80的至少一金属材料,使得晶粒侧应力减轻线路结构180可与晶粒侧凸块结构80的形成同时形成。换句话说,所述至少一金属材料的图案化部分可包括晶粒侧凸块结构80和晶粒侧应力减轻线路结构180。在一些实施例中,可以在晶粒侧介电材料层60上方沉积包括至少一金属材料(例如,金属障蔽层和铜层的层堆叠)的原胚材料层,并且可以在原胚材料层上方施加光阻层且对光阻层进行图案化。光阻层中的图案可以通过例如非等向性蚀刻制程的蚀刻制程转移到原胚材料层。原胚材料层的图案化部分可包括晶粒侧凸块结构80和晶粒侧应力减轻线路结构180。在本实施例中,晶粒侧应力减轻线路结构180可以包括与晶粒侧凸块结构80相同的材料,并可具有与晶粒侧凸块结构80相同的厚度。可以选择晶粒侧应力减轻线路结构180的图案和尺寸,使得晶粒侧应力减轻线路结构180可在封装侧凸块结构18、重分布互连结构40或晶粒侧凸块结构80的变形之前变形。

114.在另一些实施例中,可以通过沉积包括与晶粒侧凸块结构80的材料不同的材料的原胚材料层,使得晶粒侧应力减轻线路结构180可在晶粒侧凸块结构80的形成之前或之后形成。原胚材料层可以包括金属材料、半导体材料或介电材料。原胚材料层可以包括具有杨氏模数比重分布互连结构40的材料的杨氏模数低的材料。举例来说,如果重分布互连结构40包括铜(杨氏模数约为128gpa),则原胚材料层可以包括杨氏模数在1gpa到120gpa的范围

内(例如,5gpa到100gpa)的材料。可用于原胚材料层的示例性材料包括但不限于铝、银、金、镓、铟、铅及氧化硅。可以在原胚材料层上方施加光阻层,并对光阻层进行图案化。光阻层中的图案可以通过例如非等向性蚀刻制程的蚀刻制程转移到原胚材料层。原胚材料层的图案化部分可包括晶粒侧应力减轻线路结构180。在本实施例中,晶粒侧应力减轻线路结构180可以包括与晶粒侧凸块结构80不同的材料,并可具有与晶粒侧凸块结构80不同的厚度。在一些实施例中,可以选择晶粒侧应力减轻线路结构180的图案和尺寸,使得在机械应力(其例如在接合制程中可能产生)的作用下,晶粒侧应力减轻线路结构180容易在封装侧凸块结构18、重分布互连结构40或晶粒侧凸块结构80的变形之前变形。

115.可用于应力减轻线路结构(118、140及/或180)的示例性图案如图1b到图1h所示。参照图1b到图1h,应力减轻线路结构(118、140及/或180)中的每一者可以包括多个直线段部(ls1、ls2),所述直线段部(ls1、ls2)沿各自的水平方向横向地延伸。在一些实施例中,应力减轻线路结构(118、140及/或180)中的每一者分别包括彼此平行的一组直线段部(ls1、ls2)。

116.在一些实施例中,应力减轻线路结构(118、140及/或180)可以横向地延伸到间隙区域gr的范围之外,并且延伸到第一区域da1和第二区域da2中,如图1b到图1d所示。在本实施例中,应力减轻线路结构118可以延伸穿过间隙区域gr,并可横向地突出到第一区域da1及/或第二区域da2中。在一些实施例中,应力减轻线路结构(118、140及/或180)可以包括金属材料,并可用作导电路径,作为第一区域da1与第二区域da2之间的信号路径。

117.在一些实施例中,应力减轻线路结构(118、140及/或180)可以完全位于间隙区域gr的范围内,因此不横向地延伸到第一区域da1或第二区域da2中,如图1e到图1h所示。在本实施例中,应力减轻线路结构(118、140及/或180)不电性连接到随后要形成的重分布互连结构。

118.在一些实施例中,应力减轻线路结构(118、140及/或180)中的每一者可以包括多个第一直线段部ls1,沿第一水平方向hd1横向地延伸,以及多个第二直线段部ls2,沿不同于第一水平方向hd1的第二水平方向hd2横向地延伸,如图1b、图1c以及图1e到图1h所示。第一水平方向hd1与第二水平方向hd2之间的角度可以在10度到145度的范围内。

119.在图1b、图1c、图1f以及图1g所示的实施例中,应力减轻线路结构中的每一者的第一直线段部ls1的侧壁和第二直线段部ls2的侧壁通过垂直边缘(vertical edges)彼此邻接。第一直线段部ls1的侧壁可以以小于180度的第一角度α和大于180度的第二角度β和第二直线段部ls2的侧壁邻接。

120.图1d和图1h所示的实施例中,应力减轻线路结构(118、140及/或180)的直线段部可以通过具有弯曲侧壁的曲线段部相互连接。

121.在图1e所示的实施例中,应力减轻线路结构(118、140及/或180)可以包括沿第一水平方向hd1横向地延伸的多个第一应力减轻线路结构(因此,包括沿第一水平方向hd1横向地延伸的多个第一第一直线段部ls1),以及沿第二水平方向hd2横向地延伸的多个第二应力减轻线路结构(因此,包括沿第二水平方向hd2横向地延伸的多个第二直线段部ls2)。应力减轻线路结构(118、140及/或180)可以布置为互连网(interconnected mesh),其中第一应力减轻线路结构和第二应力减轻线路结构以网格图案形式邻接。

122.共同参照图1a到图1i以及根据本公开各种实施例,提供有机中介层400,其包括:

介电材料层(12、20、60),内埋重分布互连结构40;封装侧凸块结构18,位于介电材料层(12、20、60)的第一侧,并连接到重分布互连结构40的封装侧子集(package-side subset);晶粒侧凸块结构80,位于介电材料层(12、20、60)的第二侧,并连接到重分布互连结构40的晶粒侧子集(die-side subset),其中,晶粒侧凸块结构80包括位于第一区域da1中的第一晶粒侧凸块结构80a和位于第二区域da2中的第二晶粒侧凸块结构80b,在平面图中(即,沿着垂直于介电材料层(12、20、60)的水平面的垂直方向的视图),第二区域da2与第一区域da1横向地间隔开一间隙区域gr,在间隙区域gr中没有任何晶粒侧凸块结构80;以及应力减轻线路结构(118、140及/或180),位于在平面图中在间隙区域gr的范围内的介电材料层(12、20、60)之上或之内。其中,应力减轻线路结构(118、140及/或180)与封装侧凸块结构18、重分布互连结构40和晶粒侧凸块结构80中的一者包括相同的材料且位于相同的水平高度。

123.在一些实施例中,应力减轻线路结构(118、140及/或180)中的每一者包括沿各自的水平方向横向地延伸的多个直线段部,并且不电性连接到重分布互连结构40。

124.在一些实施例中,应力减轻线路结构(118、140及/或180)中的每一者包括:多个第一直线段部ls1,沿第一水平方向hd1横向地延伸;以及多个第二直线段部ls2,沿不同于第一水平方向hd1的第二水平方向hd2横向地延伸。在一些实施例中,应力减轻线路结构中的每一者的第一直线段部的侧壁和第二直线段部的侧壁通过垂直边缘彼此邻接。在一些实施例中,直线段部通过具有弯曲侧壁的曲线段部彼此相连。

125.在一些实施例中,应力减轻线路结构(118、140及/或180)包括沿第一水平方向横向地延伸的多个第一应力减轻线路结构,以及沿第二水平方向横向地延伸的多个第二应力减轻线路结构。并且,应力减轻线路结构是布置为互连网,其中第一应力减轻线路结构和第二应力减轻线路结构以网格图案形式邻接,如图1e所示。

126.在一些实施例中,介电材料层(12、20、60)包括晶粒侧介电材料层60。晶粒侧凸块结构80各自包括与晶粒侧介电材料层60的水平面接触的水平面。应力减轻线路结构(在应力减轻线路结构包括晶粒侧应力减轻线路结构180的实施例中)与晶粒侧介电材料层60的水平面接触。并且,应力减轻线路结构具有与晶粒侧凸块结构80相同的材料组成和相同的厚度。

127.在一些实施例中,介电材料层(12、20、60)包括封装侧介电材料层12,封装侧介电材料层12内埋封装侧凸块结构18和应力减轻线路结构(在应力减轻线路结构包括封装侧应力减轻线路结构180的实施例中)。并且,封装侧凸块结构18的水平面和不与介电材料层(12、20、60)或重分布互连结构40接触的应力减轻线路结构的水平面位于同一水平平面(例如,包括有机中介层400的最底表面的水平平面)内。在一些实施例中,应力减轻线路结构具有与封装侧凸块结构18相同的材料组成和相同的厚度。

128.在一些实施例中,应力减轻线路结构(在应力减轻线路结构包括互连级应力减轻线路结构140的实施例中)内埋在介电材料层(12、20、60)内,并位于一第一水平平面与一第二水平平面之间,第一水平平面包括封装侧凸块结构18与重分布互连结构40中的第一子集之间的界面,第二水平平面包括晶粒侧凸块结构80与重分布互连结构40中的第二子集之间的界面。在一些实施例中,应力减轻线路结构具有与重分布互连结构40中的一子集相同的材料组成和相同的厚度,其中该子集与第一子集和第二子集中的一者不同或相同。

129.根据本公开另一些实施例,提供有机中介层400,其包括:介电材料层(12、20、60),

内埋重分布互连结构40;封装侧凸块结构18,位于介电材料层(12、20、60)的第一侧,并连接到重分布互连结构40的封装侧子集;晶粒侧凸块结构80,位于介电材料层(12、20、60)的第二侧,并连接到重分布互连结构40的晶粒侧子集,其中,晶粒侧凸块结构80包括位于第一区域da1中的第一晶粒侧凸块结构80a和位于第二区域da2中的第二晶粒侧凸块结构80b,在平面图中,第二区域da2与第一区域da1横向地间隔开一间隙区域gr,在间隙区域gr中没有任何晶粒侧凸块结构80;以及应力减轻线路结构(118、140及/或180),位于在平面图中在间隙区域gr的范围内的介电材料层(12、20、60)之上或之内。其中,应力减轻线路结构(118、140及/或180)与从封装侧凸块结构18、重分布互连结构40和晶粒侧凸块结构80中选择的一金属部件位于相同的水平高度。其中,应力减轻线路结构(118、140及/或180)包括所述金属部件不同的材料。

130.在一些实施例中,介电材料层(12、20、60)包括晶粒侧介电材料层60。晶粒侧凸块结构80各自包括与晶粒侧介电材料层60的水平面接触的水平面。应力减轻线路结构(在应力减轻线路结构包括晶粒侧应力减轻线路结构180的实施例中)与晶粒侧介电材料层60的水平面接触。并且,应力减轻线路结构具有与晶粒侧凸块结构80不同的材料组成或不同的厚度。

131.在一些实施例中,介电材料层(12、20、60)包括封装侧介电材料层12,封装侧介电材料层12内埋封装侧凸块结构18和应力减轻线路结构(在应力减轻线路结构包括封装侧应力减轻线路结构180的实施例中)。封装侧凸块结构18的水平面和不与介电材料层(12、20、60)或重分布互连结构40接触的应力减轻线路结构的水平面位于同一水平平面(例如,包括封装侧介电材料层12的最底表面的水平平面)内。并且,应力减轻线路结构具有与封装侧凸块结构18不同的材料组成或不同的厚度。

132.在一些实施例中,应力减轻线路结构(在应力减轻线路结构包括互连级应力减轻线路结构140的实施例中)内埋在介电材料层(12、20、60)内,并位于一第一水平平面与一第二水平平面之间,第一水平平面包括封装侧凸块结构18与重分布互连结构40中的第一子集之间的界面,第二水平平面包括晶粒侧凸块结构80与重分布互连结构40中的第二子集之间的界面。并且,应力减轻线路结构具有与重分布互连结构不同的材料组成。

133.在一些实施例中,晶粒侧凸块结构80各自包括与晶粒侧介电材料层60的水平面接触的水平面,并且应力减轻线路结构(例如,晶粒侧应力减轻线路结构180)与晶粒侧介电材料层60的水平面接触。

134.图2是根据本公开一些实施例的在将半导体晶粒附接到有机中介层之后的示例性结构的垂直截面图。至少一半导体晶粒(701、702)可以附接到各个有机中介层400。每个半导体晶粒(701、702)可以通过焊料部分788接合到在个别的单元中介层区域uia内的晶粒侧凸块结构80中的相应的子集(subset)。每个半导体晶粒(701、702)可以包括晶粒凸块结构708。在一些实施例中,晶粒凸块结构708可以包括微凸块结构的二维阵列,并且每个半导体晶粒(701、702)可以通过c2接合(即,一对微凸块之间的焊料接合)附接到晶粒侧凸块结构80。在将半导体晶粒(701、702)的晶粒凸块结构708设置在焊料部分788的阵列上方之后,可以执行c2接合制程,使焊料部分788回焊(reflow)。

135.所述至少一半导体晶粒(701、702)可以包括本领域中已知的任何半导体晶粒。在一些实施例中,所述至少一半导体晶粒(701、702)可以包括晶片上系统(system-on-chip,

soc)晶粒,例如应用处理器晶粒。在一些实施例中,所述至少一半导体晶粒(701、702)可以包括多个半导体晶粒(701、702)。在一些实施例中,多个半导体晶粒(701、702)可以包括第一半导体晶粒701和至少一第二半导体晶粒702。在一些实施例中,第一半导体晶粒701可以是中央处理单元晶粒,而所述至少一第二半导体晶粒702可以包括图形处理单元晶粒。在另一些实施例中,第一半导体晶粒701可以包括晶片上系统(soc)晶粒,而所述至少一第二半导体晶粒702可以包括至少一高频宽存储器(high bandwidth memory,hbm)晶粒,每个高频宽存储器晶粒都包括多个静态随机存取存储器晶粒的垂直堆叠,并提供根据jedec标准(即,jedec固态技术协会所定义的标准)定义的高频宽。附接到同一有机中介层400的半导体晶粒(701、702)的顶表面可以位于同一水平平面内。通常,至少一半导体晶粒(701、702)可以通过至少一组焊料部分788附接到晶粒侧凸块结构80。

136.图3是根据本公开一些实施例的在形成扇出晶圆级封装之后的示例性结构的垂直截面图。至少一底部填充材料部分780可以形成在每一组接合的焊料部分788的周围。在对焊料部分788回焊之后,可通过在焊料部分788的阵列的周围注入底部填充材料来形成各个底部填充材料部分780。可以使用任何已知的底部填充材料施加方法,其可以是例如毛细力(capillary)底部填充方法、模制(molded)底部填充方法或印刷底部填充方法。在一些实施例中,多个半导体晶粒(701、702)可以附接到在每个单元中介层区域uia内的有机中介载层400,并且单个底部填充材料部分780可以在多个半导体晶粒(701、702)的下方连续地延伸。

137.根据本公开一些实施例,应力减轻线路结构(118、140、180)可以在底部填充材料的施加和固化期间吸收到有机中介层400的机械应力。具体地,底部填充材料施加过程可对晶粒侧介电材料层60施加压力。应力减轻线路结构(118、140、180)可响应于机械应力而变形,使得位于第一区域da1和第二区域da2内有机中介层400的部分在底部填充材料施加过程中或在随后可产生机械应力的过程中变形较少。

138.环氧模塑料(epoxy molding compound,emc)被施加到有机中介层400和半导体晶粒(701、702)之间的间隙。emc包括可硬化(即固化)的含环氧基的化合物,以提供具有足够刚性和机械强度的介电材料部分。emc可以包括环氧树脂、硬化剂、二氧化硅(作为填充材料)和其他添加剂。emc可以以液体形式或固体形式来提供,取决于其粘度和流动性。液体的emc可以提供较好的操控性、良好的流动性、较少的空隙、较好的填充效果和较少的流痕(flow marks)。固体的emc可以减少固化收缩率、提高支撑力和减少晶粒漂移。emc内较高的填料含量(例如,重量的85%)可以缩短成模的时间、降低模具收缩率(mold shrinkage)和减少模具翘曲。emc中填料尺寸的均匀分布可以减少流痕,并可以提高流动性。emc的固化温度可以低于粘合剂层301的释放(脱胶)温度。举例来说,emc的固化温度可以在125℃到150℃的范围内。

139.可以在固化温度下固化emc,以形成横向地包围每个半导体晶粒(701、702)的emc基质(matrix)。emc基质包括彼此横向地邻接的多个emc晶粒框架790。每个emc晶粒框架790位于个别的单元中介层区域uia内,并且横向地围绕和内埋至少一半导体晶粒(701、702)的相应集合(可以是多个半导体晶粒(701、702))。可以通过平坦化制程(可使用化学机械平坦化方法)从包括半导体晶粒(701、702)的顶表面的水平平面上方去除emc的多余部分。

140.图4是根据本公开一些实施例的在切割扇出晶圆级封装之后的示例性结构的垂直截面图。可以将载体基板300与有机中介层板400、半导体晶粒(701、702)和emc晶粒框架790

的组件分离。可以例如通过在高温下的热退火而使粘合剂层301失去活性。实施例可以包括粘合剂层301,其具有热去活性的(thermally-deactivated)粘合剂材料。在粘合剂层301可以是透明的其他实施例中,粘合剂层301可以具有紫外线去活性的(ultraviolet-deactivated)粘合剂材料。

141.可以沿着切割通道切割有机中介层400、半导体晶粒(701、702)和emc晶粒框架790的组件,所述切割通道是位于单元中介层区域uia的边界。有机中介层400、半导体晶粒(701、702)和emc晶粒框架790的每个经切割的部分包括扇出晶圆级封装(fan-out wafer-level package,fowlp),其包括至少一半导体晶粒(701、702)(可以是多个半导体晶粒)、有机中介层400、底部填充材料部分780以及emc框架790。emc晶粒框架790和有机中介层400可以具有垂直地重合的侧壁,即,两者的侧壁位于同一垂直平面内。在扇出晶圆级封装包括多个半导体晶粒(701、702)的实施例中,底部填充材料部分780可以接触多个半导体晶粒(701、702)的侧壁。emc晶粒框架790在扇出晶圆级封装内的所述至少一半导体晶粒(701、702)的周围连续地延伸,并横向地包围半导体晶粒(701、702)。

142.图5是根据本公开一些实施例的在将封装基板附接到扇出晶圆级封装之后的示例性结构的垂直截面图。参照图5,提供封装基板200。封装基板200可以是包括核心基板210的有核心(cored)封装基板、或者是不包括封装核心的无核心(coreless)封装基板。或者,封装基板200可以包括系统整合封装基板(system-integrated package substrate,sois),其包括重分布层及/或介电中间层、至少一内埋的中介层(例如,硅中介层)。这样的系统整合封装基板可以包括使用焊料部分、微凸块、底部填充材料部分(例如,模制底部填充材料部分)及/或粘合膜的层到层互连(layer-to-layer interconnections)。尽管在此使用一示例性封装基板来描述本公开实施例,但是应当理解,本公开的发明范围不以任何特殊类型的封装基板为限制,并可以包括系统整合封装基板(sois)。

143.核心基板210可以包括玻璃环氧树脂板(glass epoxy plate),其包括贯穿板孔(through-plate holes)的阵列。可以在贯穿板孔中设置包括金属材料的贯穿核心导孔结构(through-core via structures)214。每个贯穿核心导孔结构214可以或可以不包括圆柱形空心内部。可选地,介电衬层212可用于将贯穿核心导孔结构214与核心基板210电性隔离。

144.封装基板200可以包括板侧(board-side)表面增层电路(surface laminar circuit,slc)240和晶片侧表面增层电路(slc)260。板侧表面增层电路240可以包括内埋板侧布线互连(board-side wiring interconnects)244的板侧绝缘层242。晶片侧表面增层电路260可以包括内埋晶片侧布线互连264的晶片侧绝缘层262。板侧绝缘层242和晶片侧绝缘层262可以包括光敏环氧树脂材料,其可以被微影图案化以及随后被固化。内埋板侧布线互连244和内埋晶片侧布线互连264可以包括铜,其可以通过电镀沉积在板侧绝缘层242或晶片侧绝缘层262中的图案内。板侧接合焊垫248的阵列可以电性连接到内埋板侧布线互连244,并可以配置为允许通过焊球进行接合。晶片侧接合焊垫268的阵列可以电性连接到晶片侧布线互连264,并可以配置为允许通过c4焊球进行接合。

145.可以将附接到有机中介层400、至少一半导体晶粒(701、702)和emc晶粒框架790的组件的封装侧凸块结构18的焊料部分450设置在封装基板200的晶片侧接合焊垫268的阵列上。可以执行回焊制程以使焊料部分450回焊,从而引起有机中介层400与封装基板200之间

的接合。在一些实施例中,焊料部分450可以包括c4焊球,并且有机中介层400、所述至少一半导体晶粒(701、702)和emc晶粒框架790的组件可以使用c4焊球的阵列附接到封装基板200。可以通过施加底部填充材料并对其塑形,以在焊料部分450的周围形成底部填充材料部分292。可选地,可以将例如盖结构或环结构的稳定结构294附接到有机中介层400、所述至少一半导体晶粒(701、702)、emc晶粒框架790和封装基板200的组件上,以减少所述组件在后续的处理步骤中及/或组件的使用期间的变形。

146.图6是根据本公开一些实施例的在将封装基板附接到印刷电路板(pcb)之后的示例性结构的垂直截面图。参照图6,提供印刷电路板(pcb)100,其包括pcb基板110和pcb接合焊垫188。pcb基板110至少在pcb基板110的一侧上包括印刷电路(未示出)。可以形成焊料接点190的阵列,以将板侧接合焊垫248的阵列接合到pcb接合焊垫188的阵列。可以通过在板侧接合焊垫248的阵列与pcb接合焊垫188的阵列之间设置焊球的阵列,并通过回焊焊球的阵列,来形成焊料接点190。可以通过施加底部填充材料并对其塑形,以在焊料接点190的周围形成底部填充材料部分192。封装基板200通过焊料接点190的阵列附接到pcb基板110。

147.图7a是示出根据本公开一些实施例的用于形成有机中介层的第一种处理步骤顺序的第一流程图。参照步骤710和图1a到图1i,在载体基板300上方形成内埋在封装侧介电材料层12中封装侧凸块结构18。参照步骤712和图1a到图1i,在平面图中在间隙区域gr的范围内的封装侧介电材料层12之内及/或之上形成应力减轻线路结构(例如,封装侧应力减轻线路结构118)。每个应力减轻线路结构包括沿各自的水平方向横向地延伸的多个直线段部。应力减轻线路结构可以与封装侧凸块结构18位于相同水平高度。参照步骤720和图1a到图1h,在封装侧凸块结构18上方形成互连级介电材料层20和重分布互连结构40。在一些实施例中,应力减轻线路结构(例如,封装侧应力减轻线路结构118)不电性连接到重分布互连结构40。参照步骤730和图1a到图1i,在互连级介电材料层20上方形成晶粒侧介电材料层60。参照步骤740和图1a到图1i,在晶粒侧介电材料层60上方形成晶粒侧凸块结构80。晶粒侧凸块结构80包括位于第一区域da1中的第一晶粒侧凸块结构80a和位于第二区域da2中的第二晶粒侧凸块结构80b,在平面图中,第二区域da2与第一区域da1横向地间隔开一间隙区域gr,在间隙区域gr中没有任何晶粒侧凸块结构80。

148.图7b是示出根据本公开一些实施例的用于形成有机中介层的第二种处理步骤顺序的第二流程图。参照步骤710和图1a到图1i,在载体基板300上方形成内埋在封装侧介电材料层12中封装侧凸块结构18。参照步骤720和图1a到图1h,在封装侧凸块结构18上方形成互连级介电材料层20和重分布互连结构40。参照步骤722和图1a到图1i,在平面图中在间隙区域gr的范围内的互连级介电材料层20之内及/或之上形成应力减轻线路结构(例如,互连级应力减轻线路结构140)。每个应力减轻线路结构包括沿各自的水平方向横向地延伸的多个直线段部。应力减轻线路结构可以与重分布互连结构40位于相同水平高度。在一些实施例中,应力减轻线路结构(例如,互连级应力减轻线路结构140)不电性连接到重分布互连结构40。参照步骤730和图1a到图1i,在互连级介电材料层20上方形成晶粒侧介电材料层60。参照步骤740和图1a到图1i,在晶粒侧介电材料层60上方形成晶粒侧凸块结构80。晶粒侧凸块结构80包括位于第一区域da1中的第一晶粒侧凸块结构80a和位于第二区域da2中的第二晶粒侧凸块结构80b,在平面图中,第二区域da2与第一区域da1横向地间隔开一间隙区域gr,在间隙区域gr中没有任何晶粒侧凸块结构80。

149.图7c是示出根据本公开一些实施例的用于形成有机中介层的第三种处理步骤顺序的第三流程图。参照步骤710和图1a到图1i,在载体基板300上方形成内埋在封装侧介电材料层12中封装侧凸块结构18。参照步骤720和图1a到图1h,在封装侧凸块结构18上方形成互连级介电材料层20和重分布互连结构40。参照步骤730和图1a到图1i,在互连级介电材料层20上方形成晶粒侧介电材料层60。参照步骤740和图1a到图1i,在晶粒侧介电材料层60上方形成晶粒侧凸块结构80。晶粒侧凸块结构80包括位于第一区域da1中的第一晶粒侧凸块结构80a和位于第二区域da2中的第二晶粒侧凸块结构80b,在平面图中,第二区域da2与第一区域da1横向地间隔开一间隙区域gr,在间隙区域gr中没有任何晶粒侧凸块结构80。参照步骤742和图1a到图1i,在平面图中在间隙区域gr的范围内的晶粒侧介电材料层60之内及/或之上形成应力减轻线路结构(例如,晶粒侧应力减轻线路结构180)。每个应力减轻线路结构包括沿各自的水平方向横向地延伸的多个直线段部。应力减轻线路结构可以与晶粒侧凸块结构80位于相同水平高度。在一些实施例中,应力减轻线路结构(例如,晶粒侧应力减轻线路结构180)不电性连接到重分布互连结构40。

150.本公开各种实施例可用于提供有机中介层400以及包括有机中介层400、半导体晶粒(701、702)和封装基板200的半导体结构。有机中介层400包括应力减轻线路结构(118、140、180),应力减轻线路结构(118、140、180)可以有利地用于在不存在半导体晶粒(701、702)的范围中(即,在间隙区域gr中)引起变形,而不是在平面图中与半导体晶粒(701、702)在面积上重叠的区域内的有机中介层400中的变形。因此,可以提高包括有机中介层400和多个半导体晶粒(701、702)的扇出晶圆级封装(fowlp)的良率。

151.根据本公开一些实施例,提供一种有机中介层。所述有机中介层包括多个介电材料层、多个封装侧凸块结构、多个晶粒侧凸块结构以及多个应力减轻线路结构。所述介电材料层内埋多个重分布互连结构。所述封装侧凸块结构位于所述介电材料层的第一侧,并连接到所述重分布互连结构中的封装侧子集。所述晶粒侧凸块结构位于所述介电材料层的第二侧,并连接到所述重分布互连结构中的晶粒侧子集。其中,所述晶粒侧凸块结构包括位于一第一区域中的多个第一晶粒侧凸块结构和位于一第二区域中的多个第二晶粒侧凸块结构。在平面图中,第二区域与第一区域横向地间隔开一间隙区域,在间隙区域中没有任何晶粒侧凸块结构。所述应力减轻线路结构位于在平面图中在间隙区域的范围内的所述介电材料层之上或之内。其中,所述应力减轻线路结构与所述封装侧凸块结构、所述重分布互连结构和所述晶粒侧凸块结构中之一者包括相同的材料且位于相同的水平高度。

152.在一些实施例中,应力减轻线路结构中的每一者包括沿各自的水平方向横向地延伸的多个直线段部,并且不电性连接到重分布互连结构。在一些实施例中,应力减轻线路结构中的每一者包括:多个第一直线段部,沿一第一水平方向横向地延伸;以及多个第二直线段部,沿不同于第一水平方向的一第二水平方向横向地延伸。在一些实施例中,应力减轻线路结构中的每一者的第一直线段部的侧壁和第二直线段部的侧壁通过多个垂直边缘彼此邻接。在一些实施例中,应力减轻线路结构中的每一者的直线段部通过具有弯曲侧壁的多个曲线段部相互连接。在一些实施例中,应力减轻线路结构包括沿一第一水平方向横向地延伸的多个第一应力减轻线路结构和沿一第二水平方向横向地延伸的多个第二应力减轻线路结构,并且应力减轻线路结构布置为互连网,其中第一应力减轻线路结构和第二应力减轻线路结构以网格图案形式邻接。在一些实施例中,介电材料层包括晶粒侧介电材料层,

晶粒侧凸块结构各自包括与晶粒侧介电材料层的水平面接触的水平面,应力减轻线路结构与晶粒侧介电材料层的水平面接触,并且应力减轻线路结构具有与晶粒侧凸块结构相同的材料组成和相同的厚度。在一些实施例中,介电材料层包括封装侧介电材料层,封装侧介电材料层内埋封装侧凸块结构和应力减轻线路结构,并且封装侧凸块结构的水平面和不与介电材料层或重分布互连结构接触的应力减轻线路结构的水平面位于同一水平平面内。在一些实施例中,应力减轻线路结构具有与封装侧凸块结构相同的材料组成和相同的厚度。在一些实施例中,应力减轻线路结构内埋在介电材料层内,并位于一第一水平平面与一第二水平平面之间,第一水平平面包括封装侧凸块结构与重分布互连结构中的第一子集之间的界面,第二水平平面包括晶粒侧凸块结构与重分布互连结构中的第二子集之间的界面。在一些实施例中,应力减轻线路结构具有与重分布互连结构中的一子集相同的材料组成和相同的厚度,该子集与第一子集和第二子集中的一者不同或相同。

153.根据本公开另一些实施例,提供一种有机中介层。所述有机中介层包括多个介电材料层、多个封装侧凸块结构、多个晶粒侧凸块结构以及多个应力减轻线路结构。所述介电材料层内埋多个重分布互连结构。所述封装侧凸块结构位于所述介电材料层的第一侧,并连接到所述重分布互连结构中的封装侧子集。所述晶粒侧凸块结构位于所述介电材料层的第二侧,并连接到所述重分布互连结构中的晶粒侧子集。其中,所述晶粒侧凸块结构包括位于一第一区域中的多个第一晶粒侧凸块结构和位于一第二区域中的多个第二晶粒侧凸块结构。在平面图中,第二区域与第一区域横向地间隔开一间隙区域,在间隙区域中没有任何晶粒侧凸块结构。所述应力减轻线路结构位于在平面图中在间隙区域的范围内的所述介电材料层之上或之内。其中,所述应力减轻线路结构与从所述封装侧凸块结构、所述重分布互连结构和所述晶粒侧凸块结构中选择的一金属部件位于相同的水平高度。其中,所述应力减轻线路结构包括与金属部件不同的材料。

154.在一些实施例中,介电材料层包括晶粒侧介电材料层,晶粒侧凸块结构各自包括与晶粒侧介电材料层的水平面接触的水平面,应力减轻线路结构与晶粒侧介电材料层的水平面接触,并且应力减轻线路结构具有与晶粒侧凸块结构不同的材料组成或不同的厚度。在一些实施例中,介电材料层包括封装侧介电材料层,封装侧介电材料层内埋封装侧凸块结构和应力减轻线路结构,封装侧凸块结构的水平面和不与介电材料层或重分布互连结构接触的应力减轻线路结构的水平面位于同一水平平面内,并且应力减轻线路结构具有与封装侧凸块结构不同的材料组成或不同的厚度。在一些实施例中,应力减轻线路结构内埋在介电材料层内,并位于一第一水平平面与一第二水平平面之间,第一水平平面包括封装侧凸块结构与重分布互连结构中的第一子集之间的界面,第二水平平面包括晶粒侧凸块结构与重分布互连结构中的第二子集之间的界面,并且应力减轻线路结构具有与重分布互连结构不同的材料组成。

155.根据本公开又另一些实施例,提供一种形成有机中介层的方法。所述方法包括在载体基板上方形成内埋在封装侧介电材料层内的多个封装侧凸块结构。所述方法也包括在所述封装侧凸块结构上方形成多个互连级介电材料层和多个重分布互连结构。所述方法还包括在所述互连级介电材料层上方形成晶粒侧介电材料层。所述方法还包括在晶粒侧介电材料层上方形成多个晶粒侧凸块结构。其中,所述晶粒侧凸块结构包括位于一第一区域中的多个第一晶粒侧凸块结构和位于一第二区域中的多个第二晶粒侧凸块结构。在平面图

中,第二区域与第一区域横向地间隔开一间隙区域,在间隙区域中没有任何晶粒侧凸块结构。此外,所述方法包括在平面图中在间隙区域的范围内的封装侧介电材料层、所述互连级介电材料层或晶粒侧介电材料层中的一者之内或之上形成多个应力减轻线路结构。其中,所述应力减轻线路结构中的每一者包括沿各自的水平方向横向地延伸的多个直线段部,并且所述应力减轻线路结构具有选自以下的至少一特征:所述应力减轻线路结构不电性连接到所述重分布互连结构;以及所述应力减轻线路结构与所述封装侧凸块结构或所述晶粒侧凸块结构位于相同的水平高度。

156.在一些实施例中,应力减轻线路结构与封装侧凸块结构、重分布互连结构和晶粒侧凸块结构中的一者包括相同的材料且位于相同的水平高度。在一些实施例中,应力减轻线路结构与选自以下的一金属部件位于相同的水平高度:封装侧凸块结构、重分布互连结构以及晶粒侧凸块结构,并且应力减轻线路结构包括与所述金属部件不同的材料。在一些实施例中,应力减轻线路结构的材料的杨氏模数小于所述金属部件的杨氏模数。在一些实施例中,应力减轻线路结构通过以下步骤而形成:在载体基板、封装侧介电材料层、互连级介电材料层或晶粒侧介电材料层上方沉积原胚材料层;在原胚材料层上方施加光阻层,并图案化光阻层;以及将光阻层中的图案转移到原胚材料层。其中,原胚材料层的图案化部分包括应力减轻线路结构,并且应力减轻线路结构中的每一者分别包括一组彼此平行的直线段部。

157.前述内文概述了许多实施例的特征,使本技术领域中具有通常知识者可以从各个方面更佳地了解本公开。本技术领域中具有通常知识者应可理解,且可轻易地以本公开为基础来设计或修饰其他制程及结构,并以此达到相同的目的及/或达到与在此介绍的实施例等相同的优点。本技术领域中具有通常知识者也应了解这些相等的结构并未背离本公开的发明精神与范围。在不背离本公开的发明精神与范围的前提下,可对本公开进行各种改变、置换或修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1