线圈部件及其制造方法与流程

1.本发明涉及线圈部件及其制造方法,尤其涉及具有将螺旋状的线圈图案埋入素体的结构的线圈部件及其制造方法。

背景技术:

2.作为具有将螺旋状的线圈图案埋入素体的结构的线圈部件,已知有专利文献1所记载的线圈部件。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2006-324489号公报

技术实现要素:

6.发明所要解决的问题

7.然而,在专利文献1所记载的线圈部件中,难以充分地提高自谐振频率(srf)。

8.因此,本发明的目的在于,在具有将螺旋状的线圈图案埋入素体的结构的线圈部件,提高自谐振频率。

9.用于解决问题的手段

10.本发明的线圈部件具备:素体;线圈图案,埋入素体并且跨多匝呈螺旋状地卷绕;以及第1端子电极及第2端子电极,设置于素体的表面,分别与线圈图案的一端及另一端连接,素体包括:形成有腔室的支撑体以及层叠于支撑体以覆盖腔室的第1绝缘层,从而在素体的内部形成有空洞,线圈图案包括:沿腔室的内壁而设置的多个第1区间和设置于第1绝缘层上的多个第2区间,多个第1区间的一端及与其对应的多个第2区间的一端相互连接,多个第1区间的另一端及与其对应的多个第2区间的另一端相互连接。

11.根据本发明,由于线圈图案的内径区域的大部分由空洞构成,因此,能够大幅降低在线圈图案的相邻的匝间产生的杂散电容。由此,能够提高自谐振频率。

12.在本发明中,也可以是,素体还包括覆盖腔室的内壁的第2绝缘层,线圈图案的第1区间经由第2绝缘层设置于腔室的内壁。由此,可以将具有导电性的材料作为支撑体的材料。在这种情况下,也可以是,支撑体由硅构成。由此,容易在支撑体形成空洞。

13.在本发明中,也可以是,第1绝缘层由树脂类绝缘材料构成。由此,由于第1绝缘层具备柔软性,因此,即使在施加外力的情况下,覆盖空洞的部分也不容易破损。在这种情况下,也可以是,在构成第1绝缘层的树脂类绝缘材料中添加填料。由此,够提高第1绝缘层的强度。

14.在本发明中,也可以是,素体还包括:第3绝缘层,覆盖第1绝缘层以将多个第2区间埋入并且由树脂类绝缘材料构成,第1端子电极以及第2端子电极设置于第3绝缘层上,构成第3绝缘层的树脂类绝缘材料比构成第1绝缘层的树脂绝缘材料的的介电常数低。由此,能够降低在第1端子电极以及第2端子电极和线圈图案之间产生的杂散电容。

15.在本发明中,也可以是,第1端子电极以及第2端子电极在线圈图案的轴向上排列。由此,由于抑制了第1端子电极以及第2端子电极和线圈图案之间的电位差,因此,进一步降低杂散电容。

16.在这种情况下,也可以是,第1端子电极以及第2端子电极未形成于与轴向垂直的素体的表面,而形成于沿着轴向的素体的表面。由此,由于磁通量难以与第1端子电极以及第2端子电极发生干扰,因此,能够抑制涡电流的产生。

17.本发明的线圈部件的制造方法包括:第1工序,将空洞形成于支撑体;第2工序,沿着腔室的内壁形成线圈图案的多个第1区间;第3工序,通过由第1绝缘层覆盖腔室来形成空洞;第4工序,通过在第1绝缘层形成开口部,使多个第1区间的一端及另一端露出;以及第5工序,通过在第1绝缘层上形成线圈图案的多个第2区间,来将多个第1区间的一端以及与其对应的多个第2区间的一端相互连接,并且将多个第1区间的另一端以及与其对应的多个第2区间的另一端相互连接的。

18.根据本发明,能够很容易地制作具有内径区域的大部分为空洞的线圈图案的线圈部件。

19.也可以是,本发明的线圈部件的制造方法还具备:在进行第1工序之后并且在进行第2工序之前,形成覆盖腔室的内壁的第2绝缘层的工序。由此,能够将具有导电性的材料用作支撑体的材料。

20.也可以是,本发明的线圈部件的制造方法还具备:第6工序,在第1绝缘层上形成由树脂类绝缘材料构成的第3绝缘层以将多个第2区间埋入;以及第7工序,在第3绝缘层上形成分别与线圈图案的一端以及另一端连接的第1端子电极以及第2端子电极,第1绝缘层由树脂类绝缘材料构成,构成第3绝缘层的树脂类绝缘材料比构成所述第1绝缘层的树脂绝缘材料的的相对介电常数低。

21.发明效果

22.根据本发明,在具有将螺旋状的线圈图案埋入素体的结构的线圈部件,能够提高自谐振频率。

附图说明

23.【图1】图1是用来说明本发明第1实施方式的线圈部件1的结构的大致透视立体图,(a)是从上表面侧观察的图,(b)是从安装面侧观察的图。

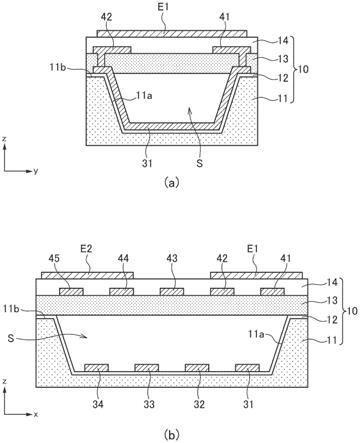

24.【图2】图2(a)是沿着图1(b)所示的a-a线的大致截面图,图2(b)是沿着图1(b)所示的b-b线的大致截面图。

25.【图3】图3是用来说明埋入素体10的线圈图案c的结构的大致立体图。

26.【图4】图4是示出从z方向观察线圈图案c的状态的大致透视俯视图。

27.【图5】图5是用来说明线圈部件1的制造方法的工序图。

28.【图6】图6是用来说明线圈部件1的制造方法的工序图。

29.【图7】图7是用来说明线圈部件1的制造方法的工序图。

30.【图8】图8是用来说明线圈部件1的制造方法的工序图。

31.【图9】图9是用来说明线圈部件1的制造方法的工序图。

32.【图10】图10是用来说明本发明的第2实施方式的线圈部件2的结构的大致截面图。

33.符号说明

34.1、2 线圈部件

35.10 素体

36.11 支撑体

37.11a 腔室的内壁

38.11b 外周面

39.12~14 绝缘层

40.31~34 第1区间

41.31a~34a 第1区间的一端

42.31b~34b 第1区间的另一端

43.41~45 第2区间

44.41a~44a 第2区间的一端

45.42b~45b 第2区间的另一端

46.51a~54a,51b~54b 开口部

47.71、72 通孔导体

48.71a、72a 开口部

49.c 线圈图案

50.e1、e2 端子电极

51.s 空洞

具体实施方式

52.以下,参照附图对本发明的优选实施方式进行详细的说明。

53.《第1实施方式》

54.图1是用来说明本发明第1实施方式的线圈部件1的结构的大致透视立体图,(a)是从上表面侧观察的图,(b)是从安装面侧观察的图。另外,图2(a)是沿着图1(b)所示的a-a线的大致截面图,图2(b)是沿着图1(b)所示的b-b线的大致截面图。

55.第1实施方式的线圈部件1是能够进行表面安装的芯片型电子部件,如图1及图2所示,具备:素体10、埋入素体10的线圈图案c、以及设置于素体10的表面的端子电极e1、e2。

56.素体10由支撑体11和绝缘层12~14构成。支撑体11由硅等具有足够的机械强度的材料构成,在其xy平面设置有以z方向为深度方向的腔室。支撑体11的表面具有:腔室的内壁11a和包围腔室的外周面11b。腔室的内壁11a具有:构成xy平面的底面以及位于底面和外周面11b之间的锥面。锥面是随着x方向位置或y方向位置变化而使深度线性变化的区域,通过设置这样的锥面,容易形成后述的线圈图案c的第1区间。另一方面,外周面11b是环状,并且构成xy平面。

57.绝缘层12是覆盖腔室的内壁11a以及外周面11b的薄膜,例如由氧化硅构成。在本发明中并非必须设置绝缘层12,但是在使用硅等导电材料作为支撑体11的材料的情况下,需要绝缘层12对支撑体11和线圈图案c进行绝缘。

58.绝缘层13由粘贴于支撑体11的外周面11b以覆盖腔室的树脂类绝缘材料构成。绝缘层13不与腔室的内壁11a接触,由此,通过支撑体11和绝缘层13在素体10的内部形成空洞

s。空洞s被空气充满,因此,空洞s的相对介电常数ε大约为1。空洞s也可以被氮气等惰性气体充满。由此,能够抑制在空洞s露出的线圈图案c的氧化。另外,绝缘层14层叠于绝缘层13的表面。在此,绝缘层13由在环氧类或丙烯酸类树脂材料中添加二氧化硅等填料(filler)的树脂类绝缘材料构成。与此相对地,绝缘层14由双马来酰亚胺和液晶聚合物等不含填料的树脂材料构成。

59.如上所述,绝缘层13由强度高且具有柔软性的树脂类绝缘材料构成,因此,即使通过在支撑体11的外周面11b粘贴绝缘层13来形成空洞s,也不容易产生因外力而导致绝缘层13的破损。另一方面,构成绝缘层14的树脂类绝缘材料由相对介电常数低的树脂材料构成,并且没有添加二氧化硅等填料,因此,相比于构成绝缘层13的树脂类绝缘材料相对介电常数低。作为一例,构成绝缘层13的树脂类绝缘材料的在1ghz的相对介电常数ε约为3.3,构成绝缘层14的树脂类绝缘材料的在1ghz的相对介电常数ε约为2.4。

60.图3是用来说明埋入素体10的线圈图案c的结构的大致立体图。另外,图4是示出从z方向观察线圈图案c的状态的大致透视俯视图。

61.如图2~图4所示,线圈图案c由经由绝缘层12而配置在支撑体11上的第1区间31~34、以及配置在绝缘层13上的第2区间41~45构成。并且,第1区间31~34的一端31a~34a分别与第2区间41~44的一端41a~44a连接,第1区间31~34的另一端31b~34b分别与第2区间42~45的另一端42b~45b连接。如图2所示,第1区间31~34中的、形成于腔室的内壁11a的部分在空洞s露出,第2区间41~45埋入绝缘层14。在此,空洞s的相对介电常数ε约为1,因此,在x方向上相邻的第1区间31~34之间的杂散电容被大幅降低。而且,对于第2区间41~45,由于埋入相对介电常数低的绝缘层14,因此,在x方向上相邻的第2区间41~45之间的杂散电容也被降低。

62.根据上述这种结构,构成跨多匝呈螺旋状卷绕的线圈图案c。线圈图案c的线圈轴是x方向。第2区间41的另一端41b构成线圈图案c的一端,并且经由贯通绝缘层14而设置的通孔导体71与端子电极e1连接。另一方面,第2区间45的一端45a构成线圈图案c的另一端,并且经由贯通绝缘层14而设置的通孔导体72与端子电极e2连接。端子电极e1、e2是仅形成于素体10的xy表面的底面端子。即,端子电极e1、e2未覆盖素体10的yz表面,由此,在使用焊料而安装于电路基板的情况下,素体10的yz表面不会被焊料的圆角(fillet)覆盖。由此,能够提高安装密度,并且由线圈图案c产生的磁通难以与端子电极e1、e2和焊料干扰,因此能够抑制涡电流的产生。

63.如图4所示,端子电极e1至少与第2区间41具有重叠,端子电极e2至少与第2区间45具有重叠。因此,在端子电极e1和第2区间41之间以及端子电极e2和第2区间45之间产生杂散电容。但是,在本实施方式中,由于位于两者之间的绝缘层14由相对介电常数低的树脂类绝缘材料构成,因此,能够降低端子电极e1、e2和第2区间41、45之间产生的杂散电容。而且,由于第2区间41~45埋入绝缘层14,因此,能够降低在x方向上相邻的第2区间41~45之间的杂散电容,即,在线圈图案c的相邻的匝间产生的杂散电容。由此,能够防止因杂散电容而引起的自谐振频率的降低。

64.另外,在本实施方式中,端子电极e1与第2区间42的一部分也具有重叠,端子电极e2与第2区间44的一部分也具有重叠。因此,在端子电极e1和第2区间42之间以及端子电极e2和第2区间44之间也产生杂散电容。在此,由于第2区间42距端子电极e1的配线距离比第2

区间41远,因此,受电压下降的影响,端子电极e1和第2区间42的每单位面积的杂散电容大于端子电极e1和第2区间41的每单位面积的杂散电容。同样地,由于第2区间44距端子电极e2的配线距离比第2区间45远,因此,受电压下降的影响,端子电极e2和第2区间44的每单位面积的杂散电容大于端子电极e2和第2区间45的每单位面积的杂散电容。如上所述,在端子电极e1、e2的各个与多个第2区间41~45具有重叠的情况下,将相对介电常数低的树脂类绝缘材料作为树脂层14的材料的效果更好。

65.如上所述,本实施方式的线圈部件1,由于第1区间31~34中的、形成于腔室的内壁11a的部分在空洞s露出,因此,能够大幅降低在x方向上相邻的第1区间31~34之间的杂散电容。另外,对于第2区间41~45,由于埋入相对介电常数低的绝缘层14,因此,在x方向上相邻的第2区间41~45之间的杂散电容也能够被降低。由此,能够大幅降低线圈图案c的相邻的匝间产生的杂散电容,并且能够提高自谐振频率。

66.而且,在本实施方式中,由于支撑体11由硅等强度高的材料构成,因此,能够确保素体10的机械强度,并且防止因杂散电容而引起的自谐振频率的降低。

67.另外,在本实施方式中,由于端子电极e1、e2在线圈图案c的轴向(x方向)上排列,因此,端子电极e1不与配线距离远的第2区间(例如第2区间44、45)重叠,同样地,端子电极e2不与配线距离远的第2区间(例如第2区间41、42)重叠。由此,由于抑制了端子电极e1、e2以及与其重叠的第2区间41、42、44、45的电位差,因此,与在y方向上排列端子电极e1、e2的情况相比,能够进一步降低杂散电容。

68.接下来,对本实施方式的线圈部件1的制造方法进行说明。

69.图5~图9是用来说明本实施方式的线圈部件1的制造方法的工序图。在图5~图9中,(a)是大致立体图,(b)是大致俯视图,(c)是yz大致截面图。

70.首先,如图5所示,准备由硅等构成的支撑体11,使用rie法等形成将z方向作为深度方向的腔室。由此,在与腔室对应的部分形成内壁11a,在腔室的周围形成环状的外周面11b。如果将硅用作支撑体11的材料,则能够高精度地形成腔室。此外,对于内壁11a的锥面的角度,能够通过rie条件来进行调整。

71.接下来,在内壁11a以及外周面11b形成由氧化硅等构成的绝缘层12之后,在绝缘层12的表面形成线圈图案c的第1区间31~34。第1区间31~34的大部分形成于覆盖腔室的内壁11a的位置,其两端形成于覆盖外周面11b的位置。作为第1区间31~34的形成方法,可以通过以下步骤来进行,即,将薄的供电膜形成于绝缘层12的整个面之后,使用喷涂法等涂布感光性抗蚀剂(resist),通过曝光显影在感光性抗蚀剂形成开口部,通过电镀使第1区间31~34在开口部生长。由此,形成沿y方向横穿腔室的连续的第1区间31~34。在此,由于腔室具有锥面,因此,在第1区间31~34难以产生断线或膜厚偏差等。

72.接下来,如图7所示,将薄膜状的绝缘层13经由绝缘层12粘贴在支撑体11的外周面11b上。由此,腔室被封闭,并且形成空洞s。上述工序也可以在氮气等惰性气体中进行。这样就能用氮气等惰性气体充满空洞s。另外,第1区间31~34中的、形成于外周面11b上的端部31a~34a、31b~34b埋入绝缘层13。接下来,通过对绝缘层13进行曝光显影,在绝缘层13形成开口部51a~54a、51b~54b。其中,开口部51a~54a分别设置于使第1区间31~34的一端31a~34a露出的位置,开口部51b~54b分别设置于使第1区间31~34的另一端31b~34b露出的位置。在此,绝缘层13由在强度较高的树脂材料中添加了填料的树脂类绝缘材料构成,

因此能够确保较高的加工性。

73.接下来,如图8所示,在绝缘层13的表面形成第2区间41~45。作为第2区间41~45的形成方法,可以通过以下步骤来进行,即,在整个面形成薄的供电膜之后,粘贴感光性膜,通过曝光显影在感光性膜形成开口部,通过电镀使第2区间41~45在开口部生长。此时,第2区间41~44的一端41a~44a设置在与开口部51a~54a重叠的位置,第2区间42~45的另一端42b~45b设置在与开口部51b~54b重叠的位置。由此,第1区间31~34的一端31a~34a分别与第2区间41~44的一端41a~44a连接,第1区间31~34的另一端31b~34b分别与第2区间42~45的另一端42b~45b连接。

74.接下来,如图9所示,在整个面形成绝缘层14以将第2区间41~45埋入。由此,在x方向上相邻的第2区间41~45通过相对介电常数低的树脂类绝缘材料绝缘。接下来,通过在绝缘层14形成开口部71a、72a,使第2区间41的另一端41b和第2区间45的一端45a露出。并且,通过在与开口部71a、72a重叠的位置分别形成端子电极e1、e2,完成本实施方式的线圈部件1。

75.如上所述,在本实施方式的线圈部件1的制造方法中,在支撑体11形成腔室,在腔室的内壁11a形成第1区间31~34之后,以封闭腔室的方式粘贴绝缘层13,因此,能够在素体10的内部形成空洞s。由此,能够将杂散电容少的线圈图案c埋入素体10。

76.《第2实施方式》

77.图10是用来说明本发明的第2实施方式的线圈部件2的结构的大致截面图。

78.如图10所示,第2实施方式的线圈部件2在绝缘层14由与绝缘层13相同的树脂类绝缘材料构成这一点上,与第1实施方式的线圈部件1不同。由于其他的基本结构与第1实施方式的线圈部件1相同,因此,对于相同的要素赋予相同的符号,并且省略重复的说明。如本实施方式的线圈部件2所例示,在本发明中,第2区间41~44被相对介电常数低的树脂类绝缘材料覆盖这一点并非必须。

79.以上,对本发明的优选实施方式进行了说明,但本发明并不限于上述的实施方式,在不脱离本发明主旨的范围内可以进行各种各样的变形,当然这些变形也包含在本发明的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1