半导体模块的制作方法

1.本发明涉及半导体模块。

背景技术:

2.以往,已知有利用导线将半导体芯片的主电极和电路电极连接的半导体模块(例如,参照专利文献1)。

3.专利文献1:日本特开2003-188378号公报

技术实现要素:

4.技术问题

5.在半导体模块中,优选提高可靠性。

6.技术方案

7.为了解决上述课题,在本发明的一个方式中,提供一种半导体模块。半导体模块可以具备主电路部。主电路部的半导体芯片可以沿着第一方向排列配置有多个。半导体芯片可以包括晶体管部和二极管部,且在上表面设置有栅极焊盘和主电极。半导体模块可以具备多个电路电极。多个电路电极可以与多个半导体芯片的主电极连接。半导体模块可以具备多个主端子。多个主端子可以与多个电路电极连接。半导体模块可以具备多个导线。多个导线可以将多个主电极与多个电路电极连接。在各个半导体芯片中,晶体管部和二极管部可以在第二方向上具有长边。在各个半导体芯片中,晶体管部和二极管部可以沿着与第二方向垂直的第三方向交替地配置。各个半导体芯片可以具有多个端边,该多个端边包括在俯视时与栅极焊盘的距离最近的栅极侧端边。各个栅极侧端边可以在俯视时朝向同一侧配置。多个主端子可以以在俯视时不夹着主电路部的方式相对于主电路部配置于同一侧。多个导线可以分别具有与主电极连接的接合部。各个接合部可在俯视时具有长边方向。接合部的长边方向可相对于第二方向具有角度。

8.应予说明,上述的发明内容并未列举本发明的全部特征。另外,这些特征组的子组合也能够成为发明。

附图说明

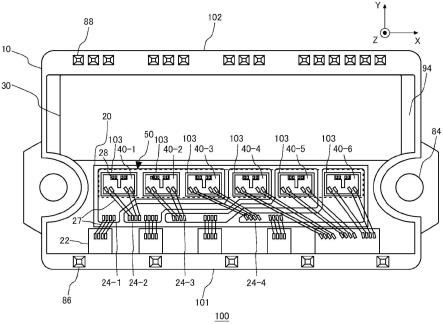

9.图1是示出本发明的一个实施方式的半导体模块100的一例的图。

10.图2是示出半导体芯片40中的接合部26和栅极接合部28的配置的一例的图。

11.图3是示出半导体芯片40中的接合部26和栅极接合部28的配置的另一例的图。

12.图4是示出半导体芯片40中的接合部26和栅极接合部28的配置的另一例的图。

13.图5是示出半导体芯片40中的接合部26和栅极接合部28的配置的另一例的图。

14.图6是示出半导体芯片40中的接合部26和栅极接合部28的配置的另一例的图。

15.图7是示出半导体芯片40中的接合部26和栅极接合部28的配置的另一例的图。

16.图8是示出半导体芯片140中的接合部26和栅极接合部28的配置的一例的图。

17.图9是对俯视时的接合部26的主要部分进行说明的图。

18.图10是对侧视时的接合部26的主要部分进行说明的图。

19.图11是示出俯视时的接合部26的形状的一例的图。

20.图12是示出俯视时的接合部26的形状的一例的图。

21.图13是示出俯视时的接合部26的形状的一例的图。

22.图14是示出比较例的半导体芯片240中的接合部26和栅极接合部28的配置的一例的图。

23.符号说明

24.10

…

树脂壳体、20

…

主电路绝缘基板、22

…

主端子电路部、24

…

电路电极、26

…

接合部、27

…

导线、28

…

栅极接合部、29

…

栅极导线、30

…

控制电路部、31

…

前端部、32

…

颈部、40

…

半导体芯片、48

…

栅极流道、50

…

主电路部、60

…

主电极、61

…

第一部分、62

…

第二部分、70

…

晶体管部、80

…

二极管部、84

…

贯通孔、86

…

主端子、88

…

控制端子、90

…

焊盘区、92

…

边缘终端结构部、94

…

空间、100

…

半导体模块、101

…

端边、102

…

端边、103

…

栅极侧端边、104

…

端边、105

…

角、106

…

角、107

…

长边方向、108

…

栅极长边方向、109

…

方向、110

…

方向、116

…

栅极焊盘、140

…

半导体芯片、240

…

半导体芯片。

具体实施方式

25.以下,通过发明的实施方式对本发明进行说明,但以下的实施方式并不限定权利要求书的发明。另外,实施方式中说明的特征的组合并不一定全部是发明的技术方案所必须的。应予说明,在本说明书和附图中,对实质上具有同一功能、同一构成的要素,通过标注同一符号而省略重复说明,另外,对于与本发明没有直接关系的要素省略图示。另外,在一个附图中,对具有同一功能、同一构成的要素代表性地标注符合,关于其他,有时省略符合。

26.在本说明书中,将与半导体芯片的深度方向平行的方向上的一侧称为“上”,将另一侧称为“下”。将基板、层或其他部件的两个主面中的一个面称为上表面,将另一个面称为下表面。“上”、“下”的方向并不限于重力方向或安装半导体模块时的方向。

27.在本说明书中,有时使用x轴、y轴和z轴的正交坐标轴来说明技术事项。正交坐标轴只不过确定构成要素的相对位置,并不限定特定的方向。例如,z轴并不限定地表示相对于地面的高度方向。应予说明,+z轴方向和-z轴方向是相互反向的方向。在不记载正负而记载为z轴方向的情况下,是指与+z轴和-z轴平行的方向。在本说明书中,将与半导体芯片的上表面和下表面平行的正交轴设为x轴和y轴。另外,将与半导体芯片的上表面和下表面垂直的轴设为z轴。在本说明书中,有时将z轴的方向称为深度方向。另外,在本说明书中,包括x轴和y轴在内,有时将与半导体芯片的上表面和下表面平行的方向称为水平方向。

28.在本说明书中,在称作“相同”或“相等”的情况下,也可以包括具有由制造偏差等引起的误差的情况。该误差例如为10%以内。另外,在角度的差异为5度以内的情况下,设为角度相同。

29.图1是示出本发明的一个实施方式的半导体模块100的一例的图。半导体模块100可以作为逆变器或转换器等电力变换装置而发挥功能。半导体模块100具备树脂壳体10、主电路绝缘基板20、多个主端子电路部22、多个电路电极24、多个导线27、控制电路部30、主电路部50、多个主端子86、多个控制端子88。主电路部50是图1中的虚线所示的区域。在本说明

书中,将设置主电路绝缘基板20的面中的正交轴设为x轴和y轴,将与xy面垂直的轴设为z轴。在图1中,示出xy面中的各部件的配置例。

30.在本例的半导体模块100中,在主电路绝缘基板20上配置多个电路电极24和主电路部50。在图1的例子中,在主电路绝缘基板20的上表面配置有电路电极24-1、电路电极24-2、电路电极24-3和电路电极24-4。电路电极24可以通过将铜板或铝板、或者对这些材料实施了镀覆而得的板直接接合或经由钎料层接合于氧化铝陶瓷、氮化硅陶瓷、氮化铝陶瓷等主电路绝缘基板20而构成。主电路绝缘基板20也可以在所述陶瓷中添加有氧化锆、氧化钇等。另外,电路电极24也可以是包含铜或铝中的至少任一方的合金。应予说明,主电路绝缘基板20和电路电极24也可以是在铜板、铝板等导电部件贴合绝缘片而成的。也就是说,主电路绝缘基板20和电路电极24可以是导电部件与绝缘部件成为一体的板状部件。

31.在主电路部50中,多个半导体芯片40沿着第一方向排列而配置。在本例中,第一方向是指x轴方向。在图1中,半导体芯片40-1、半导体芯片40-2、半导体芯片40-3、半导体芯片40-4、半导体芯片40-5和半导体芯片40-6沿着x轴方向排列而配置。半导体芯片40配置于电路电极24的上表面。在本例中,半导体芯片40-1、半导体芯片40-2和半导体芯片40-3配置于电路电极24-1的上表面。另外,半导体芯片40-4配置于电路电极24-2的上表面。半导体芯片40-5配置于电路电极24-3的上表面。半导体芯片40-6配置于电路电极24-4的上表面。在半导体芯片40配置于电路电极24的上表面的情况下,半导体芯片40的背面电极(未图示)可以与电路电极24的上表面连接。作为一例,半导体芯片40的背面电极是集电极。在本例中,半导体芯片40是将绝缘栅双极型晶体管(igbt)、fwd(free wheel diode,续流二极管)等二极管组合而成的rc(reverse conducting,反向导通)-igbt。

32.控制电路部30经由栅极导线29(参照图2)与半导体芯片40的栅极焊盘116(参照图2)连接。控制电路部30通过控制施加到半导体芯片40的栅极焊盘116的电压来控制半导体芯片40。控制电路部30经由控制端子88与外部电极连接。应予说明,在图1中,省略了控制电路部30的电路结构。

33.多个主端子电路部22经由电路电极24和导线27与多个半导体芯片40的主电极60(参照图2)或背面电极连接。多个主端子86可以与多个电路电极24连接。多个电路电极24可以与多个半导体芯片40的主电极60连接。多个主端子86可以与多个半导体芯片40的主电极60或背面电极连接。主端子电路部22可以经由主端子86与外部电极连接。通过主端子电路部22与半导体芯片40的主电极60或者背面电极连接,能够在半导体模块100中控制流过主端子86的电流。

34.另外,多个主端子86可以以在俯视时不夹着主电路部50的方式相对于主电路部50配置于同一侧。多个控制端子88可以以在俯视时不夹着主电路部50的方式相对于主电路部50配置于同一侧。在本例中,多个主端子86沿着树脂壳体10的端边101设置,多个控制端子88沿着树脂壳体10的端边102设置。将相对于主电路部50在俯视时配置有多个主端子86的一侧设为主端子侧。另外,将相对于主电路部50在俯视时配置有多个控制端子88的一侧设为控制端子侧。

35.导线27将半导体芯片40的主电极60与电路电极24连接。在本例中,多个导线27将多个半导体芯片40的主电极60与多个电路电极24连接。另外,导线27将电路电极24与主端子电路部22连接。在本例中,多个导线27从主电极60向主端子侧延伸。栅极导线29将半导体

芯片40的栅极焊盘116与控制电路部30连接。在本例中,栅极导线29从主电极60向控制端子侧延伸。即,栅极导线29从主电极60向与主端子侧相反的一侧延伸。应予说明,在图1中,仅记载了栅极导线29中的与栅极焊盘116接触的栅极接合部28。作为一例,导线27和栅极导线29是铝导线。

36.树脂壳体10设置为包围主电路绝缘基板20、主端子电路部22和空间94,所述空间94收纳控制电路部30。半导体芯片40由树脂壳体10、填充于树脂壳体10的密封树脂(未图示)这样的树脂封装。

37.多个主端子86可以设置为从树脂壳体10突出。多个控制端子88可以设置为从树脂壳体10突出。另外,也可以在树脂壳体10设置贯通孔84,所述贯通孔84供固定冷却部等的螺钉等紧固部件插入。

38.在本例中,树脂壳体10由能够通过注塑成型而形成的热固化型树脂、或者能够通过uv成型而形成的紫外线固化型树脂等树脂成型。该树脂例如可以包含选自聚苯硫醚(pps)树脂、聚对苯二甲酸丁二醇酯(pbt)树脂、聚酰胺(pa)树脂、丙烯腈丁二烯苯乙烯(abs)树脂和丙烯酸树脂等中的一种或多种高分子材料。

39.图2是示出半导体芯片40中的接合部26和栅极接合部28的配置的一例的图。在图2中,将导线27中的与半导体芯片40接触的部分表示为接合部26。另外,在图2中,将栅极导线29中的与半导体芯片40接触的部分表示为栅极接合部28。半导体芯片40-1、半导体芯片40-2、半导体芯片40-3、半导体芯片40-4、半导体芯片40-5和半导体芯片40-6中的至少一个可以具有图2的半导体芯片40的结构。半导体芯片40-1、半导体芯片40-2、半导体芯片40-3、半导体芯片40-4、半导体芯片40-5和半导体芯片40-6均可以具有图2的半导体芯片40的结构。

40.在图2中,半导体芯片40具有栅极流道48、主电极60、焊盘区90和边缘终端结构部92。即,在半导体芯片40中,栅极流道48、主电极60、焊盘区90和边缘终端结构部92设置于上表面。在图2中,主电极60是由栅极流道48包围的区域中的非焊盘区90的区域。作为一例,主电极60是发射极。另外,主电极60具有第一部分61和两个第二部分62。第一部分61在俯视时与焊盘区90对置。在本例中,将主电极60的在y轴方向上与焊盘区90面对的部分设为第一部分61。两个第二部分62在俯视时不与焊盘区90对置,而是在俯视时夹着第一部分61。在图2中,用虚线表示第一部分61与第二部分62之间的边界。

41.半导体芯片40包括晶体管部70和二极管部80。晶体管部70和二极管部80设置于设置主电极60的区域。晶体管部70和二极管部80在第二方向上具有长边。在本例中,第二方向是指y轴方向。晶体管部70和二极管部80可以沿着与第二方向垂直的第三方向交替地配置。在本例中,第三方向是指x轴方向。第三方向可以是与第一方向相同的方向。第三方向也可以是与第一方向不同的方向。在图2中,晶体管部70设置得比二极管部80多。在图2中,晶体管部70设置有5个,二极管部80设置有4个。在图2中,在设置主电极60的区域的x轴方向的端部设置晶体管部70。

42.另外,将晶体管部70的最小宽度设为l1,将二极管部80的最小宽度设为l2。在图2中,5个晶体管部70中的设置于中央的晶体管部70以外的晶体管部70的宽度为l1。另外,4个二极管部80的宽度为l2。

43.焊盘区90可以设置有多个电极焊盘。在本例中,在焊盘区90设置有4个电极焊盘。在焊盘区90可以设置有一个栅极焊盘116。除了栅极焊盘116之外的电极焊盘例如是温度测

量用焊盘或电流测量用焊盘。焊盘区90可以配置于半导体芯片40的x轴方向上的中央侧。

44.半导体芯片40在俯视时可以具有多个端边。半导体芯片40可以具有在俯视时与栅极焊盘116之间的距离为最近的栅极侧端边103。将与栅极侧端边103相反侧的端边设为端边104。在图1中,各个半导体芯片40的栅极侧端边103可以在俯视时朝向同一侧而配置。即,各个半导体芯片40的栅极焊盘116可以配置于同一侧。在图1中,栅极焊盘116配置于控制电路部30侧。另外,栅极侧端边103朝向控制端子侧配置。即,栅极侧端边103朝向与主端子侧相反的一侧配置。

45.栅极流道48与栅极焊盘116电连接,包围主电极60和焊盘区90。在图2中,用粗线记载栅极流道48。栅极流道48与设置在晶体管部70的栅极沟槽内的多晶硅等导电部电连接。栅极流道48由多晶硅等导电材料形成。

46.半导体芯片40可以具有包围主电极60、焊盘区90和栅极流道48的边缘终端结构部92。边缘终端结构部缓和半导体芯片40的上表面侧的电场集中。边缘终端结构部例如具有保护环、场板、降低表面电场以及将它们组合而成的结构。

47.在图2中,导线27分别具有与主电极60连接的接合部26。主电极60与多个接合部26连接。在本例中,配置有四个接合部26。接合部26可以具有长边。在图2中,在接合部26上用箭头记载接合部26的长边方向107。接合部26通过引线键合来配置。接合部26可以配置于与栅极侧端边103相反的一侧的端边104侧。通过将接合部26配置于端边104侧,能够防止与栅极导线29干扰。

48.在晶体管部70工作时,晶体管部70发热。因此,在接合部26中发生温度上升。由于温度上升,半导体模块100的可靠性降低。因此,为了抑制温度上升,接合部26优选配置于晶体管部70和二极管部80这双方。

49.为了将接合部26配置于晶体管部70和二极管部80这双方,考虑减小晶体管部70的宽度和二极管部80的宽度。如果减小晶体管部70的宽度和二极管部80的宽度,则有时半导体芯片40的特性会发生变化。另外,虽然考虑增大接合部26的宽度,但半导体模块100会大型化。另外,也考虑相对于晶体管部70和二极管部80的长边方向垂直地配置接合部26的长边,但导线27的方向会受到限制。

50.在本例中,接合部26的长边方向107相对于第二方向具有角度。即,接合部26的长边方向107相对于y轴方向具有角度。接合部26的长边方向107与y轴方向之间所成的角度可以不是0度。即,接合部26的长边方向107与y轴方向可以不平行。接合部26的长边方向107与y轴方向之间所成的角度可以不是90度。即,接合部26的长边方向107与y轴方向可以不垂直。接合部26的长边方向107与y轴方向之间所成的角度可为10度以上。接合部26的长边方向107与y轴方向之间所成的角度可为20度以上。接合部26的长边方向107与y轴方向之间所成的角度可为80度以下。接合部26的长边方向107与y轴方向之间所成的角度可为70度以下。

51.接合部26的长边方向107相对于第二方向具有角度,因此容易将接合部26配置于晶体管部70和二极管部80这双方。即,接合部26在俯视时可以与晶体管部70的至少一部分以及二极管部80的至少一部分重叠。因此,能够抑制接合部26中的温度上升,防止半导体模块100的可靠性的降低。另外,能够不使晶体管部70的宽度、二极管部80或接合部26的宽度变化,便防止半导体模块100的可靠性的降低。导线27的方向不受限制,便能够防止半导体

模块100的可靠性的降低。

52.在图1的各个半导体芯片40中,接合部26的长边方向107与y轴方向之间所成的角度可以相同。例如,在配置于半导体芯片40-1的4个接合部26中,接合部26的长边方向107与y轴方向之间所成的角度相同。通过设置成这种结构,可在半导体芯片40内以相同的接合设定配置多个接合部26,从而可在短时间内配置多个接合部26。另外,在这种情况下,在图1中的各半导体芯片40间,接合部26的长边方向107与y轴方向之间所成的角度可以不同,也可以相同。

53.接合部26的至少一部分在第三方向上的位置与半导体芯片40中相邻的另一接合部26的至少一部分在第三方向上的位置可以相同。即,接合部26的至少一部分与相邻的另一接合部26的至少一部分可在第三方向上重叠。在本例中,角105在第三方向上的位置与角106在第三方向上的位置相同,所述角105为接合部26的长边方向107的栅极侧端边103侧的端部的角,所述角106为半导体芯片40中的相邻的另一接合部26的长边方向107的端边104侧的端部的角。通过设为这样的结构,能够减少未设置接合部26的晶体管部70或二极管部80,能够防止电流的集中,防止半导体模块100的可靠性的降低。

54.在图2中,栅极导线29具有与栅极焊盘116连接的栅极接合部28。栅极焊盘116与栅极接合部28连接。在本例中,配置有一个栅极接合部28。栅极接合部28通过引线键合来配置。栅极接合部28可以具有长边。在图2中,在栅极接合部28上用箭头记载栅极接合部28的栅极长边方向108。

55.在本例中,栅极接合部28的栅极长边方向108相对于接合部26的长边方向107具有角度。在图2中,栅极接合部28的栅极长边方向108是指y轴方向。即,栅极接合部28的栅极长边方向108可以与第二方向平行。通过设为这样的结构,能够易于配置栅极导线29。

56.图3是示出半导体芯片40中的接合部26和栅极接合部28的配置的另一例的图。图3的半导体芯片40的接合部26的配置与图2的半导体芯片40的接合部26的配置不同。图3的除此以外的结构可以与图2相同。在图3中,将接合部26与晶体管部70重叠的区域设为区域a,将接合部26与二极管部80重叠的区域设为区域b。在图3中,用不同方向的阴影表示区域a和区域b。

57.优选在多个接合部26之间,区域a的面积与区域b的面积的比率相同。区域a的面积与区域b的面积的比率相同是指,即使存在接合部26的面积的

±

10%的偏差,也可以认为相同。在本例中,在四个接合部26之间,区域a的面积与区域b的面积的比率全部相同。通过使接合部26与晶体管部70重叠的区域的面积和接合部26与二极管部80重叠的区域的面积的比率在多个接合部26之间相同,从而易于使相等的电流流过与接合部26分别连接的导线27,能够抑制导线27过度发热。

58.在第一部分61可以形成晶体管部70。另外,将主电极60的中央的晶体管部70设为晶体管部70-1。在晶体管部70-1可以不形成接合部26。晶体管部70-1在本例中也是指第一部分61的中央的晶体管部70。通过存在晶体管部70-1,来自栅极焊盘116的栅极电流迅速地流到晶体管部70-1,能够将周围的晶体管部70也包括在内进行快速的开关。另外,通过在晶体管部70-1不直接连接导线27,能够防止半导体芯片40的中央侧的过度的电流集中。另一方面,优选在晶体管部70-1以外的晶体管部70形成接合部26。另外,优选在全部二极管部80形成接合部26。

59.俯视时配置于第一部分61的接合部26的密度可以小于俯视时配置于第二部分62的接合部的密度。即,配置于半导体芯片40的中央侧的接合部26的密度可以小于配置于半导体芯片40的外侧的接合部26的密度。半导体芯片40的中央侧与半导体芯片40的外侧相比,电流容易集中,温度容易上升。因此,通过避开温度容易上升的半导体芯片40的中央侧来配置接合部26,能够进一步防止半导体模块100的可靠性的降低。

60.图4是示出半导体芯片40中的接合部26和栅极接合部28的配置的另一例的图。图4的半导体芯片40的接合部26的配置与图2的半导体芯片40的接合部26的配置不同。图4的除此以外的结构可以与图2相同。

61.在本例中,接合部26以通过半导体芯片40的第三方向上的中心的中心线l为基准而线对称地配置。通过设为这样的结构,能够改变导线27的方向,能够使半导体模块100小型化。

62.图5是表示半导体芯片40中的接合部26和栅极接合部28的配置的另一例的图。图5的半导体芯片40的接合部26的配置与图2的半导体芯片40的接合部26的配置不同。图5的除此以外的结构可以与图2相同。

63.在本例中,与图2相比,接合部26与相邻的另一接合部26重叠的区域较大。即,角105的第三方向上的位置与角106的第三方向上的位置可以不同,所述角105为接合部26的长边方向107上的栅极侧端边103侧的端部的角,所述角106为半导体芯片40中相邻的另一接合部26的长边方向107上的端边104侧的端部的角。即使是这样的结构,也能够防止半导体模块100的可靠性的降低。

64.图6是示出半导体芯片40中的接合部26和栅极接合部28的配置的另一例的图。图6的半导体芯片40的接合部26的配置与图2的半导体芯片40的接合部26的配置不同。图6的除此以外的结构可以与图2相同。

65.在本例中,在至少一个接合部26中,俯视时该接合部26与晶体管部70重叠的面积大于俯视时该接合部26与二极管部80重叠的面积。在图6中,在4个接合部26中,俯视时接合部26与晶体管部70重叠的面积大于俯视时接合部26与二极管部80重叠的面积。优选接合部26与晶体管部70重叠的面积大于接合部26的50%且为接合部26的80%以下。在半导体模块100作为逆变器进行工作的情况下,与二极管部80相比,在晶体管部70容易流通大量的电流。因此,通过增大接合部26与晶体管部70重叠的面积,能够抑制接合部26的温度上升,能够防止半导体模块100的可靠性的降低。

66.图7是表示半导体芯片40中的接合部26和栅极接合部28的配置的另一例的图。图7的半导体芯片40的接合部26的配置与图2的半导体芯片40的接合部26的配置不同。图7的除此以外的结构可以与图2相同。

67.在本例中,在至少一个接合部26中,俯视时该接合部26与二极管部80重叠的面积大于俯视时该接合部26与晶体管部70重叠的面积。在图7中,在4个接合部26中,俯视时接合部26与二极管部80重叠的面积大于俯视时接合部26与晶体管部70重叠的面积。优选接合部26与二极管部80重叠的面积大于接合部26的50%且为接合部26的80%以下。在半导体模块100作为转换器进行工作的情况下,与晶体管部70相比,在二极管部80容易流通大量的电流。因此,通过增大接合部26与二极管部80重叠的面积,能够抑制接合部26的温度上升,能够防止半导体模块100的可靠性的降低。

68.图8是示出半导体芯片140中的接合部26和栅极接合部28的配置的一例的图。图8的半导体芯片140的晶体管部70、二极管部80和接合部26的配置与图2的半导体芯片40的晶体管部70、二极管部80和接合部26的配置不同。图8的除此以外的结构可以与图2相同。

69.在图8的半导体芯片140中,晶体管部70设置有7个,二极管部80设置有6个。将x轴方向上的晶体管部70的最小宽度设为l3,将二极管部80的最小宽度设为l4。晶体管部70的宽度和二极管部80的宽度可以在y轴上配置接合部26的位置测定。在图8的半导体芯片140中,7个晶体管部70中的除了设置于中央的晶体管部70以外的晶体管部70的宽度为l3。另外,6个二极管部80的宽度为l4。l3可以小于l1。l4可以小于l2。

70.图8的半导体芯片140的接合部26的长边方向107与第二方向之间所成的角度可以小于图2的半导体芯片40中的接合部26的长边方向107与第二方向之间所成的角度。在图8的半导体芯片140中,设置于中央的晶体管部70以外的晶体管部70的宽度是l3,二极管部80的宽度是l4。因此,即使减小接合部26的长边方向107与第二方向之间所成的角度,也能够将接合部26配置于晶体管部70和二极管部80这双方。另外,通过减小角度,能够容易地实施引线键合。

71.在主电路部50可以配置晶体管部70的最小宽度或二极管部80的最小宽度不同的多个半导体芯片。例如,在图1中,半导体芯片40-1、半导体芯片40-2和半导体芯片40-3可以具有图8的半导体芯片140的结构,半导体芯片40-4、半导体芯片40-5和半导体芯片40-6可以具有图2的半导体芯片40的结构。在这种情况下,接合部26的长边方向107与第二方向之间所成的角度可以基于晶体管部70的最小宽度或二极管部80的最小宽度而变化。即,半导体芯片40-1、半导体芯片40-2和半导体芯片40-3中的接合部26的长边方向107与第二方向之间所成的角度可以小于半导体芯片40-4、半导体芯片40-5和半导体芯片40-6中的接合部26的长边方向107与第二方向之间所成的角度。由于基于晶体管部70或二极管部80的宽度而使接合部26的长边方向107与第二方向之间所成的角度变化,因此能够防止导线27的方向被限制,并且能够防止半导体模块100的可靠性的降低。

72.图9是对俯视时的接合部26的主要部分进行说明的图。在图9中,导线27具有接合部26、前端部31和颈部32。将导线27的延伸方向设为方向110。

73.前端部31是导线27的一个端部。另外,颈部32在与前端部31相反的一侧与接合部26连接。接合部26经由从颈部32延伸的导线与电路电极24电连接。

74.接合部26的长边方向107是与将前端部31和颈部32连接的方向即方向109相同的方向。即,俯视时接合部26的长边方向107与方向109所成的角度可为5度以内。

75.图10是对侧视时的接合部26的主要部分进行说明的图。在图10中,接合部26与主电极60连接。

76.作为一例,导线27与主电极60的连接通过超声波接合来进行。具体而言,利用键合工具将处于导线27的延伸方向上的接合部26的上表面向主电极60按压,并施加超声波,由此进行接合。因此,俯视时的接合部26的长边方向107与俯视时的导线27的延伸方向即方向110相同。即,俯视时接合部26的长边方向107与方向110所成的角度可以为5度以内。而且,当利用键合工具将处于导线27的延伸方向上的接合部26的上表面向主电极60按压时,可使导线27的上表面咬入键合工具前端的槽中,使接合部26朝预定的方向旋转。由此,可使接合部26的长边方向107相对于作为延伸方向的方向110错开预定的角度。在这种情况下,俯视

时接合部26的长边方向107与方向110所成的角度可以为30度以内。

77.图11、图12、图13是示出俯视时的接合部26的形状的一例的图。俯视时的接合部26的形状并不限定于图2等的矩形形状。俯视时的接合部26的形状可以是在角部具有圆度的矩形形状(图11)。俯视时的接合部26的形状可以是长圆形状(图12)。俯视时的接合部26的形状可以是椭圆形状(图13)。

78.图14是表示比较例的半导体芯片240中的接合部26和栅极接合部28的配置的一例的图。在图14的半导体芯片240中,导线27的接合部26的长边方向107相对于y轴方向平行。在这种情况下,如图14那样,存在接合部26仅配置于晶体管部70的情况。如果仅配置于晶体管部70,则在晶体管部70工作时,接合部26的温度上升,半导体模块100的可靠性降低。

79.以上,使用实施方式对本发明进行了说明,但本发明的技术范围并不限于上述实施方式所记载的范围。能够对上述实施方式施加各种变更或改良,这对于本领域技术人员而言是显而易见的。根据权利要求书的记载可知,施加了这样的变更或改良的方式也能够包含在本发明的技术范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1