压电复合基底及其制造方法与流程

for saw-duplexer used in rf front end of smartphone.”[在线],2012年11月8日,dempa shimbun high technology,3月20日检索,平成27年,互联网《url:http://www.yuden.co.jp/jp/product/tech/column/20121108.html》非专利文献3:a tauzin等人,“3-inch single-crystal litao3 films onto metallic electrode using smart cuttm technology”,electric letters,19th june 2008,vol.4 4,no.13,p.822非专利文献4:weill liu等人,“fabrication of single-crystalline litao3film on silicon substrate using thin film transfer technology”,j.vac.sci.technol.b26(1),jan/feb 2008,p.206

技术实现要素:

本发明要解决的问题

[0010]

在非专利文献1或非专利文献2中描述的包括研磨的复合基底的制造方法具有以下问题:随着压电基底的变薄而发生膜厚均匀性的劣化。

[0011]

在非专利文献3中报道了在lt晶圆与薄膜之间具有金属层和sio2基底的结构使得能够抑制由于热处理期间的热膨胀差异而导致的晶圆的剥落或破裂,并且从而转移lt薄膜。然而,该方法不能克服上述压电材料在温度稳定性方面的问题,因为底层基底和薄膜由相同的材料即lt制成。此外,在不进行200℃或更高的热处理的情况下,薄膜不能被转移。此外,复合基底具有夹在其中的金属层,从而限制了其使用。此外,为了抑制晶圆的破裂,昂贵的lt的使用量应该大于必需的量,而这增加了制造成本。

[0012]

非专利文献4描述了在200℃至800℃下进行热处理。然而,在具体实例中,通过智能切割方法将lt薄膜转移在硅晶圆上仅在200℃下进行,并且在该实例中,没有关于lt薄膜是否转移到硅晶圆的整个表面上的描述。

[0013]

本发明人通过使用与非专利文献3类似的方法在200℃下通过热处理进行剥离的验证实验。该薄膜没有转移到硅晶圆的整个表面上,并且仅在其小部分中观察到转移。特别地,lt薄膜根本不在硅晶圆的外围部分上转移,这被认为是由于在热处理期间晶圆之间的热膨胀差异以及在硅晶圆的外围部分处从lt晶圆的层压界面发生的剥离而使待层压的晶圆翘曲而发生的。假定即使在200℃或更高的温度下进行热处理,由于它们之间的热膨胀差异而导致的待层压的晶圆的翘曲也不能被抑制,并且如上所述,lt薄膜不能稳定地转移到硅晶圆的整个表面上。包括离子注入处理的复合基底的制造方法具有这样的问题,即如上所述,热处理是必要的,尽管可以形成具有优异的膜厚均匀性的薄膜。

[0014]

为了形成具有改进的温度性能的基底,本发明人试图在具有比蓝宝石或硅的线性膨胀系数小的线性膨胀系数的石英基底(表1)上形成lt膜。然而,发现由于基底之间的膨胀系数的非常大的差异,复合基底的变形量即使在低至100℃或更低的温度下也是大的,并且基底在热处理之后保持变形或断裂,从而不应用研磨工艺。尝试通过离子注入来剥离,但由于低热处理温度仅在lt-石英界面处发生分离。

[0015]

如专利文献2中所描述的使用粘合剂的方法还具有以下问题:在lt基底和石英基底的复合基底中,通过在100℃或更低的温度下的热处理不能实现足够的粘合强度,这既不引起基底的断裂也不引起基底的分离,并且通过研磨或离子注入难以形成lt膜。

[0016]

考虑到上述问题,本发明的目的因此是提供一种压电复合基底及其制造方法,由此,即使在100℃或更低的热处理温度下,也可以通过离子注入来实现足以在具有显著小的线性膨胀系数的绝缘基底如石英基底上形成压电层如lt膜或ln膜的粘合强度。用于解决该问题的手段

[0017]

为了实现上述目的,作为本发明的一个方面,提供了一种压电复合基底,其具有连续堆叠的绝缘基底、中间层和压电层,其中所述压电层在堆叠方向上具有100nm至2,000nm的厚度,所述绝缘基底具有2英寸至12英寸的直径和100μm至2,000μm的厚度。绝缘基底的线性膨胀系数小于压电层的线性膨胀系数,并且它们之间的差为14

×

10-6

/k到16

×

10-6

/k,并且绝缘基底和中间层各自具有含si的无定形材料。

[0018]

压电层可以包含钽酸锂或铌酸锂。绝缘基底可以是石英基底。中间层可以含有无定形硅或二氧化硅。

[0019]

作为本发明的另一方面,提供了具有连续堆叠的绝缘基底、中间层和压电层的压电复合基底的制造方法,该方法包括:制备压电单晶基底和绝缘基底的步骤,所述绝缘基底的线性膨胀系数小于所述压电单晶基底的线性膨胀系数,它们之间的差为14

×

10-6

/k至16

×

10-6

/k,并且具有含si的无定形材料;所述压电单晶基底的表面经历离子注入处理以在所述压电单晶基底中形成离子注入层的步骤;在所述绝缘基底和所述压电单晶基底的各自待层压的表面中的一个或两个表面上形成具有含si的无定形材料的中间层的步骤;将所述绝缘基底的待层压表面与所述压电单晶基底的待层压表面经由所述中间层进行层压以得到粘合体的步骤;热处理所述粘合体的步骤;以及将所述离子注入层作为压电层留下并且将所述压电单晶基底的剩余部分从经所述热处理的所述粘合体剥离的步骤。

[0020]

在形成中间层的步骤中,含si的无定形材料可以包含无定形硅或二氧化硅,并且中间层可以通过cvd、溅射或旋涂形成。发明效果

[0021]

根据本发明,即使使用线性膨胀系数显著小于压电层的线性膨胀系数(它们之间的差为14

×

10-6

/k至16

×

10-6

/k)且由含si的无定形材料制成的绝缘基底,在压电层与绝缘基底之间形成具有含si的无定形材料的中间层也能够实现即使在100℃或更低的热处理温度下也足以通过离子注入形成压电层的粘合强度。

附图说明

[0022]

图1是用于解释根据本发明的压电复合基底的制造方法的一个实施方案的示意性流程图。图2是用于解释在比较例2中测量的粘合基底的变形量的示意图。

具体实施方式

[0023]

下面将参考附图描述根据本发明的压电复合基底及其制造方法的一个实施方案,但是本发明的范围不局限于此或由其所限定。

[0024]

如图1所示,本实施方案的压电复合基底的制造方法包括:制备压电单晶基底1的步骤(图1中的(a)),使压电单晶基底1经历离子注入处理的步骤(图1中的(b)),由此在压电单晶基底1中形成离子注入层1a的步骤(图1中的(c)),制备绝缘基底2的步骤(图1中的

(d)),在压电单晶基底1和绝缘基底2上形成中间层3的步骤(图1中的(e)),经由中间层3将压电单晶基底1与绝缘基底2层压的步骤(图1中的(f)),以及将压电单晶基底的一部分1b从通过层压获得的粘合体4剥离以获得压电复合基底10的步骤(图1中的(g))。下面将详细描述这些步骤中的每一个。

[0025]

在步骤(a)中制备的压电单晶基底1是由压电单晶制成的基底。作为压电体,可以使用已知的压电体,并且优选具有由锂、金属元素如钽或铌以及氧组成的化合物的压电体。这种化合物的实例包括钽酸锂(litao3;缩写为lt)和铌酸锂(linbo3;缩写为ln)。压电单晶基底1可以以晶圆的形式使用。对晶圆的尺寸没有特别限制,并且其可以具有例如2英寸至12英寸的直径和100μm至1000μm的片厚度。作为压电单晶基底1,可以使用在市场上可买到的晶圆形式或者通过切片等将压电单晶锭加工成晶圆形式而获得的压电单晶基底1。

[0026]

在步骤(b)中,对待层压的压电单晶基底1的表面进行离子注入处理a。如步骤(c)所示,通过该处理,在待层压的压电单晶基底1的表面上形成离子注入层1a。优选在5.0

×

10

16

原子/cm2至2.75

×

10

17

原子/cm2的剂量条件下进行用氢原子离子(h

+

)的离子注入处理。小于5.0

×

10

16

原子/cm2的剂量在随后的步骤中不可能引起离子注入层的脆化。当剂量大于2.75

×

10

17

原子/cm2时,在离子注入过程中,在离子注入表面产生微腔,在晶圆表面上形成不规则体,难以获得所需的表面粗糙度。氢分子离子(h

2+

)优选以2.5

×

10

16

原子/cm2至1.37

×

10

17

原子/cm2的剂量注入

[0027]

离子的加速电压优选为50kev至200kev。通过调节加速电压可以改变离子注入深度。

[0028]

在步骤(d)中制备的作为绝缘基底2的绝缘基底在298k(约25℃)至673k(约400℃)的温度下具有比压电单晶基底1的线性膨胀系数低的线性膨胀系数,这些基底之间的差为14

×

10-6

/k至16

×

10-6

/k。例如,当压电单晶基底1由钽酸锂(lt)制成时,使用线性膨胀系数为2.1

×

10-6

/k至0.1

×

10-6

/k的绝缘基底作为绝缘基底2,因为lt具有16.1

×

10-6

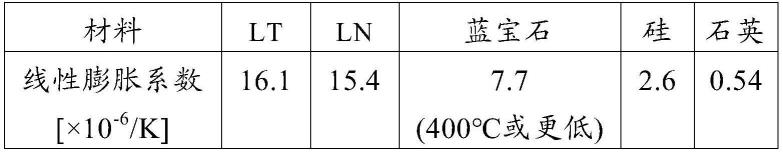

/k的线性膨胀系数。应当注意,在298k与673k的温度之间的线性膨胀系数是通过差示热膨胀计(tma)根据jis r3102:1995测量298k至673k的温度范围内的线性热膨胀系数并进行平均所获得的数值。各种材料的线性膨胀系数示于表1中。

[0029]

表1

[0030]

满足上述与压电单晶基底1的线性膨胀系数的差值的条件的绝缘基底2根据待使用的压电单晶基底1的材料而不同,并且实例包括石英、蓝宝石和硅基底。通过使用线性膨胀系数显著小于压电单晶基底1的线性膨胀系数的绝缘基底2,待粘合到绝缘基底的压电体具有改进的温度性能。石英基底是基本上由石英(sio2)制成的基底。作为石英基底中杂质的金属组分的总含量优选为20质量ppm或更少,更优选为1质量ppm或更少。

[0031]

绝缘基底2可以以晶圆的形式使用,并且在尺寸方面,晶圆具有2英寸至12英寸的直径和100μm至2,000μm的片厚度。

[0032]

优选地,通过研磨抛光等将待层压的压电单晶基底1的表面和待层压的绝缘基底2

的表面各自加工成镜面。待层压表面的表面粗糙度(rms)优选为1.0nm或更小。通过将rms调整到1.0m或更小,这些基底可以通过层压粘合。术语“rms”也称为由jis b 0601:2013规定的“均方根粗糙度rq”。

[0033]

接着,如图1中的步骤(e)所示,在待层压的压电单晶基底1的表面上和待层压的绝缘基底2的表面上形成中间层3a和3b。作为中间层3,使用含硅(si)的无定形材料。含si的无定形材料的实例包括无定形硅膜、氧化硅膜、氮化硅膜和氮氧化硅膜。因此,通过使用含si的无定形材料作为中间层3,在压电单晶基底1与绝缘基底2之间确保了足够的粘合强度。中间层3的厚度没有特别限制,并且其优选为例如10nm至100μm。

[0034]

形成这种中间层3的方法例如是化学气相沉积(cvd)、溅射或旋涂。cvd的实例包括热cvd、等离子体cvd和光cvd。在用于通过上述cvd、溅射或旋涂形成无定形硅膜或氧化硅膜的已知的膜形成条件下,可以在待层压的压电单晶基底1或绝缘基底2的表面上形成中间层3。

[0035]

图1中的步骤(e)示出了中间层3a和3b形成在待层压的压电单晶基底1和绝缘基底2的各自表面上。本发明不限于这种结构,并且也可以仅通过在压电单晶基底1的表面上形成中间层3a或者仅通过在待层压的绝缘基底2的表面上形成中间层3b来实现类似的效果。

[0036]

然后,如图1中的步骤(f)所示,压电单晶基底1和绝缘基底2通过中间层3层压。在层压之前,待层压的压电单晶基底1和绝缘基底2的各自表面经历表面活化处理。表面活化处理不受特别限制,只要其活化待层压的表面即可,实例包括等离子体活化处理、离子束辐照处理、uv臭氧处理和臭氧水处理。特别优选等离子体处理和离子束处理。表面活化处理可以在使用惰性气体如氮气和氩气或氧气的气氛中单独或组合进行。

[0037]

通过经由中间层3层压压电单晶基底1和绝缘基底2而获得的粘合体4经历热处理。该热处理增强了粘合强度,同时能够从压电单晶基底1剥离离子注入层1a。在通过热处理的剥离中,注入的氢离子通过热处理在基底中形成微泡层,然后所得微泡层膨胀以剥离离子注入层。热处理温度优选为100℃至200℃,更优选为100℃至150℃,还更优选为100℃至110℃。当热处理温度高于400℃时,由于压电单晶基底1与绝缘基底2之间的线性膨胀系数的差值大,粘合体4翘曲和变形量大,使得即使在热处理之后也可以保持变形,或者粘合体4可以断裂。另一方面,当热处理温度低于100℃时,粘合强度没有增强或微泡层没有充分膨胀,并且在随后的步骤(g)中,压电单晶基底1可以在层压界面处从绝缘基底2剥离。热处理时间例如优选为1小时至100小时。

[0038]

然后,如图1中的步骤(g)所示,压电单晶基底的一部分1b从经热处理的粘合体4上剥离,同时离子注入层1a留在中间层3的侧面上。这使得可以获得具有经由中间层3形成在绝缘基底2上的离子注入层(压电层)1a的压电复合基底10。应当注意,在这种剥离时,可以使用楔形刀片等(图中省略)产生机械震动。

[0039]

由于这样获得的压电复合基底10使用线性膨胀系数显著小于压电层1a的线性膨胀系数的绝缘基底2,因此它克服了压电体的问题,因此大大改善了温度性能。此外,由于中间层3的存在提高了压电层1a与绝缘基底2之间的粘合强度,因此可以抑制否则会由于热处理而发生的剥落或破裂。

[0040]

已经参考图1描述了根据本实施方案的压电复合基底的制造方法。本发明不局限于此或不被其限制,并且它可以包括许多修改,例如按照上述步骤的顺序改变或结合另一

个新步骤。例如,在图1中,在步骤(b)和(c)中在压电单晶基底1中形成离子注入层1a之后,在步骤(e)中在压电单晶基底1的离子注入层1a的侧面上形成中间层3a。本发明不限于这种顺序,并且在待层压的压电单晶基底1的表面上形成中间层3a之后,可以从压电单晶基底1的中间层3a的侧面进行离子注入处理a。这使得可以在压电单晶基底1的中间层3a的侧面上形成离子注入层1a,如图1所示。同样在这种情况下,可以在类似于前述步骤(b)的离子注入处理条件下形成所需的离子注入层1a。实施例

[0041]

下文将描述实施例和比较例,但本发明不限于这些实施例和比较例或被它们限制。

[0042]

实施例1将具有4英寸直径的钽酸锂(lt)单晶锭切片、研磨并抛光成具有350μm厚度和单侧镜面的lt单晶基底。在所得lt单晶基底的镜面侧,通过cvd形成20nm的无定形硅膜。

[0043]

接着,制备具有双侧镜面和400μm厚度的石英基底作为支撑基底。确认lt基底和石英基底在它们的镜面侧的表面粗糙度rms为1.0nm或更小。然后在氢离子(h

+

)剂量为1

×

10

17

原子/cm2和加速电压为130kev的条件下,lt基底的无定形硅形成的表面经历离子注入处理。

[0044]

然后,待粘合的lt基底和石英基底的各自表面经历等离子体活化处理,并将它们彼此层压。将所得的粘合体在110℃下加热24小时,并且在与粘合表面相对的一侧上的lt基底的一部分被剥离。因此,制造了具有在石英基底上剩余的厚度减薄为860nm的lt单晶膜的石英载lt(lt-on-quartz)复合基底。将所得复合基底在120℃下加热24小时,但没有发生lt层的剥离。将复合基底在125℃下进一步加热12小时,但在复合基底中未发现异常。

[0045]

实施例2将具有4英寸直径的钽酸锂(lt)单晶锭切片、研磨和抛光,并且将42

°

旋转的y切割lt单晶基底精加工成具有500μm厚度和单侧镜面的压电单晶基底。在所得到的lt单晶基底的镜面侧,通过cvd形成氧化硅膜,随后进行抛光以在lt镜面上形成150nm氧化硅膜。

[0046]

接着,制备具有双侧镜面和400μm厚度的石英基底作为支撑基底。确认lt基底和石英基底在它们的镜面侧的表面粗糙度rms为1.0nm或更小。然后,在氢离子(h

+

)剂量为1.25

×

10

17

原子/cm2和加速电压为175kev的条件下,镜面侧的lt基底经历离子注入处理。

[0047]

然后,待粘合的lt基底和石英基底的各自表面经历等离子体活化处理,并将它们彼此层压。将所得粘合体在100℃下加热24小时,并且在其粘合表面的相对侧上的lt基底的一部分被剥离。因此,制造了具有在石英基底上剩余的厚度减薄为1250nm的lt单晶膜的石英载lt复合基底。将所得复合基底在120℃下加热24小时,但没有发生lt层的剥离。将复合基底在125℃下进一步加热12小时,但在复合基底中未发现异常。

[0048]

实施例3将具有4英寸直径的铌酸锂(ln)单晶锭切片、研磨并抛光成具有500μm厚度和单侧镜面的ln单晶基底。在所得ln单晶基底的镜面侧上,通过cvd形成20nm厚的无定形硅膜。

[0049]

接着,制备具有双面镜面和400μm厚度的石英基底作为支撑基底。证实了ln基底和石英基底在其镜面侧的表面粗糙度rms为1.0nm或更小。然后在氢离子(h

+

)剂量为1

×

10

17

原子/cm2和加速电压为130kev的条件下,ln基底的无定形硅形成表面经历离子注入处理。

[0050]

然后,待粘合的ln基底和石英基底的各个表面经历等离子体活化处理,并将它们彼此层压。将所得的粘合体在110℃下加热24小时,并且在与ln基底的粘合表面相对的一侧上的ln基底的一部分被剥离。因此,制造了具有在石英基底上剩余的厚度减薄为900nm的ln单晶膜的石英载ln复合基底。将所得复合基底在120℃下加热24小时,但没有发生ln单晶膜的剥离。将复合基底在125℃下进一步加热12小时,但在复合基底中未发现异常。

[0051]

比较例1将直径为4英寸的钽酸锂单晶(lt)锭切片、研磨并抛光成厚度为350μm的lt单晶基底和单侧镜面。

[0052]

接着,制备具有双侧镜面的400μm厚的石英基底作为支撑基底。确认lt基底和石英基底在它们的镜面侧的表面粗糙度rms为1.0nm或更小。然后在氢离子(h

+

)剂量为1

×

10

17

原子/cm2和加速电压为130kev的条件下,镜面侧的lt基底经历离子注入处理。

[0053]

然后,待粘合的lt基底和石英基底的各自表面经历等离子体活化处理,并将它们彼此层压。将所得的粘合基底在110℃下加热24小时,但lt基底和石英基底在层压界面处彼此分离。

[0054]

比较例2比较例1中使用的lt单晶基底和石英基底经历等离子体活化处理并彼此层压以获得粘合基底。将所得粘合基底热处理至表2中所列的每个温度,并测量此时粘合基底的变形量。结果示于表2中。如图2所示,通过将经热处理的粘合基底20放置在平板上,使基底的中心凹陷部分面朝下,并测量与平板接触的部分与粘合基底的相对于接触部分显示出最大变形的部分之间的高度差,来确定粘合基底的变形量。

[0055]

表2表2

[0056]

因此,当线性膨胀系数显著不同的lt基底和石英基底彼此直接粘合时,粘合基底的变形量即使在低至100℃或更低的温度下也是大的,如表2所示,并且粘合基底即使在热处理之后仍保持变形。另一方面,实施例1至实施例3中获得的石英载lt或石英载ln复合基底即使在超过100℃下进行热处理,也不会以如此大的变形量翘曲,如上所述。参考符号列表

[0057]

1:压电单晶基底

1a:离子注入层2:绝缘基底3:中间层10:压电复合基底20:粘合基底

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1