基于二维半导体沟道的双铁电栅晶体管

1.本发明属于微电子器件技术领域,特别涉及一种可使用单晶体管结构实现存内计算的双铁电栅二维晶体管,这有助于推动下一代高能效比和高面积效率的存内计算器件的发展。

背景技术:

2.随着人工智能物联网(aiot)、机器人和边缘计算等新兴智能应用的出现,智能设备的信息处理系统需要实时、高效地处理海量非结构数据。然而,传统信息处理系统由于受限于传统冯-诺伊曼架构的“内存墙”瓶颈,已经难以满足当前智能设备的数据密集型计算的需要。存内计算就是针对“内存墙”难题而提出的技术方案,该技术的关键在于构建内存和逻辑模块为一体的器件,从而彻底消除数据在内存和逻辑模块间传输的时间和能量消耗,提高计算能效比。

3.铁电场效应二维晶体管因其具有较大的电阻开关比、操作电压低、数据保持时间长等特点被逐渐用作可替代传统flash的新型数据存储器件。然而,受制于其单栅结构,可实现单晶体管布尔逻辑门的铁电场效应二维晶体管还未有报道。

技术实现要素:

4.本发明的目的在于针对传统铁电场效应二维晶体管在存内计算方面的不足,结合超薄二维半导体材料受双铁电耦合极化控制的特性,提供一种基于二维半导体沟道的双铁电栅晶体管及其制备方法,实现单晶体管内的布尔逻辑和数据存储操作,从而获得存内计算功能。

5.本发明的技术方案如下:

6.一、技术原理:

7.根据材料特性研究表明,二维过渡金属硫化物(tmdc)半导体沟道具有独特的能带可调性,可通过铁电栅极化的控制来得到不同的沟道导电率及其非易失保持。在传统铁电场效应二维晶体管内引入双铁电栅结构(双铁电栅二维晶体管),可通过双铁电栅耦合效应对tmdc沟道进行电调控,实现对于tmdc沟道的非易失导电率调整。同时,双铁电栅二维晶体管采用上下铁电层的独立极化作为两个逻辑输入,可根据双铁电栅中极化方向的4种不同组合实现双输入布尔存储逻辑运算及其逻辑态的非易失保持,从而得到存内计算的功能。

8.二、器件结构

9.根据此原理发明的基于二维半导体沟道的双铁电栅晶体管,包括:衬底、底栅电极、底部铁电层、二维半导体沟道层、源极、漏极、顶部铁电层、顶栅电极;顶栅电极、顶部铁电层、二维半导体沟道层、底部铁电层、底栅电极在衬底上依次由上至下竖直分布,且源极、漏极分别位于顶部铁电层两侧。

10.其中底栅电极、漏极、源极和顶栅电极采用金属au材料。

11.其中底部铁电层和顶部铁电层均采用p(vdf-trfe)材料。

12.其中二维半导体沟道层采用二维过渡金属硫化物(tmdc)mos2或mote2材料。

13.制作上述本发明器件的方法,包括如下步骤:

14.(1)利用溶胶-凝胶旋涂工艺,在覆有au下电极的sio2/si衬底上制成p(vdf-trfe)(70:30mo l%)薄膜(厚度约150nm)作为底部铁电层;

15.(2)利用胶带微机械剥离方法,将二维mos2或mote2薄片机械剥离到聚二甲基硅氧烷(pdms)载体上。通过光学显微镜在pdms上识别出合格的mos2或mote2薄片,再用pdms将承载的mos2或mote2薄片转移到p(vdf-trfe)薄膜上,形成二维半导体沟道层;

16.(3)利用光刻和热蒸镀工艺制备具有长条形状的au金属电极,并利用pdms薄膜将其转移到2d tmdc/p(vdf-trfe)结构上,形成源极和漏极;

17.(4)利用溶胶-凝胶旋涂工艺,在2d tmdc/p(vdf-trfe)结构上再次旋涂p(vdf-trfe)(70:30mol%)薄膜(厚度约150nm)作为顶部铁电层;利用pdms转移金属au电极到顶部铁电层结构上,形成顶部栅电极。

18.本发明具有如下优点:

19.本发明由于引入了双铁电栅结构,改变了传统单栅铁电二维晶体管的操作方式,可实现双端输入的布尔逻辑操作;同时,有效利用了二维过渡金属硫化物(tmdc)半导体沟道中独特的能带可调性,保证了半导体沟道在上下铁电栅不同极化组合方式下可呈现不同的电导率,从而实现对逻辑状态的非易失保持,满足存内计算器件的需要。

附图说明

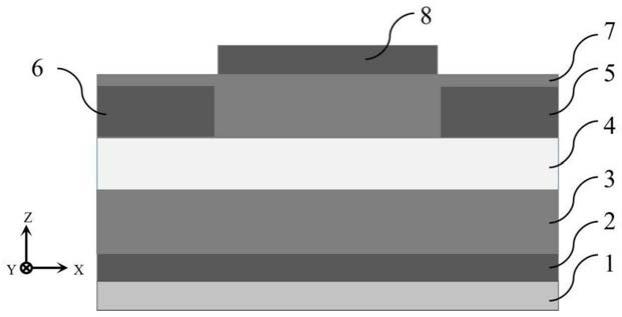

20.图1为本发明的双铁电栅晶体管结构示意图;

21.图2为本发明的双铁电栅晶体管的流程示意图。

具体实施方式

22.为了使本发明的目的及优点更加清楚明白,以下结合附图和实施例对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

23.参照图1,本发明中双铁电栅二维晶体管包括:衬底1、底栅电极2、底部铁电层3、二维半导体沟道层4、源极5、漏极6、顶部铁电层7、顶栅电极8。该衬底1采用sio2材料,该底栅电极2、顶栅电极8、源极5和漏极6均采用金属au材料;该底部铁电层3和顶部铁电层7均采用p(vdf-trfe)材料;该二维半导体沟道层4采用mos2或mote2材料。

24.顶栅电极8、顶部铁电层7、二维半导体沟道层4和底部铁电层3、底栅电极2在衬底1上依次由上至下竖直分布,其中源极5、漏极6分别位于二维半导体沟道层4两侧。

25.参照图2,制作本发明双铁电栅晶体管的方法,实现步骤如下:

26.步骤1:制作底部铁电层

27.如图2(a),通过溶胶-凝胶旋涂工艺,在覆有底栅电极2的衬底1上制成p(vdf-trfe)(70:30mol%)薄膜(厚度约150nm)作为底部铁电层。旋涂参数为3000转/秒,每个循环为30s,如图2(b)。

28.步骤2:制作二维半导体沟道层

29.使用胶带微机械剥离方法将二维mos2或mote2薄片机械剥离到聚二甲基硅氧烷

(pdms)载体上,通过光学显微镜在pdms上识别出合格的mos2或mote2薄片,再用pdms承载mos2或mote2薄片并将其转移到p(vdf-trfe)薄膜上。形成二维半导体沟道层,如图2(c)。

30.步骤3:制作源极、漏极

31.利用光刻和热蒸镀工艺制作特定形状的金属au电极,使用pdms转移金属au电极到2d tmdc/p(vdf-trfe)结构上,形成源极和漏极,如图2(d)。

32.步骤4:制作顶部铁电层

33.通过溶胶-凝胶旋涂工艺,在2d tmdc/p(vdf-trfe)结构上制成p(vdf-trfe)(70:30mol%)薄膜(厚度约150nm)作为顶部铁电层。旋涂参数为3000转/秒,每个循环为30s,如图2(e)。

34.步骤5:制作顶栅电极

35.利用光刻和热蒸镀工艺制作特定形状的金属au电极,并使用pdms转移金属au电极到顶部铁电层结构上,形成顶栅电极,如图2(f)。

36.本发明通过双铁电栅耦合效应对tmdc沟道进行电调控,实现对于tmdc沟道的非易失导电率调整。同时,双铁电栅二维晶体管采用上下铁电层的独立极化作为两个逻辑输入,可根据双铁电栅中极化方向的4种不同组合实现双输入布尔存储逻辑运算及其逻辑态的非易失保持,从而得到存内计算的功能。

37.以上所述仅是本发明的一个优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1