半导体装置的制作方法

半导体装置

1.相关申请的交叉引用

2.本技术享有以日本专利申请2021-154765号(申请日:2021年9月22日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

3.本发明的实施方式涉及半导体装置。

背景技术:

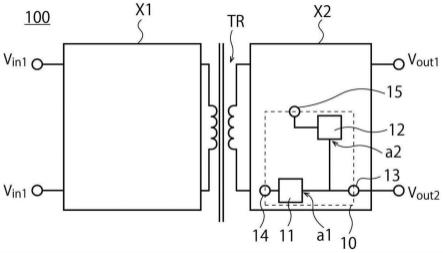

4.包含dc-dc转换器的电力变换装置等的半导体装置要求小型化和电力提高,即要求电力密度的提高。为了使电力密度提高,半导体元件的封装化不断发展。

技术实现要素:

5.实施方式提供一种使电力密度提高的半导体装置。

6.实施方式的半导体装置具备dc-dc转换器,该dc-dc转换器具有初级侧电路和包含第1半导体封装的次级侧电路,该第1半导体封装收容有包含第1半导体元件及第2半导体元件的第1半导体元件组,第1半导体元件及第2半导体元件层叠,第1半导体元件组为mosfet、igbt或二极管,第1半导体封装中包含有如下第1引线框,在第1半导体元件组为mosfet的情况下,所述第1引线框使第1半导体元件的源极电极与第2半导体元件的源极电极在第1半导体元件及第2半导体元件的层叠方向上对置而电连接,在第1半导体元件组为igbt的情况下,所述第1引线框使第1半导体元件的发射极电极与第2半导体元件的发射极电极在第1半导体元件及第2半导体元件的层叠方向上对置而电连接,或在第1半导体元件组为二极管的情况下,所述第1引线框使第1半导体元件的阴极电极与第2半导体元件的阴极电极在第1半导体元件及第2半导体元件的层叠方向上对置而电连接,第1引线框位于第1半导体元件与第2半导体元件之间。

附图说明

7.图1是实施方式的半导体装置的示意图。

8.图2是实施方式的半导体封装的示意图。

9.图3是实施方式的半导体封装的示意剖视图。

10.图4是实施方式的半导体封装的示意剖视图。

11.图5是实施方式的半导体封装的示意剖视图。

12.图6是实施方式的半导体封装的示意图。

13.图7是实施方式的半导体封装的示意剖视图。

14.图8是实施方式的半导体封装的示意剖视图。

15.图9是实施方式的半导体封装的示意剖视图。

16.图10是实施方式的半导体封装的示意剖视图。

17.图11是实施方式的半导体封装的示意图。

18.图12是实施方式的半导体封装的示意剖视图。

19.图13是实施方式的半导体封装的示意剖视图。

20.图14是实施方式的半导体封装的示意剖视图。

21.图15是实施方式的半导体封装的示意图。

22.图16是实施方式的半导体封装的示意剖视图。

23.图17是实施方式的半导体封装的示意剖视图。

24.图18是实施方式的电路图。

25.图19是实施方式的半导体封装的示意图。

26.图20是实施方式的半导体封装的示意图。

27.图21是实施方式的半导体封装的示意剖视图。

28.图22是实施方式的半导体封装的示意剖视图。

29.图23是实施方式的半导体封装的示意剖视图。

30.图24是实施方式的电路图。

31.图25是实施方式的电路图。

32.图26是实施方式的半导体封装的示意图。

33.图27是实施方式的半导体装置的示意图。

34.图28是实施方式的半导体封装的示意图。

35.图29是实施方式的半导体封装的示意图。

36.图30是实施方式的半导体封装的示意图。

37.图31是实施方式的半导体封装的示意图。

38.图32是实施方式的电路图。

39.图33是实施方式的电路图。

40.图34是实施方式的电路图。

具体实施方式

41.下面,参照附图对本发明的实施方式进行说明。此外,在下面的说明中,对相同或类似的部件等标注同一附图标记,关于已说明过一次的部件,有时省略其说明。

42.在本说明书中,为了表示部件等的位置关系,将附图的上方向记载为“上”,将附图的下方向记载为“下”或“底”。在本说明书中,“上”、“下”、“底”的概念不一定是表示与重力的朝向的关系的用语。

43.(第1实施方式)

44.第1实施方式涉及半导体装置,具体地说涉及电力变换装置。电力变换装置具有dc-dc转换器。在图1示出实施方式的电力变换装置100的示意性电路图。在图1的示意性电路图包含变压器tr、初级侧电路x1和次级侧电路x2。初级侧电路x1与次级侧电路x2通过变压器tr而绝缘。

45.初级侧电路x1与变压器tr的初级线圈连接。初级线圈和输入电源与初级侧电路x1并联连接。初级侧电路x1与高电位侧输入端子v

in1

和低电位侧输入端子v

in2

连接。高电位侧输入端子v

in1

和低电位侧输入端子v

in2

与输入电源(dc电源)连接。向初级侧电路x1的高电位

侧输入端子v

in1

和低电位侧输入端子v

in2

输入dc电源,通过包含开关元件的电路而变换为交流。在变压器tr的初级线圈中流过交流电流,在次级侧电路x2的次级线圈中流过由初级线圈感应产生的交流电流。

46.次级侧电路x2与变压器tr的次级线圈连接。次级侧电路x2与高电位侧输出端子v

out1

和低电位侧输出端子v

out2

连接。高电位侧输出端子v

out1

和低电位侧输出端子v

out2

例如与未图示的负载连接。在次级侧电路x2中包含第1半导体封装10。从次级线圈向次级侧电路x2流过的交流电流通过次级侧电路x2而变换为直流电流。

47.第1半导体封装10收容有包含第1半导体元件11和第2半导体元件12的第1半导体元件组。在第1半导体封装10可以包含除了第1半导体元件11和第2半导体元件12以外的半导体元件。第1半导体封装10具有第1共用端子13。在第1半导体封装10中包含与第1半导体元件11连接的第1非共用端子14和与第2半导体元件12连接的第2非共用端子15。电流从第1非共用端子14及第2非共用端子15向第1共用端子13流动。即,2个半导体元件(11、12)的电流的输入(端子)相区别,电流的输出(端子)是共用的。第1共用端子13与次级侧电路x2的低电位侧输出端子v

out2

电连接。

48.第1半导体元件11及第2半导体元件12通过密封材料m进行密封。在实施方式中,引线框的端部的从密封材料m露出的部分成为端子,但能够采用在半导体封装中使用的螺钉型端子等,并不特别受到限定。

49.第1半导体元件组优选的是mosfet(metal-oxide-semiconductor field-effect transistor)、igbt(insulated gate bipolar transistor)或二极管。第1半导体元件11及第2半导体元件12优选为相同种类的半导体元件。即,在将mosfet用作第1半导体元件11的情况下,将mosfet用作第2半导体元件12,但不将igbt或二极管用作第2半导体元件12。

50.作为mosfet,具体地说,优选纵向型的mosfet,优选n型mosfet。在实施方式中,以n型mosfet为例进行说明。

51.作为igbt,具体地说,优选纵向型的igbt,优选n沟道型igbt。在实施方式中,以n沟道型igbt为例进行说明。

52.作为二极管,具体地说,优选纵向型的二极管,更优选纵向型的肖特基势垒二极管。

53.密封材料m例如是模制树脂,在典型情况下,包含环氧树脂和填料。

54.在图2-4示出第1半导体封装10的剖视示意图。将第1半导体元件11及第2半导体元件12的层叠方向设为z方向,将与z方向垂直的方向设为x方向、y方向。x方向与y方向正交。第1半导体元件11的朝向第2半导体元件12的面优选与x-y面平行。另外,第2半导体元件12的朝向第1半导体元件11的面优选与x-y面并行。

55.图2的示意图(x-y面)是从第1半导体封装10的端子侧即底面侧观察到的示意图。另外,在图2的剖视图中还示出了从一部分的底面观察不到的部件等。图3是图2的a-a’剖面(y-z面)的剖视示意图。图4是图2的b-b’剖面(y-z面)的剖视示意图。图5是图2的c-c’剖面(x-z面)的剖视示意图。

56.第1半导体封装10内的第1半导体元件11和第2半导体元件12以在电气上并联连接的方式层叠。

57.以第1半导体元件组即第1半导体元件11及第2半导体元件12为n型mosfet的情况

为例,对图2-5的示意图所示的第1半导体封装10进行说明。以下说明的一部分在第1半导体元件11及第2半导体元件12为igbt的情况下和为二极管的情况下也是共通的。第1半导体元件11及第2半导体元件12两者都是n型(n沟道型)的mosfet或igbt。

58.第1半导体元件11具有源极电极a1、漏极电极b1及栅极电极c1。另外,第2半导体元件12具有源极电极a2、漏极电极b2及栅极电极c2。

59.第1半导体元件11的源极电极a1与第1半导体元件11的源极电连接,设置于第1半导体元件11的表面(第1面s1)。第2半导体元件12的源极电极a2与第2半导体元件12的源极电连接,设置于第2半导体元件12的表面(第1面s1)。

60.第1半导体元件11的漏极电极b1与第1半导体元件11的漏极电连接,设置于第1半导体元件11的表面(第2面s2)。第1半导体元件11的第2面s2是第1半导体元件11的与第1面s1相反侧的表面。第2半导体元件12的漏极电极b2与第2半导体元件12的漏极电连接,设置于第2半导体元件12的表面(第2面s2)。第2半导体元件12的第2面s2是第2半导体元件12的与第1面s1相反侧的表面。

61.第1半导体元件11的栅极电极c1与第1半导体元件11的栅极电连接,设置于第1半导体元件11的表面(第1面s1)。第2半导体元件12的栅极电极c2与第2半导体元件12的栅极电连接,设置于第2半导体元件12的表面(第1面s1)。

62.在第1半导体元件11及第2半导体元件12的各电极包含电极焊盘或电极焊盘及焊料等的导电性接合部件。

63.第1半导体元件11的源极电极a1与第2半导体元件12的源极电极a2在第1半导体元件11和第2半导体元件12的层叠方向上对置而电连接。

64.第1半导体元件11的第1面s1与第2半导体元件12的第1面s1对置,即,第1半导体元件11的源极电极a1与第2半导体元件12的源极电极a2面向第1半导体封装10的内侧而相面对。

65.第1半导体元件11的漏极电极b1与第2半导体元件12的漏极电极b2面向第1半导体封装10的外侧而朝向相反方向。

66.在第1半导体元件组为mosfet的情况下,具有使第1半导体元件11的源极电极a1及第2半导体元件12的源极电极a2对置地电连接的引线框p1(第1引线框)。第1半导体元件11的源极电极a1及第2半导体元件12的源极电极a2优选在第1半导体元件11和第2半导体元件12的层叠方向上对置。另外,第1半导体封装10的引线框p1的面向第1半导体元件11的面与第1半导体元件11的源极电极a1直接连接。第1半导体封装10的引线框p1的面向第2半导体元件12的面与第2半导体元件12的源极电极a2直接连接。

67.如图3~图4的剖视图所示,在源极电极a1与源极电极a2之间设置有引线框p1。引线框p1与第1半导体元件11的源极和第2半导体元件12的源极这两者连接。引线框p1与源极电极a1及源极电极a2相接,优选直接相接。如图3~图4所示,引线框p1朝向第1共用端子13延伸。引线框p1的一部分延伸至第1半导体封装10的底面侧为止。如图2所示,引线框p1与在半导体封装10的侧面的外侧露出的第1共用端子13连接。

68.如图2~图4所示,第1半导体元件11的漏极电极b1位于第1半导体封装10的底面侧。漏极电极b1与引线框q1相接,优选直接相接。引线框q1与第1半导体元件11的漏极连接,但不与第2半导体元件12的漏极连接。如图2~图4所示,引线框q1优选在第1半导体封装10

的底面侧露出。如图2~图4所示,引线框q1与在半导体封装10的侧面的外侧露出的第1非共用端子14连接。

69.如图2~图5所示,第2半导体元件12的漏极电极b2位于第1半导体封装10的上表面侧。即,源极电极a1及源极电极a2位于漏极电极b1与漏极电极b2之间。漏极电极b2与引线框q2相接,优选直接相接。引线框q2与第2半导体元件12的漏极连接,但不与第1半导体元件11的引线框q1连接。如图5所示,引线框q2朝向第1半导体封装10的底面方向折弯而延伸。引线框q1独立于引线框q2。引线框q2与在第1半导体封装10的侧面的外侧露出的第2非共用端子15连接。第1非共用端子14独立于第2非共用端子15。

70.如图2~图5所示,引线框q1向引线框q2的相反方向延伸。另外,如图2~图5所示,引线框p1向相对于引线框q1偏移了90

°

的方向延伸。

71.如图2~图4所示,第1半导体元件11的栅极电极c1与第1半导体元件11的第1面s1的源极电极a1邻接。栅极电极c1与引线框r1相接,优选直接相接。引线框r1与第1半导体元件11的栅极连接,但不与第2半导体元件12的栅极连接。如图3所示,引线框r1向第1半导体封装10的底面侧折弯而延伸。引线框r1与在第1半导体封装10的侧面外侧露出的栅极端子16连接。在栅极端子16连接有未图示的栅极驱动器。第1半导体元件11的动作由栅极驱动器进行控制。

72.如图2~图4所示,第2半导体元件12的栅极电极c2与第2半导体元件12的第1面s1的源极电极a2邻接。栅极电极c2与引线框r2相接,优选直接相接。引线框r2与第2半导体元件12的栅极连接,但不与第1半导体元件11的栅极连接。如图4所示,引线框r2向第1半导体封装10的底面侧折弯而延伸。引线框r2与在第1半导体封装10的侧面外侧露出的栅极端子17连接。在栅极端子17连接有未图示的栅极驱动器。第2半导体元件12的动作由栅极驱动器进行控制。

73.如图2~图4所示,引线框r1与引线框r2并行地排列而延伸。另外,如图2~图4所示,引线框r1及引线框r2在相对于引线框q1的与引线框p1相反侧,向相对于引线框q1偏移了90

°

的方向延伸。

74.若栅极电极c1与栅极电极c2以在第1半导体元件11和第2半导体元件12的层叠方向上重叠的方式配置,则引线框r1与引线框r2容易短路。因此,如图2~图4的示意图所示,优选栅极电极c1与栅极电极c2在第1半导体元件11和第2半导体元件12的层叠方向上不重叠。

75.第1半导体封装10以夹着引线框p1的方式设置有源极电极a1和源极电极a2。由此,能够兼顾使第1半导体元件11与第2半导体元件12层叠和将两个半导体元件的源极通过1个引线框p1进行连接。与将在dc-dc转换器的次级侧电路x2中设置的2个开关(二极管)单独设置的情况相比,能够在更少的面积中设置第1半导体封装10,减小安装面积,有助于电力变换装置100的小型化。即,使用了第1半导体封装10的电力变换装置100能够提高电力密度。在将第1半导体元件11和第2半导体元件12单独设置的情况下,在各自中使用散热器等散热部件,但通过如实施方式那样使用第1半导体封装10,能够将散热部件也设为1个,实施方式的电力变换装置100有助于降低部件成本、安装成本。第1半导体封装10除了引线框p1在2个半导体元件之间与两个源极连接这一点以外,能够自由地设计半导体封装10。

76.在使第1半导体元件11和第2半导体元件12互补地接通-断开的情况下,若第1半

导体元件11的面积和第2半导体元件12的面积为相同程度,则流过2个元件的电流为相同程度,2个元件的温度上升成为相同程度,元件不易破坏。即,优选第1半导体元件11的元件区域面积和第2半导体元件12的元件区域的面积为相同程度。具体地说,第1半导体元件11的面积(元件区域的面积)优选为第2半导体元件12的面积(元件区域的面积)的50%以上且150%以下,更优选为75%以上且125%以下,进一步优选为90%以上且110%以下。

77.接下来,以第1半导体元件组即第1半导体元件11及第2半导体元件12为n沟道型igbt的情况为例对图6~图10的示意图所示的第1半导体封装10进行说明。

78.图6的示意图(x-y面)是从第1半导体封装10的端子侧即底面侧观察到的示意图。另外,在图6的剖视图中还示出了从一部分的底面观察不到的部件等。图7是图6的a-a’剖面(y-z面)的剖视示意图。图8是图6的b-b’剖面(y-z面)的剖视示意图。图9是图6的c-c’剖面(x-z面)的剖视示意图。图10是图6的d-d’剖面(y-z面)的剖视示意图。

79.第1半导体元件11具有发射极电极a1、集电极电极b1及基极电极c1。另外,第2半导体元件12具有发射极电极a2、集电极电极b2及基极电极c2。

80.第1半导体元件11的发射极电极a1与第1半导体元件11的发射极电连接,设置于第1半导体元件11的表面(第1面s1)。第2半导体元件12的发射极电极a2与第2半导体元件12的发射极电连接,设置于第2半导体元件12的表面(第1面s1)。

81.第1半导体元件11的集电极电极b1与第1半导体元件11的集电极电连接,设置于第1半导体元件11的表面(第2面s2)。第1半导体元件11的第1面s1是第1半导体元件11的与第1面s1相反侧的表面。第2半导体元件12的集电极电极b2与第2半导体元件12的集电极电连接,设置于第2半导体元件12的表面(第2面s2)。第2半导体元件12的第1面s1是第2半导体元件12的与第1面s1相反侧的表面。

82.第1半导体元件11的基极电极c1与第1半导体元件11的基极电连接,设置于第1半导体元件11的表面(第1面s1)。第2半导体元件12的基极电极c2与第2半导体元件12的基极电连接,设置于第2半导体元件12的表面(第1面s1)。

83.第1半导体元件11的发射极电极a1与第2半导体元件12的发射极电极a2在第1半导体元件11和第2半导体元件12的层叠方向上对置而电连接。

84.在第1半导体元件组为igbt的情况下,具有使第1半导体元件11的发射极电极a1及第2半导体元件12的发射极电极a2对置地电连接的引线框p1(第1引线框)。第1半导体元件11的发射极电极a1及第2半导体元件12的发射极电极a2优选在第1半导体元件11和第2半导体元件12的层叠方向上对置。另外,第1半导体封装10的引线框p1的面向第1半导体元件11的面与第1半导体元件11的发射极电极a1直接连接。第1半导体封装10的引线框p1的面向第2半导体元件12的面与第2半导体元件12的发射极电极a2直接连接。

85.第1半导体元件11的第1面s1与第2半导体元件12的第1面s1对置,即第1半导体元件11的发射极电极a1与第2半导体元件12的发射极电极a2面向第1半导体封装10的内侧而相面对。

86.第1半导体元件11的集电极电极b1和第2半导体元件12的集电极电极b2面向第1半导体封装10的外侧而朝向相反方向。

87.如图7~图8的剖视图所示,在发射极电极a1和发射极电极a2之间设置有引线框p1。引线框p1与第1半导体元件11的发射极和第2半导体元件12的发射极这两者连接。引线

框p1与发射极电极a1及发射极电极a2相接,优选直接相接。如图7~图8所示,引线框p1朝向第1共用端子13而延伸。引线框p1的一部分延伸至第1半导体封装10的底面侧为止。如图2所示,引线框p1与在半导体封装10的侧面的外侧露出的第1共用端子13连接。

88.如图6~图8所示,第1半导体元件11的集电极电极b1位于第1半导体封装10的底面侧。集电极电极b1与引线框q1相接,优选直接相接。引线框q1与第1半导体元件11的集电极连接,但不与第2半导体元件12的集电极连接。如图6~图8所示,引线框q1优选在第1半导体封装10的底面侧露出。如图2~图4所示,引线框q2与在半导体封装10的侧面的外侧露出的第1非共用端子14连接。

89.如图6~图8所示,第2半导体元件12的集电极电极b2位于第1半导体封装10的上表面侧。即,发射极电极a1及发射极电极a2位于集电极电极b1与集电极电极b2之间。集电极电极b2与引线框q2相接,优选直接相接。引线框q2与第2半导体元件12的集电极连接,但不与第1半导体元件11的引线框q1连接。如图5所示引线框q2向第1半导体封装10的底面侧折弯而延伸。引线框q1独立于引线框q2。引线框q2与在第1半导体封装10的侧面的外侧露出的第2非共用端子15连接。第1非共用端子14独立于第2非共用端子15。

90.如图6~图8所示,引线框q1与引线框q2并列而并行地延伸。另外,如图6~图8所示引线框p1向引线框q1及引线框q2的相反侧延伸。

91.如图6、图9所示,第1半导体元件11的基极电极c1与第1半导体元件11的第1面s1的发射极电极a1邻接。基极电极c1与引线框r1相接,优选直接相接。引线框r1与第1半导体元件11的基极连接,但不与第2半导体元件12的基极连接。如图9所示引线框r1向第1半导体封装10的底面侧折弯而延伸。引线框r1与在第1半导体封装10的侧面外侧露出的基极端子16连接。基极端子16与未图示的igbt驱动器连接。第1半导体元件11的动作由igbt驱动器进行控制。

92.如图6、图10所示,第2半导体元件12的基极电极c2与第2半导体元件12的第1面s1的发射极电极a2邻接。基极电极c2与引线框r2相接,优选直接相接。引线框r2与第2半导体元件12的基极连接,但不与第1半导体元件11的基极连接。图10所示引线框r2向第1半导体封装10的底面侧折弯而延伸。引线框r2与在第1半导体封装10的侧面外侧露出的基极端子17连接。基极端子17与未图示的igbt驱动器连接。第2半导体元件12的动作由igbt驱动器进行控制。

93.如图6、图9~图10所示,引线框r1向引线框r2的相反方向延伸。另外,如图6、图9~图10所示引线框r1向相对于引线框q1偏移了90

°

的方向延伸。另外,引线框r2在相对于引线框q1的与引线框r1相反侧,向相对于引线框q1偏移了90

°

的方向延伸。

94.接下来,参照图11~图14的示意图,对第1半导体元件11与第2半导体元件12的大小存在差异的第1半导体封装10进行说明。第1半导体元件11及第2半导体元件12以mosfet为例进行说明,但也能够取代mosfet而使用igbt。

95.图11~图14的示意图所示的第1半导体封装10是图2~图5的示意图所示的半导体封装10的变形例。除了第1半导体元件11与第2半导体元件12的大小存在差异以外,图11~图14的示意图所示的第1半导体封装10与图2~图5的示意图所示的半导体封装10相同。

96.如图11~图14的示意图所示,第1半导体元件11与第2半导体元件12的大小不同,但第1半导体元件11与第2半导体元件12以源极电极a1与源极电极a2夹着引线框p1的方式

层叠。

97.在第1半导体元件11和第2半导体元件12的大小存在差异的情况下,如图12及图13的示意图所示,能够采用下述结构,即,位于第1半导体元件11与第2半导体元件12之间的引线框p1与源极电极a1及源极电极a2相接,2个半导体元件的源极与第1共用端子13连接。

98.在第1半导体元件11与第2半导体元件12的大小存在差异的情况下,如图12~图14的剖视图所示,也能够将漏极电极b1与引线框q1进行连接,将漏极电极b2与引线框q2进行连接。引线框q1和引线框q2与分别独立的第1非共用端子14和第2非共用端子15连接。

99.在第1半导体元件11与第2半导体元件12的大小存在差异的情况下,如图12、图13的剖视图所示,也能够将栅极电极c1与引线框r1进行连接,将栅极电极c2与引线框r2进行连接。引线框r1和引线框r2分别独立。

100.接下来,以第1半导体元件组即第1半导体元件11及第2半导体元件12为二极管的情况为例,对图15~图17的示意图所示的第1半导体封装10进行说明。

101.图15的示意图(x-y面)是从第1半导体封装10的端子侧即底面侧观察的示意图。另外,在图15的剖视图还示出了从一部分的底面观察不到的部件等。图16是图15的a-a’剖面(y-z面)的剖视示意图。图17是图15的b-b’剖面(y-z面)的剖视示意图。

102.第1半导体元件11具有阴极电极a1及阳极电极b1。另外,第2半导体元件12具有阴极电极a2及阳极电极b2。

103.第1半导体元件11的阴极电极a1与第1半导体元件11的阴极电连接,设置于第1半导体元件11的表面(第1面s1)。第2半导体元件12的阴极电极a2与第2半导体元件12的阴极电连接,设置于第2半导体元件12的表面(第1面s1)。

104.第1半导体元件11的阳极电极b1与第1半导体元件11的阳极电连接,设置于第1半导体元件11的表面(第2面s2)。第1半导体元件11的第1面s1是第1半导体元件11的与第1面s1相反侧的表面。第2半导体元件12的阳极电极b2与第2半导体元件12的阳极电连接,设置于第2半导体元件12的表面(第2面s2)。第2半导体元件12的第1面s1是第2半导体元件12的与第1面s1相反侧的表面。

105.第1半导体元件11的阴极电极a1与第2半导体元件12的阴极电极a2在第1半导体元件11和第2半导体元件12的层叠方向上对置而电连接。

106.在第1半导体元件组为二极管的情况下,具有使第1半导体元件11的阴极电极a1及第2半导体元件12的阴极电极a2对置而电连接的引线框p1(第1引线框)。第1半导体元件11的阴极电极a1及第2半导体元件12的阴极电极a2优选在第1半导体元件11和第2半导体元件12的层叠方向上对置。另外,第1半导体封装10的引线框p1的面向第1半导体元件11的面与第1半导体元件11的阴极电极a1直接连接。第1半导体封装10的引线框p1的面向第2半导体元件12的面与第2半导体元件12的阴极电极a2直接连接。

107.第1半导体元件11的第1面s1与第2半导体元件12的第1面s1对置,即第1半导体元件11的阴极电极a1与第2半导体元件12的阴极电极a2面向第1半导体封装10的内侧而相面对。

108.第1半导体元件11的阳极电极b1与第2半导体元件12的阳极电极b2面向第1半导体封装10的外侧而朝向相反方向。

109.如图16~图17的剖视图所示,在阴极电极a1与阴极电极a2之间设置有引线框p1。

引线框p1与第1半导体元件11的阴极和第2半导体元件12的阴极这两者连接。引线框p1与阴极电极a1及阴极电极a2相接,优选直接相接。如图16~图17所示引线框p1朝向第1共用端子13而延伸。引线框p1的一部分延伸至第1半导体封装10的底面侧为止。如图5所示,引线框p1与在半导体封装10的侧面的外侧露出的第1共用端子13连接。

110.如图16~图17所示,第1半导体元件11的阳极电极b1位于第1半导体封装10的底面侧。阳极电极b1与引线框q1相接,优选直接相接。引线框q1与第1半导体元件11的阳极连接,但不与第2半导体元件12的阳极连接。如图6~图8所示,引线框q1优选在第1半导体封装10的底面侧露出。如图2~图4所示,引线框q2与在半导体封装10的侧面的外侧露出的第1非共用端子14连接。

111.如图16~图17所示,第2半导体元件12的阳极电极b2位于第1半导体封装10的上表面侧。即,阴极电极a1及阴极电极a2位于阳极电极b1与阳极电极b2之间。阳极电极b2与引线框q2相接,优选直接相接。引线框q2与第2半导体元件12的阳极连接,但不与第1半导体元件11的引线框q1连接。如图5所示引线框q2向第1半导体封装10的底面侧折弯而延伸。引线框q1独立于引线框q2。引线框q2与在第1半导体封装10的侧面的外侧露出的第2非共用端子15连接。第1非共用端子14独立于第2非共用端子15独立。

112.如图15~图17所示,引线框q1与引线框q2并列而并行地延伸。另外,如图15~图17所示,引线框p1向引线框q1及引线框q2的相反侧延伸。

113.(第2实施方式)

114.第2实施方式涉及半导体装置,具体地说,涉及电力变换装置。第2实施方式作为使用了第1半导体封装10的具体例,涉及具有双晶正激型(日语:2石式

ダブルフォワード

型)dc-dc转换器的电力变换装置100。第2实施方式的电力变换装置100在次级侧电路x2包含第1半导体封装10。第2实施方式的电力变换装置100以第1半导体元件11及第2半导体元件12为mosfet的情况为例进行说明,但第1半导体元件11及第2半导体元件12也可以是igbt或二极管。在第2实施方式中,优选使用第1实施方式及第2实施方式中说明的第1半导体封装10。

115.在图18中示出第2实施方式的双晶正激型(2石双正激型)dc-dc转换器的电路图。图18所示的电路图是双晶正激型dc-dc转换器的电路图的一个例子,电路结构能够适当变更。在初级侧电路x1包含开关元件q1-q5、二极管d1-d4、电容器c1-c2,与第1变压器tr1和第2变压器tr2的初级线圈连接。使开关元件q1、q3和开关元件q2、q4交替地接通-断开。初级侧电路x1的各开关元件为mosfet或igbt。在各开关元件连接有栅极驱动器或igbt驱动器,但省略图示。

116.在次级侧电路x2包含开关元件q6-q9、线圈l2、电容器c3,与第1变压器tr1和第2变压器tr2的次级线圈连接。在次级侧电路x2中,使开关元件q6和开关元件q7交替地接通-断开。

117.在双晶正激型dc-dc转换器中,优选使用作为第1半导体元件11而收容有开关元件q6及作为第2半导体元件12而收容有开关元件q7、或作为第1半导体元件11而收容有开关元件q7及作为第2半导体元件12而收容有开关元件q8的第1半导体封装10。在开关元件q6及开关元件q7为mosfet的情况下,能够采用2个开关元件q6、q7的源极与低电位侧输出端子v

out2

连接且将这些开关元件的源极端子共用化而成的第1半导体封装10。

118.开关元件q8的源极侧也与低电位侧输出端子v

out2

连接。因此,在第1半导体封装10中,在开关元件q6(第1半导体元件11)、开关元件q7(第2半导体元件12)的基础上,能够收容开关元件q8作为第3半导体元件。第3半导体元件的源极电极也优选与引线框p1连接,并优选与第1共用端子13电连接。

119.第3半导体元件包含于第1半导体元件组。在第1半导体元件11及第2半导体元件为mosfet的情况下,第3半导体元件也为mosfet。另外,在第1半导体元件11及第2半导体元件12为igbt的情况下,第3半导体元件也为igbt。第3半导体元件的面积(元件区域的面积)优选为第1半导体元件11的面积(元件区域的面积)的50%以上且150%以下,更优选为75%以上且125%以下,进一步优选为90%以上且110%以下。

120.在第2实施方式中,能够使用收容有开关元件q3及开关元件q4的第2半导体封装20。第2半导体封装20收容第2半导体元件组。在第2半导体封装20的开关元件q3和开关元件q4为p型mosfet的情况下,在第2半导体封装20采用第3半导体封装的结构,被漏极电极b1及漏极电极b2夹着的引线框与低电位侧输入端子v

in2

连接。

121.在图19示出第2半导体封装20的示意图。图19的示意图(x-y面)是从第2半导体封装20的端子侧即底面侧观察到的示意图。另外,在图19的示意图中还示出从一部分的底面观察不到的部件等。图19的a-a’剖面(y-z面)的剖视示意图相当于图3的a-a’剖面(y-z面)的剖视示意图。图19的b-b’剖面(y-z面)的剖视示意图相当于图4的b-b’剖面(x-z面)的剖视示意图。图19的c-c’剖面(y-z面)的剖视示意图是图5的c-c’剖面(x-z面)的剖视示意图。

122.在第2半导体元件组中包含第4半导体元件21和第5半导体元件22。第2半导体元件组为mosfet或igbt。以下,主要以第2半导体元件组为mosfet的情况为例进行说明。关于第2半导体元件组为igbt的情况也进行一部分说明。

123.第2半导体封装20将开关元件q3作为第4半导体元件21进行收容,将开关元件q4作为第5半导体元件22进行收容,或将开关元件q4作为第4半导体元件21进行收容,将开关元件q3作为第5半导体元件22进行收容。第2半导体封装20具有第2共用端子23、第3非共用端子24、第4非共用端子25、栅极端子26、栅极端子27。第2共用端子23与初级侧电路x1的低电位侧输入端子v

in2

电连接。

124.第4半导体元件21相当于第1半导体元件11,第5半导体元件22相当于第2半导体元件12。第2半导体封装20的第2共用端子23、第3非共用端子24及第4非共用端子25分别相当于第1半导体封装10的第1共用端子13、第1非共用端子14、第2非共用端子15。

125.第1半导体封装10和第2半导体封装20为相同的装置,因此将其说明省略一部分。在第1半导体封装10和第2半导体封装20中,一部分的部件的附图标记或一部分的部件的名称是共用的。关于第2半导体封装20,对与第1半导体封装10共用的内容省略其说明及对应的示意图。

126.在第2半导体封装20可以包含除了第4半导体元件21和第5半导体元件22以外的半导体元件,例如,可以包含第4半导体元件21、第5半导体元件22和源极侧的配线共用的第6半导体元件(例如,开关元件q5)。

127.在第4半导体元件21与第5半导体元件22之间设置有引线框p1(第2引线框)。第2共用端子23与引线框p1连接。第3非共用端子24与引线框q1连接。第4非共用端子25与引线框

q2连接。栅极端子26与引线框r1连接。栅极端子27与引线框r2连接。

128.在第2半导体元件组为mosfet的情况下,具有使第4半导体元件21的源极电极a1及第5半导体元件22的源极电极a2对置地电连接的引线框p1(第2引线框)。第4半导体元件21的源极电极a1及第5半导体元件22的源极电极a2优选在第4半导体元件21和第5半导体元件22的层叠方向上对置。另外,第2半导体封装20的引线框p1的面向第4半导体元件21的面与第4半导体元件21的源极电极a1直接连接。第2半导体封装20的引线框p1的面向第5半导体元件22的面与第5半导体元件22的源极电极a2直接连接。

129.在第2半导体元件组为igbt的情况下,具有使第4半导体元件21的发射极电极a1及第5半导体元件22的发射极电极a2对置地电连接的引线框p1(第2引线框)。第4半导体元件21的发射极电极a1及第5半导体元件22的发射极电极a2优选在第4半导体元件21和第5半导体元件22的层叠方向上对置。另外,第2半导体封装20的引线框p1的面向第4半导体元件21的面与第4半导体元件21的发射极电极a1直接连接。第2半导体封装20的引线框p1的面向第5半导体元件22的面与第5半导体元件22的发射极电极a2直接连接。

130.第2半导体封装20也以夹着引线框p1的方式设置有源极电极a1和源极电极a2。于是,能够兼顾使第4半导体元件21与第5半导体元件22层叠和将两个半导体元件的源极通过1个引线框p1进行连接。与将在dc-dc转换器的初级侧电路x1中设置的2个开关元件单独设置的情况相比,能够在更少的面积中设置第2半导体封装20,减小安装面积,有助于电力变换装置100的小型化。即,使用了第2半导体封装20的电力变换装置100能够提高电力密度。在将第4半导体元件21和第5半导体元件22单独设置的情况下,在各自中使用散热器等散热部件,但如实施方式那样通过使用第2半导体封装20,从而能够将散热部件也设为1个,实施方式的电力变换装置100有助于降低部件成本、安装成本。通过在电力变换装置100使用第1半导体封装10和第2半导体封装20这两者,从而更有助于成本的削减。第2半导体封装20除了引线框p1在2个半导体元件之间与两个源极连接这一点以外,能够自由地设计第2半导体封装20。

131.在使第4半导体元件21和第5半导体元件22互补地接通-断开的情况下,若第4半导体元件21的面积和第5半导体元件22的面积为相同程度,则流过2个元件的电流为相同程度,2个元件的温度上升成为相同程度,元件不易破坏。即,优选第4半导体元件21的元件区域面积和第5半导体元件22的元件区域的面积为相同程度。具体地说,第4半导体元件21的面积(元件区域的面积)优选为第5半导体元件22的面积(元件区域的面积)的50%以上且150%以下,更优选为75%以上且125%以下,进一步优选为90%以上且110%以下。

132.在第2实施方式中,能够使用收容有开关元件q1及开关元件q2的第3半导体封装30。第3半导体封装30收容第3半导体元件组。在第3半导体封装30的开关元件q1和开关元件q2为p型mosfet的情况下,在第3半导体封装30中采用第2半导体封装20的结构,被源极电极a1及源极电极a2夹着的引线框与高电位侧输入端子v

in1

连接。

133.在图19-22中示出第3半导体封装30的示意图。图19的示意图(x-y面)是从第2半导体封装20的端子侧即底面侧观察的示意图。另外,在图19的示意图中还示出了从一部分的底面观察不到的部件等。图20是图19的e-e’剖面(y-z面)的剖视示意图。图21是图19的f-f’剖面(x-z面)的剖视示意图。图22是图19的g-g’剖面(x-z面)的剖视示意图。

134.在第3半导体元件组中包含第7半导体元件31和第8半导体元件32。第3半导体元件

组为mosfet或igbt。以下,主要以第3半导体元件组为mosfet的情况为例进行说明。关于第3半导体元件组为igbt的情况也进行一部分说明。在第3半导体元件组为mosfet的情况下,第2半导体元件组也为mosfet。在第3半导体元件组为igbt的情况下,第2半导体元件组也为igbt。

135.第3半导体封装30将开关元件q1作为第7半导体元件31进行收容,将开关元件q1作为第8半导体元件32进行收容,或将开关元件q1作为第7半导体元件31进行收容,将开关元件q2作为第8半导体元件32进行收容。第3半导体封装30具有第5非共用端子33、第6非共用端子34、第3共用端子35、栅极端子36、栅极端子37。第3共用端子35与初级侧电路x1的高电位侧输入端子v

in1

电连接。

136.第3半导体封装30由于是与第1半导体封装10和第2半导体封装20类似的装置,因此将其说明省略一部分。在第1半导体封装10、第2半导体封装20及第3半导体封装30中,一部分的部件的附图标记或一部分的部件的名称是共用的。关于第3半导体封装30,对与第1半导体封装10和/或第2半导体封装20共用的内容,省略其说明及对应的示意图。第3半导体封装30与第1半导体封装10及第2半导体封装20的不同点在于,漏极侧对置。

137.第3半导体封装30内的第7半导体元件31和第8半导体元件32以在电气上并联地电连接的方式层叠。

138.第7半导体元件31具有源极电极a1、漏极电极b1及栅极电极c1。另外,第8半导体元件32具有源极电极a2、漏极电极b2及栅极电极c2。

139.第7半导体元件31的源极与第7半导体元件31的源极电连接,设置于第7半导体元件31的表面(第1面s1)。第8半导体元件32的源极电极a2与第8半导体元件32的源极电连接,设置于第8半导体元件32的表面(第1面s1)。

140.第7半导体元件31的漏极电极b1与第7半导体元件31的漏极电连接,设置于第7半导体元件31的表面(第2面s2)。第7半导体元件31的第2面s2是第7半导体元件31的与第1面s1相反侧的表面。第8半导体元件32的漏极电极b2与第8半导体元件32的漏极电连接,设置于第8半导体元件32的表面(第2面s2)。第8半导体元件32的第2面s2是第8半导体元件32的与第1面s1相反侧的表面。

141.第7半导体元件31的栅极电极c1与第7半导体元件31的栅极电连接,设置于第7半导体元件31的表面(第1面s1)。第8半导体元件32的栅极电极c2与第8半导体元件32的栅极电连接,设置于第8半导体元件32的表面(第1面s1)。

142.在第7半导体元件31及第8半导体元件32的各电极包含电极焊盘或电极焊盘及焊料等导电性接合部件。

143.第7半导体元件31的源极电极a1与第8半导体元件32的源极电极a2面向第3半导体封装30的外侧而朝向相反方向。

144.第7半导体元件31的漏极电极b1与第8半导体元件32的漏极电极b2在第7半导体元件31和第8半导体元件32的层叠方向上对置而电连接。

145.第7半导体元件31的第2面s2与第8半导体元件32的第2面s2对置,即第7半导体元件31的漏极电极b1与第8半导体元件32的漏极电极b2面向第3半导体封装30的内侧而相面对。

146.如图20~图23所示,第7半导体元件31的源极电极a1位于第3半导体封装30的底面

侧。源极电极a1与引线框p1相接,优选直接相接。引线框p1与第7半导体元件31的源极连接,但不与第2半导体元件12的源极连接。如图20~图23所示,引线框p1优选在第3半导体封装30的底面侧露出。如图20~图23所示,引线框p1与在半导体封装10的侧面的外侧露出的第5非共用端子33连接。

147.如图20~图23所示,第8半导体元件32的源极电极a2位于第3半导体封装30的上表面侧。即,漏极电极b1及漏极电极b2位于源极电极a1与源极电极a2之间。源极电极a2与引线框p2相接,优选直接相接。引线框p2与第8半导体元件32的源极连接,但不与第7半导体元件31的引线框p1连接。如图21所示,引线框p2朝向第3半导体封装30的底面方向折弯而延伸。引线框p1独立于引线框p2。引线框p2与在第3半导体封装30的侧面的外侧露出的第6非共用端子34连接。第5非共用端子33独立于第6非共用端子34。

148.如图20~图23所示,引线框p1在相对于引线框p2偏移60

°

的方向上延伸。另外,如图20~图23所示,引线框p2相对于引线框q1在相反方向上延伸。

149.如图21~图23的剖视图所示,在漏极电极b1与漏极电极b2之间设置有引线框q1(第3引线框)。引线框q1与第7半导体元件31的漏极和第8半导体元件32的漏极这两者连接。引线框q1与漏极电极b1及漏极电极b2相接,优选直接相接。如图21所示,引线框q1朝向第3共用端子35延伸。引线框q1的一部分延伸至第3半导体封装30的底面侧为止。如图20-21所示,引线框q1与在第3半导体封装30的侧面的外侧露出的第3共用端子35连接。

150.如图20、图22所示,第7半导体元件31的栅极电极c1与第7半导体元件31的第1面s1的源极电极a1邻接。栅极电极c1与引线框r1相接,优选直接相接。引线框r1与第7半导体元件31的栅极连接,但不与第8半导体元件32的栅极连接。如图20、22所示,引线框r1沿第3半导体封装30的底面侧延伸。引线框r1与在第3半导体封装30的侧面外侧露出的栅极端子36连接。在栅极端子36连接有未图示的栅极驱动器。第7半导体元件31的动作由栅极驱动器进行控制。

151.如图20、图23所示,第8半导体元件32的栅极电极c2与第8半导体元件32的第1面s1的源极电极a2邻接。栅极电极c2与引线框r2相接,优选直接相接。引线框r2与第8半导体元件32的栅极连接,但不与第7半导体元件31的栅极连接。如图23所示,引线框r2从第3半导体封装30的上表面侧向底面侧折弯而延伸。引线框r2与在第3半导体封装30的侧面外侧露出的栅极端子37连接。在栅极端子37连接有未图示的栅极驱动器。第8半导体元件32的动作由栅极驱动器进行控制。

152.如图20、图22、图23所示,引线框r1与引线框r2并行地排列而延伸。另外,如图20、图22、图23所示,引线框r1及引线框r2在相对于引线框q1的与引线框p1相反侧,在相对于引线框q1偏移了90

°

的方向上延伸。

153.在第3半导体元件组为mosfet的情况下,具有使第7半导体元件31的漏极电极b1及第8半导体元件32的漏极电极b2对置而电连接的引线框q1(第3引线框)。第7半导体元件31的漏极电极b1及第8半导体元件32的漏极电极b2优选在第7半导体元件31和第8半导体元件32的层叠方向上对置。另外,第3半导体封装30的引线框q1的面向第7半导体元件31的面与第7半导体元件31的漏极电极b1直接连接。第3半导体封装30的引线框q2的面向第8半导体元件32的面与第8半导体元件32的漏极电极b2直接连接。

154.在第3半导体元件组为igbt的情况下,具有使第7半导体元件31的集电极电极b1及

第8半导体元件32的集电极电极b2对置而电连接的引线框q1(第3引线框)。第7半导体元件31的集电极电极b1及第8半导体元件32的集电极电极b2优选在第7半导体元件31和第8半导体元件32的层叠方向上对置。另外,第3半导体封装30的引线框q1的面向第7半导体元件31的面与第7半导体元件31的集电极电极b1直接连接。第3半导体封装30的引线框q1的面向第8半导体元件32的面与第8半导体元件32的集电极电极b2直接连接。

155.第3半导体封装30以夹着引线框q1的方式设置有漏极电极b1和漏极电极b2。由此,能够兼顾使第7半导体元件31和第8半导体元件32层叠和将两个半导体元件的漏极通过1个引线框q1进行连接。与将在dc-dc转换器的初级侧电路x1设置的2个开关元件单独设置的情况相比,能够在更少的面积中设置第3半导体封装30,减小安装面积,有助于电力变换装置100的小型化。即,使用了第3半导体封装30的电力变换装置100能够提高电力密度。在将第7半导体元件31和第8半导体元件32单独设置的情况下,在各自中使用散热器等散热部件,但通过如实施方式那样使用第3半导体封装30,能够将散热部件也设为1个,实施方式的电力变换装置100有助于降低部件成本、安装成本。通过将第1半导体封装10、第2半导体封装20及第3半导体封装30全部用于电力变换装置100,从而更有助于成本的削减。第3半导体封装30除了引线框q1在2个半导体元件之间与两个漏极连接这一点以外,能够自由地设计第3半导体封装30。

156.在使第7半导体元件31和第8半导体元件32互补地接通-断开的情况下,若第7半导体元件31的面积和第8半导体元件32的面积为相同程度,则流过2个元件的电流为相同程度,2个元件的温度上升成为相同程度,元件不易破坏。即,优选第7半导体元件31的元件区域面积和第8半导体元件32的元件区域的面积为相同程度。具体地说,第7半导体元件31的面积(元件区域的面积)优选为第8半导体元件32的面积(元件区域的面积)的50%以上且150%以下,更优选为75%以上且125%以下,进一步优选为90%以上且110%以下。

157.(第3实施方式)

158.第3实施方式涉及半导体装置,具体地说,涉及电力变换装置。第3实施方式涉及具有半桥型dc-dc转换器的电力变换装置。第3实施方式的电力变换装置100在次级侧电路x2包含第1半导体封装10。第3实施方式的电力变换装置100以第1半导体元件11及第2半导体元件12为mosfet的情况为例进行说明,但第1半导体元件11及第2半导体元件12也可以是igbt或二极管。在第3实施方式中,优选使用在第1实施方式及第2实施方式中说明过的第1半导体封装10。

159.在图24中示出第3实施方式的半桥型dc-dc转换器的电路图。图24所示的电路图是半桥型dc-dc转换器的电路图的一个例子,电路结构能够适当变更。

160.在初级侧电路x1包含开关元件q9-q10、电容器c4-c5,与第3变压器tr3的初级线圈连接。使开关元件q9和开关元件q10交替地接通-断开。初级侧电路x1的各开关元件为mosfet或igbt。在各开关元件连接有栅极驱动器或igbt驱动器,但省略图示。

161.在次级侧电路x2包含开关元件q11-q12、线圈l3、电容器c6,与第3变压器tr3的次级线圈连接。在次级侧电路x2中,使开关元件q11和开关元件q12交替地接通-断开。

162.在半桥型dc-dc转换器中,优选使用作为第1半导体元件11而收容有开关元件q11及作为第2半导体元件12而收容有开关元件q12、或作为第1半导体元件11而收容有开关元件q12及作为第2半导体元件12而收容有开关元件q11的第1半导体封装10。在开关元件q11

及开关元件q12为mosfet的情况下,能够采用2个开关元件q11、q12的源极与低电位侧输出端子v

out2

连接且将这些开关元件的源极端子共用化而成的第1半导体封装10。

163.开关元件q13的源极侧也与低电位侧输出端子v

out2

连接。因此,在第1半导体封装10中,在开关元件q11(第1半导体元件11)、开关元件q12(第2半导体元件12)的基础上,能够收容开关元件q13作为第3半导体元件。优选第3半导体元件的源极电极也与引线框p1连接,与第1共用端子13电连接。

164.在第3实施方式中,通过采用第1半导体封装10,实施方式的电力变换装置100有助于降低部件成本、安装成本。第1半导体封装10除了引线框p1在2个半导体元件之间与两个源极连接这一点以外,能够自由地设计半导体封装10。

165.(第4实施方式)

166.第4实施方式涉及半导体装置,具体地说,涉及电力变换装置。第5实施方式涉及具有全桥型dc-dc转换器的电力变换装置。第4实施方式的电力变换装置100在次级侧电路x2包含第1半导体封装10。另外,优选在初级侧电路x1使用第2半导体封装20及第3半导体封装30。第4实施方式的电力变换装置100以第1半导体元件11及第2半导体元件12为mosfet的情况为例进行说明,但第1半导体元件11及第2半导体元件12也可以为igbt或二极管。在第3实施方式中,优选使用在第1实施方式及第2实施方式中说明过的第1半导体封装10。在第3实施方式中,优选使用在第2实施方式中说明的第2半导体封装20和/或第3半导体封装30。

167.在图25中示出第3实施方式的全桥型dc-dc转换器的电路图。图25所示的电路图是全桥型dc-dc转换器的电路图的一个例子,电路结构能够适当变更。

168.在初级侧电路x1中包含开关元件q14-q17,与第4变压器tr4的初级线圈连接。使开关元件q14、q16和开关元件q15、q17交替地接通-断开。初级侧电路x1的各开关元件为mosfet或igbt。在各开关元件连接有栅极驱动器或igbt驱动器,但省略图示。

169.在次级侧电路x2中包含开关元件q18-q21、线圈l4、电容器c1,与第4变压器tr4的次级线圈连接。在次级侧电路x2中,使开关元件q18、q20和开关元件q19、q20交替地接通-断开。

170.在全桥型dc-dc转换器中,优选使用作为第1半导体元件11而收容有开关元件q20及作为第2半导体元件12而收容有开关元件q21、或作为第1半导体元件11而收容有开关元件q21及作为第2半导体元件12而收容有开关元件q20的第1半导体封装10。在开关元件q20及开关元件q21为mosfet的情况下,能够采用2个开关元件q20、q21的源极与低电位侧输出端子v

out2

连接且将这些开关元件的源极端子共用化而成的第1半导体封装10。

171.在全桥型dc-dc转换器中,优选使用作为第4半导体元件21而收容有开关元件q16及作为第5半导体元件22而收容有开关元件q17、或作为第4半导体元件21而收容有开关元件q17及作为第5半导体元件22而收容有开关元件q16的第2半导体封装20。在开关元件q16及开关元件q17为mosfet的情况下,能够采用2个开关元件q16、q17的源极与低电位侧输入端子v

in2

连接且将这些开关元件的源极端子共用化而成的第2半导体封装20。

172.在全桥型dc-dc转换器中,优选使用作为第7半导体元件31而收容有开关元件q14及作为第8半导体元件32而收容有开关元件q15、或作为第7半导体元件31而收容有开关元件q15及作为第8半导体元件32而收容有开关元件q14的第3半导体封装30。在开关元件q14及开关元件q15为mosfet的情况下,能够采用2个开关元件q14、q15的源极与高电位侧输入

端子v

in1

连接且将这些开关元件的漏极端子共用化而成的第3半导体封装30。

173.在第4实施方式中,能够使用收容有开关元件q18及开关元件q19的第4半导体封装40。第4半导体封装40收容第4半导体元件组。

174.在图26示出第4半导体封装40的示意图。图26的示意图(x-y面)是从第4半导体封装40的端子侧即底面侧观察的示意图。另外,在图26的示意图中还示出从一部分的底面观察不到的部件等。图26的e-e’剖面(y-z面)的剖视示意图相当于图20的e-e’剖面(y-z面)的剖视示意图。图26的f-f’剖面(y-z面)的剖视示意图相当于图21的f-f’剖面(x-z面)的剖视示意图。图26的g-g’剖面(y-z面)的剖视示意图相当于图22的g-g’剖面(x-z面)的剖视示意图。

175.在第4半导体元件组中包含第9半导体元件41和第10半导体元件42。第4半导体元件组为mosfet、igbt或二极管。在第1半导体元件组为mosfet的情况下,第4半导体元件组也为mosfet。在第1半导体元件组为igbt的情况下,第4半导体元件组也为igbt。在第1半导体元件组为二极管的情况下,第4半导体元件组也为二极管。以下,主要以第4半导体元件组为mosfet的情况为例进行说明。关于第4半导体元件组为igbt、二极管的情况,也进行一部分说明。

176.第4半导体封装40将开关元件q18作为第9半导体元件41进行收容,将开关元件q19作为第10半导体元件42进行收容,或将开关元件q19作为第9半导体元件41进行收容,将开关元件q18作为第10半导体元件42进行收容。第4半导体封装40具有第7非共用端子43、第8非共用端子44、第4共用端子45、栅极端子46、栅极端子47。第4共用端子45与次级侧电路x2的高电位侧输出端子v

out1

电连接。

177.第4半导体封装40的第9半导体元件41相当于第3半导体封装30的第7半导体元件31。第4半导体封装40的第10半导体元件42相当于第3半导体封装30的第8半导体元件32。第4半导体封装40的第7非共用端子43、第8非共用端子44、第4共用端子45分别相当于第3半导体封装30的第5非共用端子33、第6非共用端子34、第3共用端子35。

178.第3半导体封装30和第4半导体封装40是相同的装置,因此将其说明省略一部分。在第1半导体封装10至第4半导体封装40中,一部分的部件的附图标记或一部分的部件的名称是共用的。关于第4半导体封装40,对与第3半导体封装30共用的内容,省略其说明及对应的示意图。

179.在第9半导体元件41与第10半导体元件42之间设置有引线框q1(第4引线框)。第4共用端子45与引线框q1连接。第7非共用端子43与引线框p1连接。第8非共用端子44与引线框p2连接。栅极端子46与引线框r1连接。栅极端子47与引线框r2连接。

180.在第4半导体元件组为mosfet的情况下,具有使第9半导体元件41的漏极电极b1及第10半导体元件42的漏极电极b2对置而电连接的引线框q1(第4引线框)。第9半导体元件41的漏极电极b1及第10半导体元件42的漏极电极b2优选在第9半导体元件41和第10半导体元件42的层叠方向(z方向)上对置。另外,第4半导体封装40的引线框q1的面向第9半导体元件41的面与第9半导体元件41的漏极电极b1直接连接。第4半导体封装40的引线框q1的面向第10半导体元件42的面与第10半导体元件42的漏极电极b2直接连接。

181.在第4半导体元件组为igbt的情况下,具有使第9半导体元件41的集电极电极b1及第10半导体元件42的集电极电极b2对置而电连接的引线框q1(第4引线框)。第9半导体元件

41的集电极电极b1及第10半导体元件42的集电极电极b2优选在第9半导体元件41和第10半导体元件42的层叠方向上对置。另外,第4半导体封装40的引线框q1的面向第9半导体元件41的面与第9半导体元件41的集电极电极b1直接连接。第4半导体封装40的引线框q1的面向第10半导体元件42的面与第10半导体元件42的集电极电极b2直接连接。

182.第4半导体封装40以夹着引线框q1的方式设置有漏极电极b1和漏极电极b2。由此,能够兼顾使第9半导体元件41和第10半导体元件42层叠和将两个半导体元件的漏极通过1个引线框q1进行连接。与将在dc-dc转换器的初级侧电路x1设置的2个开关元件单独设置的情况相比,能够在更少的面积中设置第3半导体封装30,减小安装面积,有助于电力变换装置100的小型化。即,使用了第4半导体封装40的电力变换装置100能够提高电力密度。在将第9半导体元件41和第10半导体元件42单独设置的情况下,在各自中使用散热器等散热部件,但通过如实施方式那样使用第4半导体封装40,能够将散热部件也设为1个,实施方式的电力变换装置100有助于降低部件成本、安装成本。通过将第1半导体封装10、第2半导体封装20及第3半导体封装30全部用于电力变换装置100,从而更有助于成本的削减。第4半导体封装40除了引线框q1在2个半导体元件之间与两个漏极连接这一点以外,能够自由地设计第4半导体封装40。

183.在使第9半导体元件41和第10半导体元件42互补地接通-断开的情况下,若第9半导体元件41的面积和第10半导体元件42的面积为相同程度,则流过2个元件的电流为相同程度,2个元件的温度上升成为相同程度,元件不易破坏。即,优选第9半导体元件41的元件区域面积和第10半导体元件42的元件区域的面积为相同程度。具体地说,第9半导体元件41的面积(元件区域的面积)优选为第10半导体元件42的面积(元件区域的面积)的50%以上且150%以下,更优选为75%以上且125%以下,进一步优选为90%以上且110%以下。

184.在第4实施方式中,也能够使用p型mosfet、p沟道型mosfet。例如,在全部半导体元件中使用了p型mosfet的情况下,通过在第1半导体封装10采用第4半导体封装40的结构、使被漏极电极b1及漏极电极b2夹着的引线框与低电位侧输出端子v

out2

连接、在第2半导体封装20采用第3半导体封装40的结构、使被漏极电极b1及漏极电极b2夹着的引线框与低电位侧输入端子v

in2

连接、在第3半导体封装30采用第2半导体封装20的结构、使被源极电极a1及源极电极a2夹着的引线框与高电位侧输入端子v

in1

连接、在第4半导体封装40采用第1半导体封装10的结构、使被源极电极a1及源极电极a2夹着的引线框与高电位侧输出端子v

out1

连接,由此能够将本发明的半导体封装用于电力变换装置100。

185.(第5实施方式)

186.第5实施方式涉及半导体装置,具体地说,涉及具有逆变器电路的电力变换装置或信号放大器。电力变换装置更具体地说是逆变器。在图27中示出实施方式的半导体装置200的示意性电路图。在半导体装置200为信号放大器的情况下,还具有供放大的信号输入的信号输入端子。在图27的示意性电路图中包含收容有第11半导体元件52和第12半导体元件52的第5半导体封装50。

187.第5半导体封装50收容有包含第11半导体元件51及第12半导体元件52的第5半导体元件组。在第5半导体封装50中,第11半导体元件51及第12半导体元件52层叠,第5半导体元件组为igbt、双极型晶体管、mosfet或fet,第11半导体元件51为p沟道型的半导体元件,第12半导体元件52为n沟道型的半导体元件,第5半导体元件组为igbt或双极型晶体管的情

况下,第11半导体元件51的集电极电极与第12半导体元件52的集电极电极在第11半导体元件51及第12半导体元件52的层叠方向上对置而电连接,在第5半导体元件组为mosfet或fet的情况下,使第11半导体元件51的漏极电极与第12半导体元件52的漏极电极在第11半导体元件51及第12半导体元件52的层叠方向上对置而电连接的第5引线框包含在第5半导体封装50中。第5引线框位于第11半导体元件51与第12半导体元件52之间。

188.半导体装置200具有高电位侧输入端子v

in1

和低电位侧输入端子v

in2

,与dc电源连接。对第5半导体封装50施加dc电压,通过第5半导体封装50变换后的ac电流或放大后的信号从输出端子out输出。

189.第5半导体封装50收容有包含第11半导体元件51和第12半导体元件52的第5半导体元件组。在第5半导体封装50中也可以包含除了第11半导体元件51和第12半导体元件52以外的半导体元件。第5半导体封装50具有第5共用端子55。在第5半导体封装50中包含与第11半导体元件51连接的第9非共用端子53和与第12半导体元件52连接的第10非共用端子54。

190.第11半导体元件51及第12半导体元件52是两者都为双极型晶体管、两者都为igbt、两者都为mosfet或两者都为fet的任一种。

191.在将第5半导体封装50收容于igbt模块和/或运算放大器的情况下,能够省略密封材料m。

192.第11半导体元件51为p沟道型的半导体元件,第12半导体元件52为n沟道型的半导体元件。第11半导体元件51和第12半导体元件52优选为互补对。

193.在图28~图31中示出第5半导体封装50的示意图。将第11半导体元件51及第12半导体元件52的层叠方向设为z方向,将与z方向垂直的方向设为x方向、y方向。x方向与y方向正交。第11半导体元件51的面向第12半导体元件52的面优选与x-y面平行。另外,第12半导体元件52的面向第11半导体元件51的面优选与x-y面并行。

194.在图28的示意图中,第11半导体元件51位于下侧,第12半导体元件52位于上侧,但也可以是第11半导体元件51位于上侧、第12半导体元件52位于下侧的第5半导体封装50。

195.图28的示意图(x-y面)是从第5半导体封装50的端子侧即底面侧观察的示意图。另外,在图28的剖视图中还示出了从一部分的底面观察不到的部件等。图9是图29的h-h’剖面(y-z面)的剖视示意图。图30是图2的i-i’剖面(y-z面)的剖视示意图。图31是图28的j-j’剖面(x-z面)的剖视示意图。

196.第5半导体封装50内的第11半导体元件51和第12半导体元件52以在电气上串联电连接的方式层叠。

197.第5半导体封装50由于是与第3半导体封装30和第4半导体封装40相同的装置,因此将其说明省略一部分。在第1半导体封装10至第4半导体封装40中,一部分的部件的附图标记或一部分的部件的名称是共用的。关于第5半导体封装50,对与第3半导体封装30及第4半导体封装40共用的内容,省略其说明及对应的示意图。

198.第5半导体封装50的第11半导体元件51相当于第3半导体封装30的第7半导体元件31。第5半导体封装50的第12半导体元件52相当于第3半导体封装30的第8半导体元件32。第5半导体封装50的第9非共用端子53、第10非共用端子54、第5共用端子55分别相当于第3半导体封装30的第5非共用端子33、第6非共用端子34、第3共用端子35。

199.在第11半导体元件51与第12半导体元件52之间设置有引线框q1(第5引线框)。第5共用端子55与引线框q1连接。第9非共用端子53与引线框p1连接。第10非共用端子54与引线框p2连接。基极端子56与引线框r1连接。基极端子57与引线框r2连接。

200.在第5半导体元件组为igbt或双极型晶体管的情况下,具有使第11半导体元件51的集电极电极b1及第12半导体元件52的集电极电极b2对置而电连接的引线框q1(第5引线框)。第11半导体元件51的集电极电极b1及第12半导体元件52的集电极电极b2优选在第11半导体元件51和第12半导体元件52的层叠方向上对置。另外,第5半导体封装50的引线框q1的面向第11半导体元件51的面与第11半导体元件51的集电极电极b1直接连接。第5半导体封装50的引线框q1的面向第12半导体元件52的面与第12半导体元件52的集电极电极b2直接连接。

201.在第5半导体元件组为mosfet或fet的情况下,具有使第11半导体元件51的漏极电极b1及第12半导体元件52的漏极电极b2对置而电连接的引线框q1(第5引线框)。第11半导体元件51的漏极电极b1及第12半导体元件52的漏极电极b2优选在第11半导体元件51和第12半导体元件52的层叠方向(z方向)上对置。另外,第5半导体封装50的引线框q1的面向第11半导体元件51的面与第11半导体元件51的漏极电极b1直接连接。第5半导体封装50的引线框q1的面向第10半导体元件42的面与第10半导体元件42的漏极电极b2直接连接。

202.第5半导体封装50以夹着引线框q1的方式设置有漏极电极b1和漏极电极b2。由此,能够兼顾使第11半导体元件51和第12半导体元件52层叠和将两个半导体元件的漏极通过1个引线框q1进行连接。与将2个开关元件单独设置的情况相比,能够在更少的面积中设置第5半导体封装50,减小安装面积,有助于半导体装置200的小型化。即,使用了第5半导体封装50的半导体装置200能够提高电力密度。在将第11半导体元件51和第12半导体元件52单独设置的情况下,在各自中使用散热器等散热部件,但通过如实施方式那样使用第5半导体封装50,能够将散热部件也设为1个,实施方式的电力变换装置100有助于降低部件成本、安装成本。第5半导体封装50除了引线框q1在2个半导体元件之间与两个漏极连接这一点以外,能够自由地设计第4半导体封装40。

203.在使第11半导体元件51和第12半导体元件52接通-断开的情况下,若第11半导体元件51的面积和第12半导体元件52的面积为相同程度,则流过2个元件的电流为相同程度,2个元件的温度上升成为相同程度,元件不易破坏。即,优选第11半导体元件51的元件区域面积和第12半导体元件52的元件区域的面积为相同程度。具体地说,第11半导体元件51的面积(元件区域的面积)优选为第12半导体元件52的面积(元件区域的面积)的50%以上且150%以下,更优选为75%以上且125%以下,进一步优选为90%以上且110%以下。

204.(第6实施方式)

205.第6实施方式涉及半导体装置,具体地说,涉及电力变换装置。第6实施方式涉及具有逆变器的电力变换装置。第6实施方式的电力变换装置200包含第5半导体封装50。第6实施方式的电力变换装置200以第11半导体元件51及第12半导体元件52为igbt的情况为例进行说明。

206.在图32中示出第6实施方式的3相逆变器的电路图。图32所示的电路图是3相逆变器的电路图的一个例子,电路结构能够适当变更。

207.在图32所示的3相逆变器电路中包含开关元件q22-q27、二极管d6-d11。二极管

与各开关元件并联连接。在各开关元件连接有栅极驱动器或igbt驱动器,但省略图示。

208.由于是3相逆变器,因此p沟道型的开关元件和n沟道型的开关元件的对(pair)包含3个,分别与输出端子v

out3

、输出端子v

out4

、输出端子v

out5

连接。各输出端子例如与3相电动机连接。

209.在3相逆变器中,优选使用作为第11半导体元件51而收容有开关元件q22及作为第12半导体元件52而收容有开关元件q23的第5半导体封装50。

210.在3相逆变器中,优选使用作为第11半导体元件51而收容有开关元件q24及作为第12半导体元件52而收容有开关元件q25的第5半导体封装50。

211.在3相逆变器中,优选使用作为第11半导体元件51而收容有开关元件q26及作为第12半导体元件52而收容有开关元件q27的第5半导体封装50。

212.例如,能够采用开关元件q22及开关元件q23的集电极与输出端子v

out3

连接且将这些开关元件的集电极端子共用化而成的第5半导体封装50。

213.在第5半导体封装50中还能够收容二极管。通过将多个第5半导体封装50收容于igbt模块,有助于igbt模块的小型化。通过采用第5半导体封装50,有助于采用了第5半导体封装50的装置的小型化,有助于降低部件成本及安装成本。

214.(第7实施方式)

215.第7实施方式涉及半导体装置,具体地说,涉及信号放大器。第7实施方式的信号放大器300包含第5半导体封装50。第7实施方式的信号放大器300以第11半导体元件51及第12半导体元件52为双极型晶体管的情况为例进行说明。

216.在图33中示出第7实施方式的信号放大器300的电路图。图33所示的电路图是信号放大器300的电路图的一个例子,电路结构能够适当变更。

217.在图33所示的信号放大器300的电路包含开关元件q28-q29、二极管d12-d13及电阻r1-r6。在信号放大器300,在v-gnd间连接dc电源。从信号放大器300的输入端子in输入的信号由信号放大器300放大,从输出端子out输出。

218.在信号放大器300中,优选使用作为第11半导体元件51而收容有开关元件q29及作为第12半导体元件52而收容有开关元件q30的第5半导体封装50。

219.例如,能够采用开关元件q29及开关元件q30的集电极与输出端子out连接且将这些开关元件的集电极端子共用化而成的第5半导体封装50。

220.通过采用第5半导体封装50,有助于采用了第5半导体封装50的装置的小型化,有助于降低部件成本及安装成本。

221.(第8实施方式)

222.第8实施方式涉及半导体装置,具体地说,涉及信号放大器。第8实施方式的信号放大器400包含第5半导体封装50。第8实施方式的电力变换装置200以第11半导体元件51及第12半导体元件52为双极型晶体管的情况为例进行说明。

223.在图34中示出第8实施方式的信号放大器500的电路图。信号放大器500更具体地说是运算放大器。图34所示的电路图是信号放大器500的电路图的一个例子,电路结构能够适当变更。

224.在图34所示的信号放大器500的电路中包含开关元件q31-q43、电容器c6。在信号放大器500中,在v-gnd间连接dc电源。从信号放大器500的输入端子in

+

及in

-

输入的信号

由信号放大器500放大,从输出端子out输出。

225.在信号放大器500中,优选使用作为第11半导体元件51而收容有开关元件q42及作为第12半导体元件52而收容有开关元件q43的第5半导体封装50。

226.例如,能够采用开关元件q42及开关元件q43的集电极与输出端子out连接且将这些开关元件的集电极端子共用化而成的第5半导体封装50。

227.通过采用第5半导体封装50,有助于采用了第5半导体封装50的装置的小型化,有助于降低部件成本及安装成本。

228.对本发明的几个实施方式进行了说明,但这些实施方式是作为例子提示出的,并不是要对发明的范围进行限定。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围,能够进行各种省略、置换、变更。这些实施方式以及其变形包含于发明的范围及主旨,并且包含于权利要求书所记载的发明和其等同的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1