1.实施方式涉及传感器,并且具体地,涉及摄影传感器以及叠层图像传感器。

背景技术:2.摄影传感器包括感光点的矩阵。感光点允许将电磁辐射(uv、可见光或ir)转换为模拟电信号。

3.感光点在矩阵中以行和列的方式布置。矩阵的感光点通常通过电容性隔离沟槽(在本领域中也称为电容性深沟槽隔离(cdti)沟槽)彼此分离。

4.感光点矩阵在其制造过程中会经受机械应力。具体地,在感光点矩阵的制造过程中,cdti沟槽通过沉积由非晶硅制成的材料而被填充。由非晶硅制成的该材料在高温退火过程中转变为多晶硅。该转变引起材料收缩,该收缩转化为拉伸机械应力。

5.这些机械应力会导致感光点矩阵变形。具体地,感光点矩阵承受的机械应力可以使其弯曲,从而在感光点矩阵的表面上形成凹陷。

6.因此,感光点矩阵的表面是弯曲的,而不是平坦的。因此,执行用于在感光点矩阵的凹陷表面上机械-化学抛光的方法会在感光点矩阵的表面上留下残余物。这些残余物可能使感光点矩阵的感光点短路。

7.此外,特定摄影传感器被布置在几个叠加的层上。具有自由面的第一层包括感光点矩阵。第二层被布置在第一层下面,即与第一层的自由面相对,该第二层包括用于处理由感光点矩阵产生的信号的电路。摄影传感器可以在第二层下面包括其它层。

8.第一层可以通过直接粘合(没有粘合剂)的方法组装至第二层,该方法是在分子粘合后进行热退火以固化氧化物-氧化物粘合界面的方法。

9.具体地,第一层的与其自由面相对的面被组装至第二层。第一层的与其自由面相对的这个面可以在感光点矩阵处具有凹陷。

10.当感光点矩阵是凹陷的时,第一层与第二层之间的组件可能具有较低的性能。

11.具体地,第一层与第二层之间的组件可以在感光点矩阵处具有结合空隙。这些结合空隙可能导致组件在粘合两个层之后的减薄方法期间、或者在两个层之间的电中断之后破裂。

12.具体地,这些结合空隙由感光点矩阵边缘处的感光点矩阵曲率而导致。感光点矩阵的曲率越大,结合空隙就越大。

13.已经注意到,感光点矩阵的曲率是由感光点矩阵与围绕其的半导体衬底之间的硅密度的骤变所引起的。

14.因此,对于这种感光点矩阵,第一层的拓扑结构不适合获得在第一层与第二层之间令人满意的组件。

15.因此,需要提出允许降低感光点矩阵曲率的解决方案。

技术实现要素:16.根据本实用新型,可以克服上述技术问题,有助于实现以下优点:降低感光点矩阵的曲率。

17.根据一个方面,提出了一种传感器,包括包含半导体衬底的半导体板,所述半导体衬底包括:感光点矩阵,每个感光点由隔离沟槽界定;以及外围区,直接围绕感光点矩阵延伸,外围区具有的多晶硅密度介于感光点矩阵边缘处的多晶硅密度与围绕外围区的多晶硅密度之间。

18.根据某些实施例,传感器包括:半导体衬底;所述半导体衬底中的感光点的矩阵,所述矩阵的每个感光点由包括多晶硅的隔离沟槽界定;以及所述半导体衬底的外围区,直接围绕感光点的所述矩阵延伸,所述外围区包括由包含多晶硅的隔离沟槽界定的虚设感光点;其中所述外围区中的多晶硅密度低于在感光点的所述矩阵的外边缘处的多晶硅密度、并且高于在围绕所述外围区的所述半导体衬底的范围中的多晶硅密度。

19.外围区允许从感光点矩阵开始逐渐降低多晶硅密度。

20.因此,机械应力从感光点矩阵开始逐渐下降。

21.因此,外围区允许降低感光点矩阵边缘处的曲率。

22.这种半导体板可以形成背照式多层摄影传感器的层。具体地,因此半导体板可以粘合至半导体衬底的另一个板。

23.在有利的实施方式中,外围区包括围绕感光点矩阵的外围隔离沟槽,外围区的外围隔离沟槽以大于矩阵中的感光点宽度的距离与感光点矩阵的所述外边缘分离。

24.这种外围区允许逐渐降低围绕感光点矩阵的多晶硅密度。

25.有利地,外围区包括形成在衬底中并且由隔离沟槽彼此界定的一组虚设感光点。因此,虚设感光点具有的宽度大于感光点矩阵中的感光点宽度。

26.根据某些实施例,外围区包括围绕感光点矩阵的外围隔离沟槽,外围区的外围隔离沟槽以大于矩阵中的感光点的宽度的距离与感光点矩阵的外边缘分离。

27.优选地,外围区包括围绕矩阵延伸的一系列外围隔离沟槽,一系列外围隔离沟槽中的两个连续外围隔离沟槽之间的距离大于矩阵中的感光点宽度,两个连续外围隔离沟槽之间的该距离从最靠近感光点矩阵的外边缘的外围隔离沟槽开始增加。

28.或者,外围区包括围绕感光点矩阵的外围隔离沟槽,外围区的外围隔离沟槽在小于界定矩阵的感光点的隔离沟槽的深度的一个深度上延伸。

29.这种外围区还允许逐渐降低围绕感光点矩阵的多晶硅密度。

30.有利地,外围区包括形成在衬底中并且由隔离沟槽彼此界定的一组虚设感光点。因此外围区的隔离沟槽在一个深度上延伸,该深度小于界定感光点矩阵的感光点的隔离沟槽的深度。

31.优选地,外围区包括围绕矩阵延伸的一系列外围隔离沟槽,这些外围隔离沟槽的深度和这些外围隔离沟槽的宽度从最靠近感光点矩阵的外围隔离沟槽开始下降。

32.有利地,外围区的外围隔离沟槽具有的深度介于界定感光点矩阵的感光点隔离沟槽的深度的三分之一与三分之二之间。

33.优选地,外围区具有的宽度介于20μm与400μm之间。

34.根据另一方面,提出了一种传感器包括:半导体衬底;半导体衬底中的感光点的矩

阵,由包括多晶硅的第一隔离沟槽界定;以及半导体衬底的第一外围区,围绕感光点的矩阵,第一外围区包括由包含多晶硅的第二隔离沟槽界定的第一虚设感光点;其中第一外围区的第二隔离沟槽中的多晶硅密度低于用于感光点的述矩阵的第一隔离沟槽中的多晶硅密度。

35.根据某些实施例,传感器进一步包括:半导体衬底的第二外围区,围绕半导体衬底的第一外围区,第二外围区包括由包含多晶硅的第三隔离沟槽界定的第二虚设感光点;其中第二外围区的第三隔离沟槽中的多晶硅密度小于第一外围区的第二隔离沟槽中的多晶硅密度。

36.根据某些实施例,感光点的矩阵以第一间距被布置,第一虚设感光点以大于第一间距的第二间距被布置,并且第二虚设感光点以大于第二间距的第三间距被布置。

37.根据某些实施例,第二间距是第一间距的两倍,并且第三间距是第一间距的四倍。

38.根据某些实施例,第二隔离沟槽的深度小于第一隔离沟槽的深度,并且其中第三隔离沟槽的深度小于第二隔离沟槽的深度。

39.根据某些实施例,感光点的矩阵以第一间距被布置,并且第一虚设感光点以大于第一间距的第二间距被布置。

40.根据某些实施例,第二间距是第一间距的两倍。

41.根据某些实施例,第二隔离沟槽的深度小于第一隔离沟槽的深度。

附图说明

42.本实用新型的其他优点和特征将在审阅实施例和实施方式的详细描述(决非限制性的)以及附图时显而易见,其中:

43.图1示出了传感器的半导体板的俯视图;

44.图2示出了在图1中示出的半导体板的截面图;

45.图3示出了半导体板的第二实施方式的截面图;以及

46.图4示出了用于制造传感器的方法的实施例。

具体实施方式

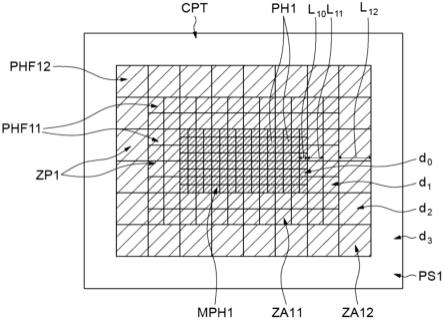

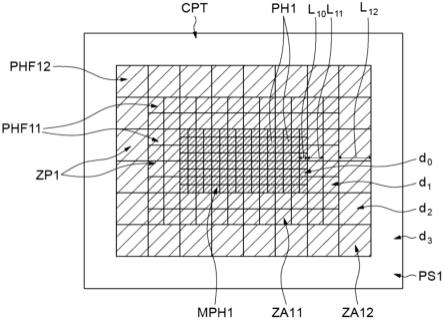

47.图1示出了根据一实施例的传感器cpt的半导体板ps1的俯视图。图2示出了该半导体板ps1的截面图。

48.半导体板ps1包括包含感光点矩阵mph1的半导体衬底sub1。矩阵mph1的感光点ph1以行和列的方式布置。

49.矩阵mph1的感光点ph1通过隔离沟槽pht1而被彼此隔离,优选地,这些隔离沟槽pht1是电容性隔离沟槽(在本领域中也称为电容性深沟槽隔离(cdti)沟槽)。因此矩阵mph1的轮廓包括隔离沟槽pht1。隔离沟槽pht1从半导体衬底sub1的自由面fl1起在半导体衬底sub1中沿深度延伸。例如,隔离沟槽pht1在介于3μm与10μm之间的深度上延伸。

50.感光点ph1具有的宽度l

10

介于0.5μm与5μm之间。感光点的宽度由界定感光点ph1的两个相对隔离沟槽pht1之间的距离限定。

51.感光点矩阵mph1具有给定间距。该间距由感光点ph1的宽度和界定该感光点ph1的隔离沟槽pht1的宽度之和限定。

52.半导体板ps1还包括围绕感光点矩阵的外围区zp1。外围区zp1因此形成于半导体衬底sub1中。半导体衬底sub1的范围进一步围绕外围区zp1。

53.具体地,在图1中,外围区zp1包括两个环形区za11、za12。

54.外围区zp1具有的宽度l1介于20μm与400μm之间。

55.第一环形区za11包括两个(外围)隔离沟槽ti11、ti12。第一环形区可以包括虚设感光点phf11,该虚设感光点位于两个隔离沟槽ti11、ti12之间、以及隔离沟槽ti11与感光点矩阵之间。在本文中,“虚设感光点”可以例如具有与感光点ph1相同的组成、配置以及总体布局,除了虚设感光点没有建立电连接。或者,“虚设感光点”可以例如仅包括由(外围)隔离沟槽界定的衬底的一部分。

56.第一隔离沟槽ti11围绕感光点矩阵mph1延伸。

57.第二隔离沟槽ti12围绕第一隔离沟槽ti11延伸。

58.第一隔离沟槽ti11位于离感光点矩阵mph1的距离l

11

处,该距离大于感光点ph1的宽度l

10

。

59.同样地,第二隔离沟槽ti12位于大于感光点ph1的宽度的距离处。该距离等于第一隔离沟槽ti11与感光点矩阵mph1之间的距离。这些距离例如介于1μm与10μm之间。

60.第一环形区的隔离沟槽ti11、ti12是深隔离沟槽。隔离沟槽ti11、ti12从衬底sub1的自由面起在与界定感光点ph1的隔离沟槽pht1的深度相同的深度上延伸。隔离沟槽ti11、ti12可以是cdti沟槽。因此隔离沟槽ti11、ti12由诸如二氧化硅等的介电涂层材料形成并且填充有硅。或者,隔离沟槽ti11、ti12可以是深隔离沟槽(deep trench isolation

–

dti)。因此隔离沟槽ti11、ti12仅填充有诸如二氧化硅等的介电涂层材料。

61.第一环形区za11的隔离沟槽ti11、ti12具有相同的宽度。第一环形区za11的隔离沟槽ti11、ti12的宽度与感光点矩阵mph1的隔离沟槽pht1的宽度相同。

62.优选地,第一环形区za11具有的间距比感光点矩阵mph1的间距大两倍。第一环形区za11的间距由隔离沟槽ti11、ti12的宽度和两个隔离沟槽ti11、ti12之间的距离之和限定。

63.第二环形区za12围绕第一环形区za11延伸。第二环形区za12包括隔离沟槽ti13。该隔离沟槽ti13围绕第一环形区za11延伸。第二环形区可以包括在衬底中形成在隔离沟槽ti13与隔离沟槽ti12之间的虚设感光点phf12。

64.相对于第一环形区za11,第二环形区za12的隔离沟槽ti13位于距离l

12

处,该距离大于来自第一环形区za11的两个隔离沟槽ti11、ti12之间的距离l

11

。该距离例如介于2μm与20μm之间。

65.隔离沟槽ti13是深隔离沟槽。隔离沟槽ti13从衬底的自由面起在与界定感光点ph1的隔离沟槽pht1的深度相同的深度上延伸。隔离沟槽ti13可以是cdti沟槽。因此隔离沟槽ti13由诸如二氧化硅等的介电涂层材料形成并且填充有硅。或者,隔离沟槽t113可以是深隔离沟槽(deep trench isolation)。因此隔离沟槽ti13仅填充有诸如二氧化硅等的介电涂层材料。

66.第二环形区za12的隔离沟槽ti13的宽度与感光点矩阵mph1的隔离沟槽pht1的宽度相同。

67.优选地,第二环形区za12具有的间距比感光点矩阵mph1的间距大四倍。第二环形

区za12的间距由隔离沟槽ti13的宽度和隔离沟槽ti13与第一环形区za11之间的距离之和限定。

68.因此,外围区zp1的各个环形区za11、za12的间距大于感光点矩阵mph1的间距,并且从最靠近感光点矩阵mph1的环形区za11开始增加。

69.这允许从感光点矩阵mph1开始逐渐降低多晶硅密度。具体地,间距越大,多晶硅密度就越低。

70.因此,第一环形区za11具有多晶硅密度d1。第二环形区za12具有多晶硅密度d2。第一环形区za11的多晶硅密度d1介于感光点矩阵边缘上的多晶硅密度d0与第二环形区za12的多晶硅密度d2之间。第二环形区za12的多晶硅的密度d2大于围绕外围区zp1的半导体衬底的范围中的多晶硅密度d3。

71.因此,机械应力从感光点矩阵mph1开始逐渐下降。

72.因此,外围区zp1允许降低感光点矩阵边缘处的曲率。

73.这种半导体板ps1可以形成多层摄影传感器的层。因此,半导体板ps1可以粘合至半导体衬底的另一个板。

74.当然,该第一实施方式能够进行对本领域技术人员显而易见的各种替换和修改。

75.具体地,第二环形区za12可以包括根据第二环形区za12的间距而布置的多个隔离沟槽。因此,这些隔离沟槽在与隔离沟槽t113相同的深度上延伸。

76.同样地,第一环形区za11可以包括根据第一环形区za11的间距布置的两个以上的隔离沟槽。第一环形区za11还可以包括单个隔离沟槽。

77.此外,外围区zp1可以包括围绕感光点矩阵的两个以上的环形区。在此情况下,环形区包括至少一个隔离沟槽,该隔离沟槽具有与界定感光点的隔离沟槽的宽度相同的宽度。环形区具有从感光点矩阵开始增加的间距。

78.图3示出了半导体板ps2的第二实施方式的截面图。

79.半导体板ps2包括半导体衬底sub2,该半导体衬底包括感光点矩阵mph2。矩阵mph2的感光点ph2以行和列的方式布置。

80.与图1类似地,矩阵mph2的感光点ph2通过隔离沟槽pht2而被彼此隔离,优选地,这些隔离沟槽pht2是电容性隔离沟槽(也称为电容性深沟槽隔离(cdti)沟槽)。因此矩阵mph2的轮廓包括隔离沟槽pht2。隔离沟槽pht2从衬底sub2的自由面fl2起在半导体衬底sub2中沿深度延伸。例如,隔离沟槽pht2在介于3μm与10μm之间的深度pf

20

上延伸。此外,隔离沟槽pht2具有的宽度例如介于0.2μm与0.6μm之间。

81.与图1类似地,感光点ph2具有的宽度l

20

介于0.5μm与5μm之间。感光点ph2的宽度由界定感光点ph2的两个相对隔离沟槽pht2之间的距离限定。

82.半导体板ps2还包括围绕感光点矩阵mph2的外围区zp2。因此外围区zp2形成在半导体衬底sub2中。

83.具体地,外围区zp2包括两个环形区za21、za22。

84.外围区zp2具有的宽度l2介于20μm与400μm之间。

85.第一环形区za21包括两个隔离沟槽ti21、ti22。隔离沟槽ti21、ti22可以是cdti沟槽。因此隔离沟槽ti21、ti22由诸如二氧化硅等的介电涂层材料形成并填充有硅。或者,隔离沟槽ti21、ti22可以是深隔离沟槽(deep trench isolation)。因此隔离沟槽ti21、ti22

仅填充有诸如二氧化硅等的介电涂层材料。

86.第一隔离沟槽ti21围绕感光点矩阵mph2延伸。

87.第二隔离沟槽ti22围绕第一隔离沟槽ti21延伸。

88.第一隔离沟槽ti21与第二隔离沟槽ti22之间的距离l

21

等于感光点ph2的宽度l

20

。同样地,第一隔离沟槽ti21与感光点矩阵mph2之间的距离等于感光点ph2的宽度。

89.第一环形区za21可以包括在衬底中形成于(外围)隔离沟槽ti22与(外围)隔离沟槽ti21之间、以及在隔离沟槽ti21与感光点矩阵之间的虚设感光点phf21。

90.第一环形区za21的隔离沟槽ti21、ti22具有的宽度lt

21

小于界定感光点ph2的隔离沟槽pht2的宽度lt

20

。例如,第一环形区za21的隔离沟槽ti21、ti22具有的宽度l

21

介于0.1μm与0.3μm之间。

91.此外,第一环形区za21的隔离沟槽ti21、ti22相比界定感光点ph2的隔离沟槽pht2延伸较浅。例如,第一环形区za21的隔离沟槽ti21、ti22从衬底sub2的自由面fl2起在介于界定感光点矩阵的感光点的隔离沟槽的深度的二分之一与三分之二之间的深度pf

21

上延伸。

92.第二环形区za22围绕第一环形区za21延伸。第二环形区za22包括两个隔离沟槽ti23、ti24。这些隔离沟槽ti23、ti24围绕第一环形区za21延伸。隔离沟槽ti23、ti24可以是cdti沟槽。因此隔离沟槽ti23、ti24由诸如二氧化硅等的介电涂层材料形成并且填充有硅。或者,隔离沟槽ti23、ti24可以是深隔离沟槽(deep trench isolation)。因此隔离沟槽ti23、ti24仅填充有诸如二氧化硅等的介电涂层材料。

93.第二环形区za22的两个隔离沟槽ti23、ti24之间的距离l

22

等于感光点矩阵mph2的感光点ph2的宽度l

20

。同样地,第二环形区za22的第一隔离沟槽ti23位于离第一环形区za21的一距离处,该距离等于感光点矩阵mph2的感光点ph2的宽度l

20

。

94.第二环形区za22可以包括在衬底中形成于隔离沟槽ti24与隔离沟槽ti23之间、以及隔离沟槽ti23与隔离沟槽ti22之间的虚设感光点phf22。

95.第二环形区za22的隔离沟槽ti23、ti24具有的宽度lt

22

小于第一环形区za21的隔离沟槽ti21、ti22的宽度lt

21

。例如,第二环形区za22的隔离沟槽ti23、ti24具有的宽度l

22

介于0.05μm与0.15μm之间。

96.此外,第二环形区za22的隔离沟槽ti23、ti24相比第一环形区za22的隔离沟槽ti21、ti22延伸得较浅。例如,第二环形区za22的隔离沟槽ti23、ti24从衬底的自由面fl2起在介于界定感光点矩阵的感光点的隔离沟槽的深度的三分之一与二分之一之间的深度pf

22

上延伸。

97.因此,外围区zp2的各个环形区za21、za22的隔离沟槽ti21、ti22、ti23、ti24的宽度和深度小于感光点矩阵mph2的隔离沟槽pht2的宽度。此外,隔离沟槽ti21、ti22、ti23、ti24的宽度和深度从最靠近感光点矩阵mph2的环形区za21开始减小。

98.这种外围区zp2还允许从感光点矩阵mph2开始逐渐降低多晶硅密度。具体地,隔离沟槽的深度越小,多晶硅密度就越低。

99.因此,机械应力从感光点矩阵mph2开始逐渐下降。

100.因此,外围区zp2允许降低在感光点矩阵mph2的边缘处的曲率。

101.这种半导体板ps2也可以形成多层摄影传感器的层。因此,半导体板可以粘合至半

导体衬底的另一个板。

102.当然,该第二实施方式能够进行对本领域技术人员显而易见的各种替换和修改。

103.具体地,第一环形区za21可以包括具有相同宽度并且在相同深度上延伸的两个以上的隔离沟槽。第一环形区还可以包括单个隔离沟槽。

104.同样地,第二环形区za22可以包括具有相同宽度并且在相同深度上延伸的两个以上的隔离沟槽。第二环形区za22还可以包括单个隔离沟槽。

105.此外,外围区zp2可以包括围绕感光点矩阵的两个以上的环形区,或单个环形区。在此情况下,环形区包括至少一个隔离沟槽。因此,隔离沟槽的宽度和深度从感光点矩阵开始在各个环形区之间下降。此外,各个环形区的隔离沟槽之间的距离与感光点矩阵的感光点宽度保持相同。

106.还可以将在图1和图2中示例性地示出的半导体板的第一实施方式与在图3中示出的第二实施方式结合。在此情况下,外围区的环形区具有从最靠近感光点矩阵的环形区开始增加的间距,并且外围区的环形区的隔离沟槽具有从最靠近感光点矩阵的环形区开始下降的宽度和深度。

107.图4示出了根据本实用新型的实施方式的用于制造传感器的方法的实施例。

108.该方法包括获取步骤40,其中包括获取半导体衬底的半导体板。这种半导体板可以通过本领域技术人员公知的方法获取。

109.所述方法进一步包括形成感光点矩阵的步骤41,其中感光点矩阵形成于半导体板的半导体衬底中。感光点矩阵可以通过本领域技术人员公知的方法形成。具体地,形成感光点矩阵,以便获取以行和列布置的数个感光点,每个感光点由隔离沟槽(具体地,电容性隔离沟槽)被分离。

110.所述方法进一步包括形成外围区的步骤42。在该步骤中,外围区围绕感光点矩阵而形成。

111.具体地,形成外围区包括形成包含至少一个隔离沟槽的至少一个环形区。

112.例如,形成外围区可以包括形成在图1和图2中示出的环形区,或者形成在图3中示出的环形区。

113.环形区的隔离沟槽可以通过本领域技术人员已知的方法获取。例如,环形区的隔离沟槽可以通过在蚀刻后通过沉积诸如二氧化硅等的介电材料而获取。