封装结构的制作方法

1.本公开的实施例涉及一种封装结构。

背景技术:

2.半导体封装技术可将系统芯片(system on chip,soc)和存储器芯片集成在一起,以向系统芯片提供高带宽并实现高性能运算(high-performancecomputing,hpc)。系统芯片包括用于运算的逻辑电路以及用于外部连接的输入输出电路,随着半导体工艺的不断发展,半导体器件越来越趋向于小型化和高度集成,对于系统芯片而言,虽然逻辑电路的尺寸随着半导体工艺节点的发展而不断减小,但不同工艺节点之间输入输出电路的尺寸变化却很小,且因此会在系统芯片中占用较大面积而限制逻辑电路的可使用面积。此外,使用先进工艺节点技术来制造系统芯片成本较高。

技术实现要素:

3.根据本公开的至少一个实施例提供一种封装结构,其包括:封装基板;以及第一子封装结构,设置于所述封装基板上,所述第一子封装结构包括第一管芯组、第一附加管芯和第一封装连接构件,所述第一管芯组包括第一主管芯和第一子管芯,其中,所述第一主管芯具有沿第一方向延伸的第一侧边和沿第二方向延伸的第二侧边,所述第一方向和所述第二方向相交,所述第一子管芯在所述第二方向上设置在所述第一主管芯的一侧,所述第一附加管芯在所述第二方向上设置在所述第一主管芯的一侧,所述第一封装连接构件设置于所述第一管芯组和所述第一附加管芯与所述封装基板之间,以至少提供所述第一主管芯与所述第一子管芯之间以及所述第一管芯组与第一附加管芯之间的电性连接,所述第一管芯组的所述第一子管芯包括设置于第一连接区中的第一连接件和设置于第二连接区中的第二连接件,所述第一连接件通过所述第一封装连接构件连接到所述第一主管芯,所述第二连接件通过所述第一封装连接构件连接到所述封装基板,且被配置为与所述第一子封装结构以外的外部构件进行连接。

4.根据本公开至少一个实施例提供的封装结构中,所述第一子管芯具有第一侧和第二侧,所述第一子管芯的所述第一侧面向所述第一主管芯的所述第一侧边,且所述第二侧与所述第一侧沿大致垂直的方向延伸,所述第一子管芯的所述第一连接区设置在所述第一侧,且所述第二连接区设置在所述第二侧。

5.根据本公开至少一个实施例提供的封装结构中,所述第一子管芯的所述第一连接件和所述第一主管芯并行连接,而所述第一子管芯的所述第二连接件与所述外部构件串行连接。

6.根据本公开至少一个实施例提供的封装结构中,所述第一连接件之间的节距小于或等于所述第二连接件之间的节距。

7.根据本公开至少一个实施例提供的封装结构中,所述第一附加管芯和所述第一子管芯在所述第二方向上设置在所述第一主管芯的同一侧或相对侧。

8.根据本公开至少一个实施例提供的封装结构中,所述第一附加管芯和所述第一子管芯在所述第一方向上交叠,所述第一主管芯具有在所述第一方向上相对的两个所述第二侧边,且所述第一附加管芯和所述第一子管芯在所述第一方向上设置在所述第一主管芯的两个所述第二侧边在所述第二方向上的延长线之间。

9.根据本公开至少一个实施例提供的封装结构中,还包括:包封层,设置于所述第一封装连接构件的远离所述封装基板的一侧,且至少在平行于所述封装基板的主表面的方向上侧向包封所述第一管芯组和所述第一附加管芯。

10.根据本公开至少一个实施例提供的封装结构中,所述包封层包括沿所述第一方向延伸的第一边缘和沿所述第二方向延伸的第二边缘,其中在所述第一主管芯的所述第二侧边与所述包封层的所述第二边缘之间的空间被所述包封层大致填满。

11.根据本公开至少一个实施例提供的封装结构中,在所述第一主管芯的所述第二侧边与所述包封层的所述第二边缘之间的所述空间没有设置管芯或除所述包封层以外的其他构件。

12.根据本公开至少一个实施例提供的封装结构中,所述第一封装连接构件包括中介板、桥接管芯或再分布结构。

13.根据本公开至少一个实施例提供的封装结构中,所述第一管芯组包括系统芯片,且所述第一主管芯为包括逻辑电路的逻辑管芯,所述第一子管芯为包括输入输出电路的输入输出管芯。

14.根据本公开至少一个实施例提供的封装结构中,所述第一附加管芯为存储器管芯,且所述存储器管芯通过所述第一封装连接构件连接至所述逻辑管芯。

15.根据本公开至少一个实施例提供的封装结构中,所述第一子管芯具有沿所述第二方向延伸的侧边,且所述第一子管芯的所述侧边与所述第一主管芯的所述第二侧边在所述第二方向上彼此对齐。

16.根据本公开至少一个实施例提供的封装结构中,所述第一主管芯的所述第一侧边在所述第一方向上的长度大于或等于所述第二侧边在所述第二方向上的长度,其中所述第一子管芯和所述第一附加管芯各自在所述第一方向上的宽度小于或等于所述第一主管芯的在所述第一方向上的所述长度。

17.根据本公开至少一个实施例提供的封装结构中,还包括第二子封装结构,所述第二子封装结构与所述第一子封装结构沿所述第一方向并排设置于所述封装基板上。

18.根据本公开至少一个实施例提供的封装结构中,所述第二子封装结构包括第二管芯组、第二附加管芯和第二封装连接构件,所述第二管芯组包括第二主管芯和第二子管芯,其中,所述第二主管芯在所述第一方向上的长度大于其在所述第二方向上的长度;所述第二子管芯在所述第二方向上设置在所述第二主管芯的一侧;所述第二附加管芯在所述第二方向上设置在所述主管芯的一侧;所述第二封装连接构件设置于所述第二管芯组和所述第二附加管芯与所述封装基板之间,以提供所述第二主管芯与所述第二子管芯之间以及所述第二管芯组与所述第二附加管芯之间的电性连接,所述第二子管芯包括设置于第三连接区中的第三连接件和设置于第四连接区中的第四连接件,所述第三连接件通过所述第二封装连接构件连接到所述第二主管芯,所述第四连接件通过所述第二封装连接构件和所述封装基板连接到所述第一子封装结构的所述第一子管芯的所述第二连接件。

19.根据本公开至少一个实施例提供的封装结构中,所述第三连接区和所述第四连接区设置在所述第二子管芯的延伸方向彼此大致垂直的两侧。

20.根据本公开至少一个实施例提供的封装结构中,所述第一子封装结构还包括第三子管芯,在所述第二方向上设置在所述主管芯的一侧,且所述第三子管芯包括设置于第五连接区中的第五连接件和设置于第六连接区中的第六连接件,所述第五连接件通过所述第一封装连接构件连接到所述主管芯,且所述第六连接件被配置为通过所述第一封装连接构件和所述封装基板与所述封装结构以外的外部构件进行连接。

21.根据本公开至少一个实施例提供的封装结构中,所述第五连接区和所述第六连接区设置在所述第三子管芯的延伸方向彼此大致垂直的两侧。

22.根据本公开至少一个实施例提供的封装结构中,还包括电子组件,安装在所述封装基板的主表面上,且在平行于所述封装基板的所述主表面的方向上排列在所述第一子封装结构的侧边。

23.根据本公开至少一个实施例提供的封装结构中,还包括加固环,设置在所述封装基板的主表面上,且在平行于所述封装基板的所述主表面的方向上侧向环绕所述第一子封装结构并与所述第一子封装结构间隔开。

24.根据本公开实施例的封装结构优化了管芯排布设计并能够提高主管芯的运算能力。

附图说明

25.为了更清楚地说明本公开实施例的技术方案,下面将对实施例的附图作简单地介绍,显而易见地,下面描述中的附图仅仅涉及本公开的一些实施例,而非对本公开的限制。

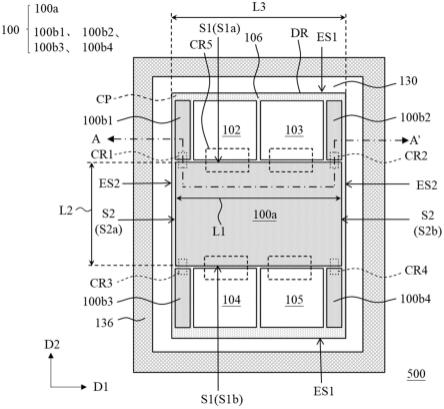

26.图1示出根据本公开一些实施例的封装结构的示意性俯视图。

27.图2a示出根据本公开另一些实施例的封装结构的示意性俯视图。

28.图2b和图2c分别示出图2a所示封装结构中一些子管芯与周边构件的放大示意图。

29.图3a至图3c示出根据本公开另一些实施例的封装结构的示意性截面图。

30.图4示出根据本公开又一些实施例的封装结构的示意性俯视图。

31.图5a至图5c示出根据本公开又一些实施例的封装结构的示意性截面图。

具体实施方式

32.为使本公开实施例的目的、技术方案和优点更加清楚,下面将结合本公开实施例的附图,对本公开实施例的技术方案进行清楚、完整地描述。显然,所描述的实施例是本公开的一部分实施例,而不是全部的实施例。基于所描述的本公开的实施例,本领域普通技术人员在无需创造性劳动的前提下所获得的所有其他实施例,都属于本公开保护的范围。

33.除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。

34.本公开各种实施例将系统芯片分为主管芯(例如,包括逻辑电路的逻辑电路管芯)以及子管芯(例如,包括输入输出电路的输入输出电路管芯),并使用封装连接构件将主管芯和子管芯集成在一起而成为管芯组,此外,附加管芯(例如,存储器管芯)也通过封装连接构件与该管芯组集成在一起。此外,本公开一些实施例通过改善主管芯、子管芯以及附加管芯的排列方式,进而可最大化主管芯的可使用面积,从而可提供更高速运算能力(highercomputing power),另外,还可控制或减小整体封装结构的翘曲问题,且可节省制造成本。

35.图1示出根据本公开一些实施例的封装结构的示意性俯视图。

36.参照图1,在一些实施例中,封装结构50包括管芯组10以及管芯(die) 2、3、4、5、包封层(encapsulant layer)6、封装连接构件7、封装基板8以及加固环(stiffener ring)9。管芯组10包括由单个管芯分出的主管芯10a和子管芯10b1和10b2。管芯2-5为管芯组10以外的其他管芯,且又可被称为附加管芯(additional die)。封装连接构件7设置于管芯组10和管芯2-5与封装基板8之间,包封层6设置于封装连接构件7的远离封装基板8的一侧,且环绕包覆各个管芯。应注意,封装连接构件7被上覆的包封层6和管芯覆盖,因而在俯视图中不可见而以虚线示出。加固结构9可设置于封装基板8上,且可用于防止或减小整个封装结构50的翘曲。在一些实施例中,管芯组10是系统芯片(system on chip,soc),且包括逻辑电路和输入输出电路。在一些实施例中,将系统芯片的输入输出电路和逻辑电路分开并各自设置于单独的较小管芯中,并通过封装连接构件将逻辑管芯和输入输出管芯集成在同一个封装件中。例如,管芯组10中的主管芯10a为包括逻辑电路的逻辑管芯,或可称为soc管芯,且子管芯10b1和10b2为包括输入输出电路的输入输出管芯。主管芯10a以及子管芯10b1、10b2通过封装连接构件7彼此连接。通过将系统芯片分成逻辑管芯和输入输出管芯并通过封装构件将这些管芯集成在一起,可节省制造成本。

37.在一些实施例中,主管芯10a具有沿方向d1延伸的侧边以及沿方向d2 延伸的侧边,方向d1和d2彼此相交,且例如大致是彼此垂直的。子管芯 10b1和10b2在方向d1上排列在逻辑管芯10a的侧边(例如,相对两侧);管芯2-5可为与管芯10不同类型的管芯,例如是存储器芯片。在一些实施例中,管芯2-5中的一或多个为高带宽存储器(high bandwidth memory,hbm) 芯片。管芯2-5在方向d2上设置在逻辑管芯10a的侧边(例如,相对两侧)。也就是说,子管芯10b1-10b2和管芯2-5在不同方向上(例如,彼此相交或垂直的方向上)设置在主管芯的不同侧。

38.本公开的发明人在对包括管芯组的封装结构进行研究的过程中发现,在上述封装结构50中,由于受限于工艺限制(例如,光罩尺寸限制)以及考虑到可能存在的翘曲问题,封装连接构件7的尺寸(例如,在方向d1和d2上的长度、宽度、面积等)是受限的。也就是说,可供管芯组10以及芯片2-5 排布的整体尺寸是受限的。在此情况下,若将子管芯10b1和10b2和管芯2

‑ꢀ

5在不同方向(例如,彼此相交或垂直的不同方向)上设置在主管芯的不同侧,会使得主管芯10a的尺寸进一步受到限制,在主管芯10a为逻辑管芯的实施例中,此种尺寸限制进而会影响逻辑管芯的运算能力。

39.基于上述研究,本公开发明人对上述封装结构中各个管芯的排布进行了进一步的改进,从而可最大化主管芯的尺寸,进而可提高主管芯的运算能力。另外,改进后的封装结构还可进一步改善(例如,减小)封装结构的翘曲问题。具体阐述如下。

40.图2a示出根据本公开另一些实施例的封装结构500的示意性俯视图。封装结构500

可根据封装连接构件的不同而实现为不同的封装结构500a

‑ꢀ

500c(统称为封装结构500)。图3a至图3c示出根据本公开一些实施例的封装结构500a-500c的示意性截面图,且图3a至图3c为沿图2a的线a-a’截取的截面图。

41.参照图2a,在一些实施例中,封装结构500包括管芯组100、管芯102

‑ꢀ

105、包封层106、封装连接构件cp以及封装基板130。其中可将位于封装基板130上的包括管芯组100、管芯102-105、包封层106以及封装连接构件cp的结构称为子封装结构。在一些实施例中,管芯组100可为soc芯片,且可包括从soc芯片分出的主管芯以及至少一个子管芯;举例来说,管芯组包括主管芯100a以及多个子管芯100b1、100b2、100b3、100b4,主管芯100a 例如是包括逻辑电路的逻辑管芯(logic die),多个子管芯100b1-100b4例如分别是包括输入输出电路的输入输出管芯(input/output die,i/o die)。管芯 102-105可为与管芯组100不同类型的管芯,且例如是存储器管芯。举例来说,管芯102-105各自可为动态随机存储器(dynamic random access memory, dram)管芯、静态随机存取存储器(static random access memory,sram)、高带宽存储器(high bandwidth memory,hbm)管芯或其他类型的存储器管芯中的一种。

42.在一些实施例中,管芯组100和多个管芯102-105设置于封装连接构件 cp之上,且封装连接构件cp设置于封装基板108上,即,封装连接构件 cp设置于管芯组100和多个管芯102-105与封装基板108之间。管芯组100 所包括的主管芯100a和子管芯100b1-100b4以及管芯102-105彼此间隔开的并排设置在封装连接构件cp上,包封层106设置于封装连接构件cp的远离封装基板108的一侧且环绕包覆管芯组100和多个管芯102-105,即包封层106设置在管芯组100的各个管芯以及多个管芯102-105之间且环绕各个管芯的侧壁。应注意,包封层106在方向d1和d2上的尺寸大致等于封装连接构件cp在方向d1和d2上的尺寸,封装连接构件cp由于被上覆的包封层106和管芯覆盖,因此在俯视图中不可见而以虚线示出。在一些实施例中,管芯组100和多个管芯102-105安装在封装连接构件cp的主表面(例如,顶表面)上,且大致不会超出封装连接构件cp的所在的区域。也就是说,在垂直于封装基板130的主表面(例如,顶表面)的方向上,管芯组100 和多个管芯102-105在封装基板130的主表面上的正投影落在封装连接构件 cp在封装基板130的主表面上的正投影的范围内。举例来说,将封装连接构件cp的顶面所在的区域称为管芯区dr,管芯区dr的边界由封装连接构件cp在方向d1和d2上的边界界定。在一些实施例中,包封层106的边界与封装连接构件cp在方向d1和d2上的边界大致对齐。

43.在一些实施例中,从俯视图来看,主管芯100a的形状可大致设置成矩形或正方形,且具有彼此平行的沿第一方向延伸的两个第一侧边以及彼此平行的沿与第一方向相交(例如,大致垂直)的第二方向延伸的两个第二侧边,即,第一侧边和第二侧边彼此相交且例如是彼此大致垂直的,两个第一侧边的长度彼此大致相同,两个第二侧边的长度彼此大致相同,第一侧边和第二侧边之一(例如,第一侧边)的长度大于或等于第一侧边和第二侧边之另一 (例如,第二侧边)的长度。然而,主管芯100a也可根据产品的设计和需求设置成任意合适的形状,且本公开并不对此进行限制。举例来说,主管芯100a 具有沿方向d1延伸的侧边(或侧壁)s1和沿方向d2延伸的侧边(或侧壁) s2,侧边s1和侧边s2可分别称为第一侧边和第二侧边(或分别称为第一侧壁和第二侧壁),或反之亦然。方向d1和方向d2彼此相交,例如是彼此大致垂直。主管芯100a的侧边s1包括彼此平行的沿方向d1延伸且在方向d2 上彼

100b4和管芯102-105设置在主管芯100a的侧边s2a和s2b的沿方向d2延伸的延长线之间;子管芯100b1

‑ꢀ

100b4和管芯102-105在方向d2上在包封层106的沿方向d1延伸的边缘es1上的正投影落在主管芯100a在方向d2上在包封层106的边缘es1上的正投影的范围内或者与主管芯100a在方向d2上在包封层106的边缘es1 上的正投影重合。

48.在一些实施例中,子管芯100b1-100b4设置在靠近包封层106边缘的角落处,管芯102和103在方向d1上设置在子管芯100b1和100b2之间,管芯104和105在方向d1上设置在子管芯100b3和100b4之间。也就是说,管芯102和103以及子管芯100b1和100b2在方向d1上交叠,管芯104和 105以及子管芯100b3和100b4在方向d1上交叠;也就是说,管芯102和 103以及子管芯100b1和100b2在方向d1上在包封层106的边缘es2上的正投影彼此重合(例如,部分重合或全部重合);管芯104和105以及子管芯100b3和100b4在方向d1上在包封层106的边缘es2上的正投影彼此重合(例如,部分重合或全部重合)。在一些实施例中,子管芯100b1和100b3 的沿方向d2延伸的侧边与主管芯的侧边s2a大致对齐,子管芯100b2和 100b4的沿方向d2延伸的侧边与主管芯的侧边s2b大致对齐,但本公开并不以此为限。

49.应理解,图2a所示的芯片组的子管芯和芯片组以外的其他管芯的数量和排列方式以及子管芯和其他管芯的相对位置关系仅为例示说明,且本公开并不以此为限。只要子管芯和其他管芯沿同一个方向设置在主管芯一侧或两侧,而不是沿不同方向设置在主管芯旁边即可。例如,子管芯和其他管芯可在方向d2上设置在主管芯的单侧或相对两侧,且在方向d2上在主管芯的每一侧处可各自设置子管芯和/或其他管芯,只要子管芯和其他管芯不在方向 d1上设置在主管芯的旁边,子管芯和其他管芯的数量和排列方式并不受限制,且在方向d2上设置在主管芯两侧的子管芯和其他管芯的数量和/或排列方式可相同或不同。举例来说,在另一些实施例中,子管芯和其他管芯可均设置在主管芯100a的靠近其侧边s1a和s1b之一的一侧,而在主管芯100a 的靠近其侧边s1a和s1b之另一的一侧没有设置子管芯或其他管芯。在再一些实施例中,所有子管芯均设置在主管芯100a的靠近其侧边s1a和s1b之一的一侧,而其他管芯均设置在主管芯100a的靠近其侧边s1a和s1b之另一的一侧。

50.在本公开的实施例中,由于子管芯和其他管芯沿同一方向d2上设置在主管芯的一侧或相对侧,而在方向d1上没有管芯设置在主管芯的旁边,因此主管芯在方向d1上的尺寸不会受到限制,如此可使得主管芯的尺寸最大化,进而使得主管芯可提供更高运算能力。此外,通过上述的排列方式,管芯组的子管芯也可起到机械填充芯片(mechanical fill chiplet)的作用,而且可减小包封层的填充面积,进而改善(例如,减小)封装结构的翘曲。

51.参照图2a和图3a,在一些实施例中,封装结构500a为基板上晶片上芯片(chip-on-wafer-on-substrate,cowos)封装,其使用中介板(interposer) 120作为封装连接构件cp。封装结构500a包括设置在封装基板130上的子封装结构spg1。在此实施例中,子封装结构spg1为晶片上芯片(chip-on

‑ꢀ

wafer,cow)封装。

52.在一些实施例中,管芯组100中的主管芯100a和子管芯100b1-100b4具有大致类似的结构。以主管芯100a为例,如图3a中的放大图所示,主管芯 100a可包括衬底110a、装置层112a以及多个导电连接件113a,衬底110a可为半导体衬底,例如是硅衬底,衬底也可替代的或另外的包括其他合适的半导体材料(例如锗)。在一些实施例中,装置层112a中包括形成在衬底110a 的靠近装置层112a一侧的一或多个装置,例如是有源装置(active device) 和/或无源装置(passive device)。有源装置例如包括晶体管、二极管等,无源装置例如包

括电容器、电阻器、电感器等。装置层112a中还设置有互联结构 (interconnection structure),其包括嵌置于介电材料中的一或多层导电走线。多个装置可通过互联结构连接,且形成逻辑电路。逻辑电路还通过导电走线与导电连接件113a连接,导电连接件113a作为主管芯100a的外部连接点,用于将主管芯的逻辑电路连接(例如,电性连接)至主管芯以外的其他构件。导电连接件113a可包括金属材料,例如铝、铜等,但本公开并不以此为限。

53.类似的,子管芯100b1可包括衬底110b、装置层112b以及多个导电连接件113b,子管芯100b1的该些构件与上文针对主管芯100a描述的类似,不同之处在于,子管芯100b1的装置层112b包括输入输出电路,例如是形成在衬底110b的靠近装置层112b的一侧的多个装置通过互联结构连接,并形成输入输出电路。输入输出电路通过导电走线与导电连接件113b电性连接,且导电连接件113b作为子管芯100b1的外部连接点,用于将子管芯100b1 的输入输出电路连接至子管芯100b1以外的其他构件。在一些实施例中,其他子管芯100b2-100b4的结构与子管芯100b1的大致相同,例如可分别包括衬底110b、装置层112b以及多个导电连接件113b。

54.参照图3a,在一些实施例中,作为封装连接构件cp的中介板120可包括衬底121、衬底穿孔(through substrate via,tsv)122以及互联结构126。衬底121可为半导体衬底,例如是硅衬底,但也可替代的或另外的包括其他合适的半导体材料。互联结构126设置在衬底121上,例如是设置在衬底 121的靠近管芯组100和多个管芯102-105的一侧。在一些实施例中,互联结构126包括嵌置于介电结构123中的一或多层导电走线125;介电结构123 的材料可包括氧化硅、氮化硅、氮氧化硅、其类似物或其组合,介电结构可为单层或多层结构;导电走线125的材料可为包括金属,例如是钛、铜等,导电走线125可包括导电线和导电通孔,导电线例如可在平行于衬底121的主表面的水平方向上延伸且可包括位于不同层的导电线,导电通孔可在垂直于衬底121的主表面的竖直方向上延伸且连接位于不同层的导电线;在一些实施例中,中介板120包括位于互联结构126的顶部的导电接垫,导电接垫例如可为导电走线125的靠近各个管芯的顶部部分,或者是形成在导电走线 125的靠近各个管芯的一侧的导电构件。衬底穿孔122包括导电材料,例如包括钛、铜等金属,且其材料可与导电走线125的材料相同或不同;衬底穿孔122延伸穿过衬底121,且与导电走线125电性连接;在一些实施例中,在衬底穿孔122与衬底121之间还设置有绝缘层,以使得衬底穿孔122与衬底121电性隔离。

55.在一些实施例中,多个连接件107设置于管芯组100和管芯102-105与中介板120之间,以提供管芯组100和管芯102-105与中介板120之间的电性连接。多个连接件107可包括多个导电凸块,例如是或包括多个微凸块 (micro-bump),多个微凸块分别设置在管芯组100的各个管芯的连接件 113a/113b和管芯102-105的连接件与中介板120的导电接垫之间,以将各个管芯电性连接至中介板120。

56.在一些实施例中,包封层106设置在中介板120上,例如设置在中介板 120的靠近管芯组100和管芯102-105的一侧,且环绕包覆管芯组100中的各个管芯以及管芯102-105。包封层106可包括模制化合物(moldingcompound),例如是环氧树脂模塑化合物(epoxy molding compound,emc),但本公开并不以此为限。在一些实施例中,管芯组100和管芯102-105在中介板120上彼此间隔开,且包封层106填充在各个管芯之间的空间;包封层 106可至少环绕包覆各个管芯的侧壁,且还可覆盖各个管芯的顶表面。在一些实施例中,包封层106

还填充在各个管芯与中介板120之间的空间,以环绕包覆多个微凸块107,且覆盖多个管芯的底表面,但本公开并不以此为限。在替代实施例中,可在各个管芯与中介板120之间的空间设置底部填充层 (underfill layer),以环绕包覆多个微凸块107,且底部填充层的侧壁被包封层106包封覆盖。

57.继续参照图2a和图3a,在一些实施例中,中介板120设置在封装基板 130上。在封装基板130中可包括导电走线132,多个导电连接件128设置在中介板120与封装基板130之间,以提供两者之间的电性连接。举例来说,导电连接件128设置在中介板120的衬底穿孔122与封装基板130的导电走线132之间,以使得中介板120电性连接到封装基板130。导电连接件128 可包括导电凸块,例如是受控塌陷芯片连接(controlled collapsed chipconnection,c4)凸块,但本公开并不以此为限。在一些实施例中,在中介板 120与封装基板130之间的空间还设置有底部填充层(underfill layer)129,以环绕包覆多个导电连接件128。在一些实施例中,在封装基板130上设置有一或多个电子组件135,电子组件135可为或包括无源组件,例如是电容器。电子组件135例如是设置在封装基板130的靠近中介板120的一侧,且可通过表面安装技术(surface mounting technology,smt)安装并连接至封装基板130,在此实施例中,电子组件135和导电连接件150设置在封装基板130的相对两侧。应理解,图中所示的电子组件135的位置和数量仅为例示说明,且本公开并不以此为限。举例来说,在另一些实施例中,电子组件 135也可设置在封装基板130的远离中介板120的一侧,且可与导电连接件 150设置在封装基板130的同一侧。此外,为简要起见,电子组件135并未在俯视图中示出。

58.在一些实施例中,加固环136安装在封装基板130的靠近中介板120的一侧,且可沿着封装基板130的边缘设置。加固环136可包括刚性材料,且可用于控制、改善(例如,减小)整个封装结构500a的翘曲。

59.在一些实施例中,多个导电连接件150设置在封装基板130的远离中介板120的一侧,且连接至封装基板130的导电走线132,进而通过封装基板 130、导电连接件128、中介板120以及连接件107耦合至管芯组100和管芯 102-105。在一些实施例中,导电连接件150可为或包括焊料球(solder ball),例如是球珊阵列(ball grid array,bga),但本公开并不以此为限。在一些实施例中,封装结构500a可进一步(例如,通过导电连接件150)连接至其他外部构件,例如印刷电路板(printed circuit board,pcb)。举例来说,可将封装结构500a安装在印刷电路板上,印刷电路板可设置于封装基板130的远离中介板120的一侧,且导电连接件150设置于封装基板130与印刷电路板之间,以提供封装结构500a与印刷电路板之间的电性连接。

60.参照图2a和图3a,在一些实施例中,管芯组100中的主管芯100a和多个子管芯100b1-100b4通过封装连接构件cp(例如,中介板120)连接到彼此,且管芯102-105也可通过封装连接构件cp(例如,中介板120)连接到管芯组100(例如,主管芯100a)。图2a中示意性的示出封装连接构件cp 中提供各个子管芯100b1-100b4与主管芯100a之间的电性连接的互联区cr1、 cr2、cr3、cr4以及提供各个管芯102-105与主管芯100a之间的电性连接的多个互联区cr5。

61.参照图2a和图3a,在封装连接构件cp是或包括中介板120的实施例中,互联区cr1-cr4可包括互联结构126中的导电走线125。举例来说,如图3a所示,导电走线125中的一些位

于互联区cr1中且提供主管芯100a 与子管芯100b1之间的电性连接,导电走线125中的一些位于互联区cr2中且提供主管芯100a与子管芯100b2之间的电性连接。也就是说,主管芯100a 与子管芯100b1通过多个连接件107以及中介板120的互联区cr1中的导电走线125彼此连接,主管芯100a与子管芯100b2通过多个连接件107以及中介板120的互联区cr2中的导电走线125彼此连接。应理解,主管芯 100a与子管芯100b3和100b4以及与管芯102-105的连接方式与上述连接方式类似,于此不再赘述。

62.在一些实施例中,管芯组100的主管芯100a和多个子管芯100b1-100b4 通过中介板120的互联结构126中的一些导电走线125彼此连接(或称为内部连接),此外,子管芯100b1-100b4作为输入输出电路管芯,还通过中介板 120和封装基板130连接至外部构件(例如,子封装结构spg1以外或封装结构500a以外的外部构件),即,进行外部连接。举例来说,子管芯100b1

‑ꢀ

100b4通过导电连接件107、中介板120的互联结构126中的另一些导电走线125以及衬底穿孔122、导电连接件128以及封装基板130中的导电走线 132连接到导电连接件150,且可进一步通过导电连接件150与封装结构500a 以外的外部构件进行连接。

63.在一些实施例中,主管芯100a中的子管芯100b1-100b4各自具有用于与主管芯100a进行内部连接的连接区(或称为内部连接区)以及用于与外部构件进行外部连接的连接件(或称为外部连接区);内部连接区设置在子管芯的靠近主管芯的一侧处,外部连接区可设置在子管芯的靠近包封层的边缘的一侧处,内部连接区所在的一侧与外部连接区所在的一侧沿大致垂直的方向延伸,但本公开并不以此为限。此处,内部或外部连接是相对于管芯组 100的内部或外部而言,即,将子管芯的用于管芯组100所包括的各管芯之间的连接称为内部连接,而将除此之外的并非用于管芯组100的各管芯之间的连接称为外部连接,例如是用于与子封装结构spg1以外的其他设置在封装基板上的子封装结构的连接或者与封装结构500以外的其他构件(例如,其他封装件或其他电子装置)之间的连接。

64.图2b示出图2a所示封装结构500中子管芯100b1及其周边构件的放大示意图。图2c示出图2a中子管芯100b2及其周边构件的放大示意图。

65.参照图2a和图2b,在一些实施例中,子管芯100b1包括用于与主管芯 100a进行内部连接的内部连接区inc以及用于进行外部连接的外部连接区 exc,内部连接区inc设置在子管芯100b1的靠近主管芯100a的一侧(例如,第一侧),外部连接区inc设置在子管芯100b1的靠近包封层106的边缘es2 且例如是远离管芯102的一侧(例如,第二侧)。在一些实施例中,子管芯 100b1的上述第一侧和第二侧沿彼此相交(例如,彼此垂直)的方向延伸。在一些实施例中,子管芯100b1包括彼此大致平行的沿方向d1延伸的相对侧边cs1和cs3,以及彼此大致平行的沿方向d2延伸的相对侧边cs2和 cs4。也就是说,侧边cs1和cs3大致垂直于侧边cs2和cs4。在一些实施例中,子管芯100b1的侧边cs1面对主管芯100a的侧边s1a,侧边cs2 朝向或面对包封层106的大致沿方向d2延伸的边缘es2,侧边cs3朝向或面对包封层106的大致垂直于边缘es2的另一大致沿方向d1延伸的边缘,侧边cs4面对管芯102。子管芯100b1的内部连接区inc设置于靠近侧边 cs1的一侧,且例如是沿方向d1延伸;外部连接区exc设置于靠近侧边cs2 的一侧,且例如是沿方向d2延伸;也就是说,内部连接区inc和外部连接区exc沿彼此大致垂直的方向延伸(即,两者的延伸方向之间的夹角大致呈 90度),且设置在子管芯100b1的延伸方向彼此大致垂直的两侧。

66.在一些实施例中,内部连接区inc和外部连接区exc中包括导电走线和连接件。举

例来说,连接件113b包括设置于内部连接区inc中的连接件113b1 和设置于外部连接区exc中的连接件113b2。参照图3a,内部连接区inc中的连接件113b1通过连接件107以及中介板120中的互联区cr1中的导电走线125连接到主管芯100a(例如,连接到主管芯100a的连接件113a);外部连接区exc通过连接件107、中介板120中的一些导电走线125(例如,位于互联区cr1以外的导电走线)、连接件128以及封装基板130连接到导电连接件150,且可进一步通过导电连接件150连接到外部构件(例如,pcb 板等其他封装件或电子器件等)。

67.在一些实施例中,如图2b所示,内部连接区inc在方向d1上的尺寸 (例如,长度)大于其在方向d2上的尺寸(例如,宽度),但本公开并不以此为限;在替代实施例中,内部连接区inc在方向d1上的尺寸(例如,长度或宽度)也可大致等于或小于其在方向d2上的尺寸(例如,长度或宽度);多个连接件113b1可在内部连接区inc中沿方向d1排列成一或多行、沿方向d2排列成一或多列、或者沿方向d1和方向d2排列成包括多行和多列的阵列;在一些实施例中,多个连接件113b1可具有大致相同的尺寸(例如,直径或宽度),且彼此间隔开大致相同的间距,例如,相邻的连接件113b1在方向d1或方向d2上以节距(pitch)p1排列。在本文中,节距是指从元件的中心到另一紧邻的元件的中心之间的距离,或者等于元件的直径加上彼此紧邻的元件之间的间距。另外,不同连接件113b1之间的节距可相同或不同,即,在内部连接区inc中的多个连接件可以固定节距排列,也可以不同节距排列。举例来说,在节距不同的情况下,内部连接区inc中可包括多个子区域,且多个子区域中连接件之间的节距可彼此不同,且此处节距p1可表示内部连接区inc中多个连接件的最小节距或平均节距。

68.在一些实施例中,如图2b所示,外部连接区exc在方向d2上的尺寸 (例如,长度)大于在方向d1上的尺寸(例如,宽度),但本公开并不以此为限;在替代实施例中,外部连接区exc在方向d2上的尺寸(例如,长度或宽度)也可大致等于或小于其在方向d2上的尺寸(例如,长度或宽度);多个连接件113b2可在外部连接区exc中沿方向d2排列成一或多列、沿方向d1排列成一或多行、或者沿方向d1和方向d2排列成包括多行和多列的阵列;在一些实施例中,多个连接件113b2可具有大致相同的尺寸(例如,直径或宽度),且彼此间隔开大致相同的间距,例如,相邻的连接件113b2在方向d2或方向d1上以节距(pitch)p2排列。另外,不同连接件113b2之间的节距可相同或不同,即,在外部连接区exc中的多个连接件可以固定节距排列,也可以不同节距排列。举例来说,在节距不同的情况下,外部连接区exc中可包括多个子区域,且多个子区域中连接件之间的节距可彼此不同,且此处节距p2可表示外部连接区exc中多个连接件的最小节距或平均节距。

69.在一些实施例中,子管芯100b1与主管芯100a之间的连接是并行连接 (parallel connection),且用于进行内部连接的连接件113b1例如是用于传输子管芯与主管芯之间的相对较低频率的电信号;而子管芯100b1与外部构件之间的连接可为串行连接(serial connection),且例如是包括在高速串行电路 (high speed serial circuit)中,用于进行外部连接的连接件113b2例如是用于与外部构件基于pci-express(pcie)(例如,根据串行器/解串化器 (serializer-deserializer,serdes)协议)进行通信的高速模拟输入输出(highspeed analog i/o)接口,连接件113b2用于传输相对少量的电信号。在一些实施例中,连接件113b2之间的节距p2大于或等于连接件113b1之间的节距p1。此处“连接件113b2之间的节距p2大于或等于连接件113b1之间的节距p1”,包括多个连接件113b2的最小节距大于或等于多个连接件113b1 的最小节距,也可包括多个连接件113b2的平均节距大于多

个连接件113b1 的平均节距。另外,多个连接件113b2中某两个相邻连接件113b2之间的节距可大于、等于或小于多个连接件113b1中某两个相邻连接件113b1之间的节距。

70.参照图2c,在一些实施例中,子管芯100b2的结构与子管芯100b1的结构大致类似,不同之处在于基于两者处在不同位置(例如,两者相对于管芯102和103的方位不同),从而外部连接区的位置稍有不同,例如,子管芯100b1的外部连接区exc设置在图中较靠左的位置处,而子管芯100b2的外部连接区exc设置在图中较靠右的位置处且靠近包封层106的边缘es2。在一些实施例中,子管芯100b1和子管芯100b2的结构对称,例如是相对于沿方向d2延伸穿过主管芯100a中心的线对称,但本公开并不以此为限。应理解,子管芯100b2和周边构件(例如,主管芯100a、管芯103、包封层106) 之间的相对位置关系与上述子管芯100b1和周边构件之间的相对位置关系类似或大致相同,其他子管芯100b3和100b4的连接区的配置以及其与主管芯 100a的连接关系、与周边构件的相对位置关系也与上述针对子管芯100b1描述的类似,于此不再赘述。一般来说,子管芯的内部连接区设置在靠近主管芯的第一侧,且子管芯的外部连接区设置在靠近包封层的边缘且远离其他管芯的第二侧,且第一侧和第二侧沿大致垂直的方向延伸。

71.图3b和图3c示出根据本公开另一些实施例的封装结构的示意性剖视图。图3b和图3c所示的封装结构500b和500c与前述图3a的封装结构 500a类似,不同之处在于图3b和图3c的封装结构使用其他类型的封装连接构件来替换图3a所示封装结构中的中介板120,而封装结构500b和500c 的其他结构与封装结构500a大致相同,下文将不再赘述。

72.参照图2a和图3b,在一些实施例中,封装结构500b包括设置于封装基板130的子封装结构spg2,其使用连接结构220来作为封装连接构件cp,连接结构220设置在管芯组100和管芯102-105与封装基板130之间,以提供管芯组100内各个管芯之间的电性连接、管芯102-105与管芯组100的主管芯100a的电性连接以及相应管芯与封装基板130之间的电性连接。在一些实施例中,连接结构220包括桥接管芯(bridge die)201以及多个导电构件203和205。在一些实施例中,桥接管芯201是基于半导体衬底(例如,硅衬底)而形成的管芯,且可包括导电走线201,以提供电性连接。导电走线201、导电构件203和205各自包括金属等导电材料,例如包括钛、铜、金、钨、铝、其类似物、其合金或其组合。在一些实施例中,导电构件203 和205可包括导电通孔、导电走线或其组合。应注意,图3b简要示出的桥接管芯201的结构和导电构件203和205的结构仅为例示说明,且本公开并不以此为限。在一些实施例中,连接结构220还包括介电结构206,介电结构206环绕包覆桥接管芯201以及多个导电构件203和205。介电结构206 可为单层或多层结构,且可包括合适的介电材料,例如可包括氧化硅、氮化硅等无机介电材料;聚酰亚胺、环氧树脂、emc等包括聚合物材料的有机介电材料;或其组合,且本公开并不以此为限。

73.在一些实施例中,桥接管芯201和导电构件203用于各个管芯之间的连接,而导电构件205用于相应管芯与封装基板130之间的连接。桥接管芯 201和导电构件203可设置于图2a所示的各个互联区cr1-cr5内,以将相应管芯连接到彼此;例如,在每个互联区cr1-cr5内设置有内桥接管芯201 和导电构件203,使得相应的管芯可通过连接件107、导电构件203以及桥接管芯201的导电走线202彼此电性连接。如图3b所示,以互联区cr1为例,主管芯100a和子管芯100b1通过连接件107、导电构件203以及桥接管芯201的导电走线202彼此电性连接。在一些实施例中,主管芯100a和子管芯100b1分别与桥接管芯202在垂直于封装基

板130的主表面(例如,顶表面)的方向上彼此交叠(例如,部分交叠),即,主管芯100a和子管芯100b1 的在垂直于封装基板130的主表面的方向上在封装基板130上的正投影分别与桥接管芯201在垂直于封装基板130的主表面的方向上在封装基板130上的正投影彼此重合(例如,部分重合)。

74.在一些实施例中,管芯组100中的各个子管芯100b1-100b4还可通过连接结构和导电基板130连接至外部构件。例如,各个子管芯100b1-100b4的外部连接区中的连接件113b2可通过连接件107、连接结构220的导电构件 205、连接件128以及封装基板130中的导电走线132连接到连接件150,并可进一步通过连接件150耦合至外部构件。

75.参照图2a和图3c,在一些实施例中,封装结构500c包括设置于封装基板130上的子封装结构spg3,其使用再分布结构(redistribution structure) 320作为封装连接构件cp。再分布结构320设置在管芯组100和管芯102

‑ꢀ

105与封装基板130之间,以提供管芯组100内各个管芯之间的电性连接、管芯102-105与管芯组100的主管芯100a之间的电性连接以及相应管芯与封装基板130之间的电性连接。在一些实施例中,再分布结构320包括介电结构306以及一或多个再分布层(redistribution layer)303,介电结构306可包括环氧树脂、聚酰亚胺等合适的聚合物材料,且可为单层或多层结构;一或多个再分布层303嵌置于介电结构306中,且可包括导电线301以及导电通孔302;再分布层303可包括多层导电线301,且位于不同层的导电线301 可通过导电通孔302彼此电性连接;再分布层303包括合适的导电材料,例如包括钛、铜等金属材料。应理解,图3c所示的再分布层303的布置和层数仅为例示说明,且本公开并不以此为限。

76.在一些实施例中,各个管芯通过位于相应互联区cr1-cr5中的再分布层彼此电性连接,且相应管芯通过另一些再分布层而连接到封装基板130。举例来说,如图3c所示,主管芯100a和子管芯100b1、主管芯100a和子管芯100b2分别通过连接件107以及再分布结构320的位于互联区cr1和cr2 中的包括导电线301和导电通孔302的再分布层303的一些部分而电性连接到彼此;子管芯100b1和子管芯100b2分别通过连接件107、再分布结构320 的再分布层303的另一些部分、连接件128以及封装基板130连接到连接件 150,且可进一步通过连接件150与外部构件进行连接。

77.在上述封装结构500a-500c中,在封装基板130上设置有一个子封装结构spg1-spg3,但本公开并不以此为限。在另一些实施例中,多个子封装结构可设置在封装基板130,且多个子封装结构可为相同类型或不同类型的封装结构。

78.图4示出根据本公开另一些实施例的封装结构600的示意性俯视图。图 4所示的封装结构与图2a所示的封装结构类似,不同之处在于图4所示的封装结构包括设置在基板上的多个子封装结构。封装结构600可根据使用不同类型的封装连接构件而实现为封装结构600a-600c(统称为封装结构600)。图5a至图5c分别示出根据本公开一些实施例中的封装结构600a-600c的示意性截面图,且图5a至图5c是沿图4的线b-b’截取的。

79.参照图4,在一些实施例中,封装结构600包括封装基板130、子封装结构spga、子封装结构spgb以及设置于封装基板130上的加固环136。子封装结构spga和spgb可各自采用上述实施例中的子封装结构spg1-spg3 中的任一种。在一些实施例中,子封装结构spga和spgb并排设置在封装基板130上。举例来说,子封装结构spga和spgb沿方向d1排列在封装基板130上。子封装结构spga和spgb中各个管芯的结构特征及连接关系与前述实施例类似,不

同之处在于,在封装结构600中,不同子封装结构中的管芯还通过封装连接构件cp和封装基板130彼此电性连接。子封装结构中管芯组的一些子管芯(即,输入输出管芯)用于不同子封装结构之间的电性连接。例如,子封装结构spga的管芯组100中的子管芯100b2和子封装结构spgb的管芯组100中的子管芯100b1相邻且面向彼此设置,子封装结构spga的管芯组100中的子管芯100b4和子封装结构spgb的管芯组100 中的子管芯100b3相邻且面向彼此设置;子封装结构spga的子管芯100b2 通过封装连接构件cp以及封装基板130与子封装结构spgb的子管芯100b1 电性连接;子封装结构spga的子管芯100b4通过封装连接构件cp以及封装基板130与子封装结构spgb的子管芯100b3电性连接。也就是说,子封装结构spga和spgb的子管芯100b2和100b1以及子管芯100b4和100b3 用于子封装结构spga和spgb之间的电性连接,如箭头ar1所示。在此实施例中,如箭头ar2所示,子封装结构spga和spgb中各自靠近包封层106的边缘且远离另一子封装结构的子管芯100b1和100b3以及子管芯100b2 和100b4用于与封装结构600以外的其他构件进行外部连接,例如用于通过封装连接构件cp和封装基板130连接至封装结构600以外的其他构件。在此实施例中,子封装结构spga和spgb中所包括的管芯的类型、数量等可彼此相同或不同,且本公开并不对此进行限制。

80.图5a示出子封装结构使用中介板120作为封装连接构件cp的实施例。参照图5a,在一些实施例中,封装结构600a包括封装基板130、子封装结构spga1和spgb1、电子组件135、加固环136以及连接件150。子封装结构spga1和spgb1与前述实施例中图3a所示的子封装结构spg1类似。在此实施例中,封装基板130中还包括用于不同子封装结构之间的电性连接的导电走线132’;举例来说,子封装结构spga1和spgb1中管芯组100的相邻设置的子管芯(例如子封装结构spga1中管芯组100的子管芯100b2和子封装结构spgb1中管芯组100的子管芯100b1)通过各自的连接件107、中介板120和连接件128以及封装基板130中的导电走线132’电性连接到彼此。

81.图5b示出子封装结构使用连接结构220作为封装连接构件cp的实施例。参照图5b,在一些实施例中,封装结构600b包括封装基板130、子封装结构spga2和spgb2、电子组件135、加固环136以及连接件150。子封装结构spga2和spga2与前述实施例中图3b所示的子封装结构spg2类似。在此实施例中,子封装结构spga2和spgb2中管芯组100的相邻设置的子管芯(例如子封装结构spga2中管芯组100的子管芯100b2和子封装结构spgb2中管芯组100的子管芯100b1)通过各自的连接件107、连接结构220(例如,导电构件205)和连接件128以及封装基板130中的导电走线132’电性连接到彼此。

82.图5c示出子封装结构使用再分布结构320作为封装连接构件cp的实施例。参照图5c,在一些实施例中,封装结构600c包括封装基板130、子封装结构spga3和spgb3、电子组件135、加固环136以及连接件150。子封装结构spga3和spga3与前述实施例中的子封装结构spg3类似。在此实施例中,子封装结构spga3和spgb3中管芯组100的相邻设置的子管芯 (例如子封装结构spga3中管芯组100的子管芯100b2和子封装结构spgb3 中管芯组100的子管芯100b1)通过各自的连接件107、再分布结构320中的再分布层303和连接件128以及封装基板130中的导电走线132’电性连接到彼此。

83.在本公开的各种实施例中,将单个芯片分成单独的主管芯(例如,逻辑管芯)和子管芯(例如,输入输出管芯)且通过封装技术将主管芯和子管芯集成在一起,子管芯提供与主管芯的电性连接以及与外部构件的电性连接,如此可节省芯片制造成本。此外,通过改进

封装连接构件上的各个管芯的排布方式,例如将芯片组中的子管芯以及芯片组以外的其他管芯均在同一方向上设置在主管芯的一侧或相对侧,而在与该同一方向相交或垂直的另一方向上没有管芯设置在主管芯的一侧或相对侧。如此设置可使得主管芯(例如,逻辑管芯)的尺寸最大化,进而可具有更高运算能力,从而可提高装置的性能。此外,子管芯可充当机械填充芯片控制或减小封装结构的翘曲,而且,此种排列方式可优化多个管芯在封装连接构件上管芯区中的面积占有率,减小包封层的占有面积,降低或最小化不同材料的热膨胀系数失配(coefficientof thermal expansion mismatch,cte mismatch),进而也可改善(例如,减小) 封装结构的翘曲。

84.有以下几点需要说明:

85.(1)本公开实施例附图中,只涉及到与本公开实施例涉及到的结构,其他结构可参考通常设计。

86.(2)在不冲突的情况下,本公开同一实施例及不同实施例中的特征可以相互组合。

87.以上,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1